Sumeet Naik

Member since: 3 months

Educational Institution: Not Entered

Country: India

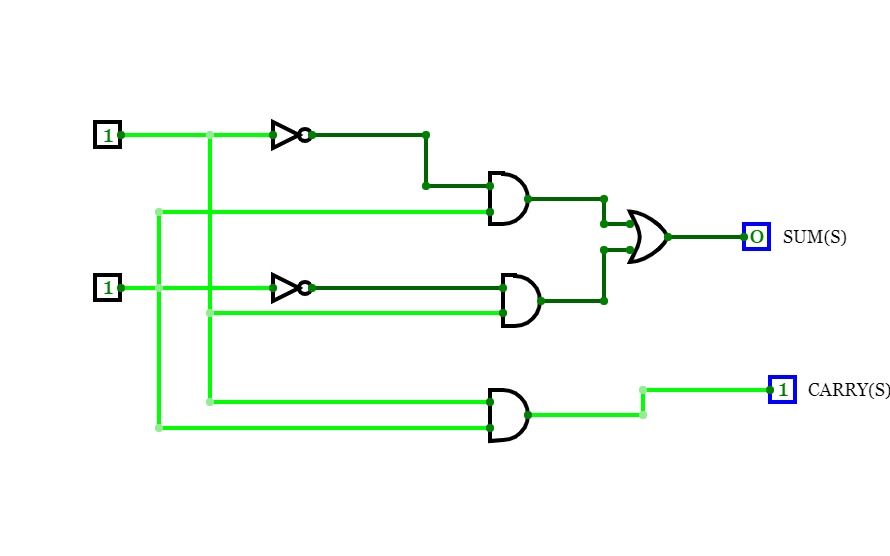

half adder using nand gates

half adder using nand gates

EXP 2 half sub

EXP 2 half sub

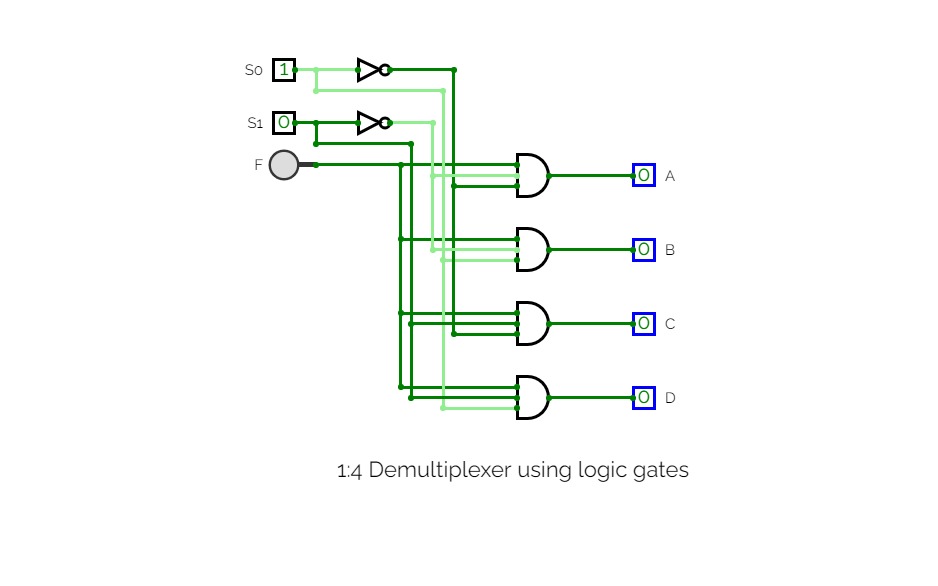

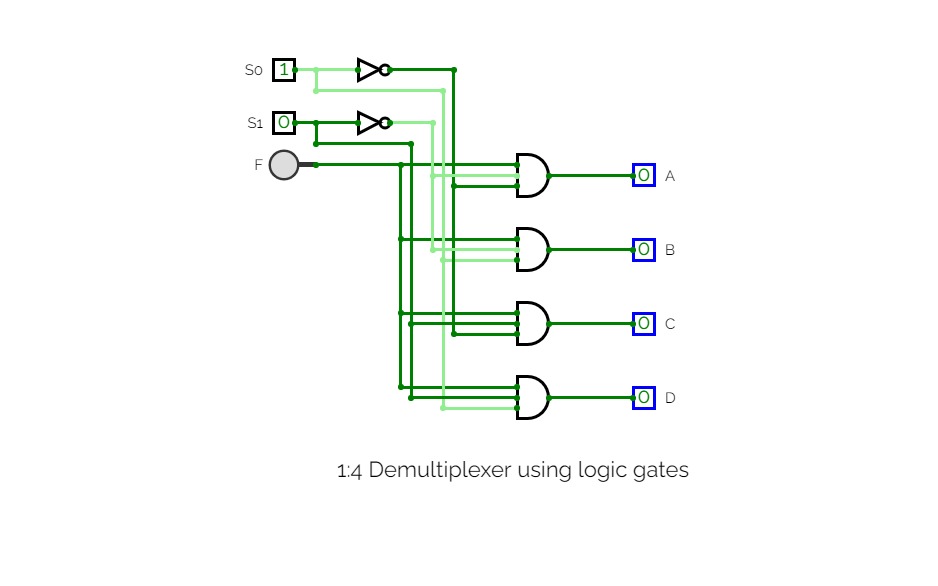

Demultiplexer using logic gates

Demultiplexer using logic gates

1x4 Demultiplexer using NAND gates

1x4 Demultiplexer using NAND gates

Half adder full ader half sub full sub

Half adder full ader half sub full sub

3X8 DECODER

3X8 DECODER

3 Bit Synchronous Up Counter J-K Flip Flops

3 Bit Synchronous Up Counter J-K Flip Flops

3 Bit Synchronous Up Counter J-K Flip Flops

3 Bit Synchronous Up Counter J-K Flip Flops

Untitled

Untitled

EXPERIMENT1FOR EC

EXPERIMENT1FOR EC

experiment 7

experiment 7

exp7 2

exp7 2

HALF ADDER USING BASIC GATES

HALF ADDER USING BASIC GATES

Full Adder using NAND Gate

Full Adder using NAND Gate

sumeet 7

sumeet 7

Demultiplexer using logic gates

Demultiplexer using logic gates

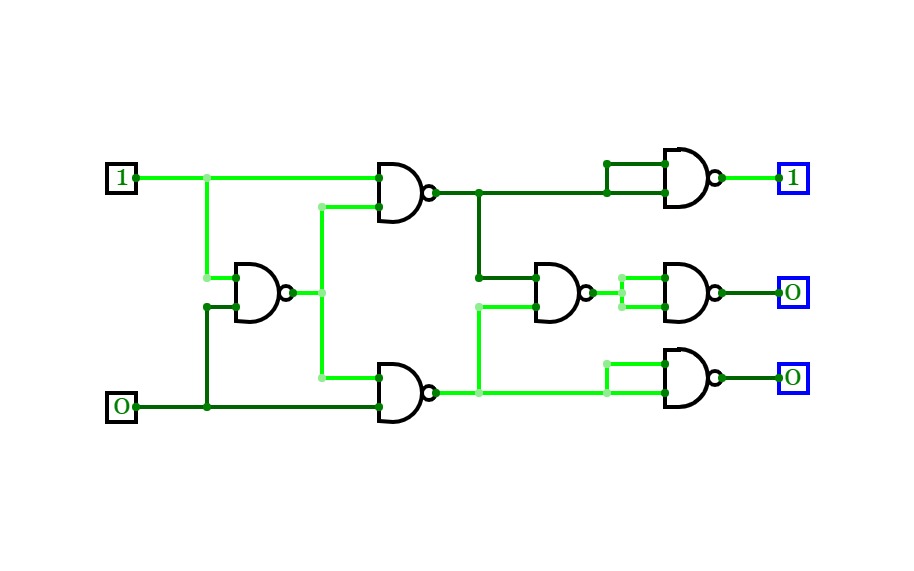

1 bit magnitude comparator using basic gates

1 bit magnitude comparator using basic gates

flip flop 1

flip flop 1

1-BIT COMPARATOR CIRCUIT USING NAND GATE

1-BIT COMPARATOR CIRCUIT USING NAND GATE

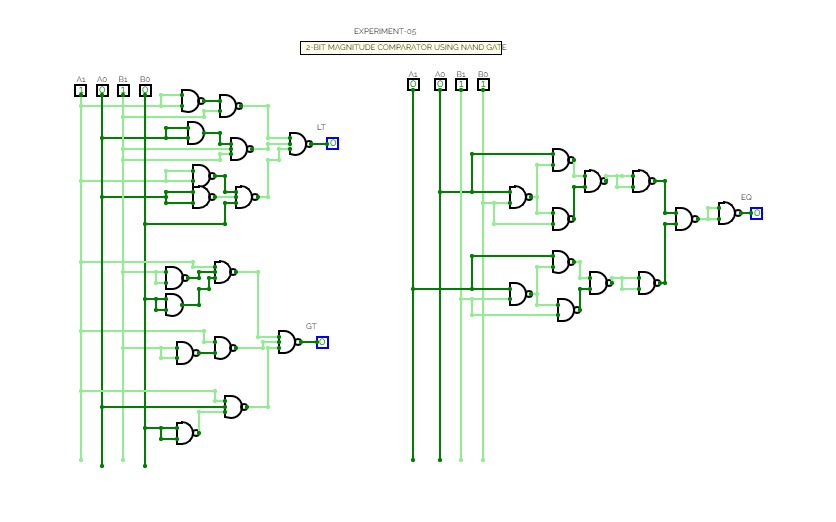

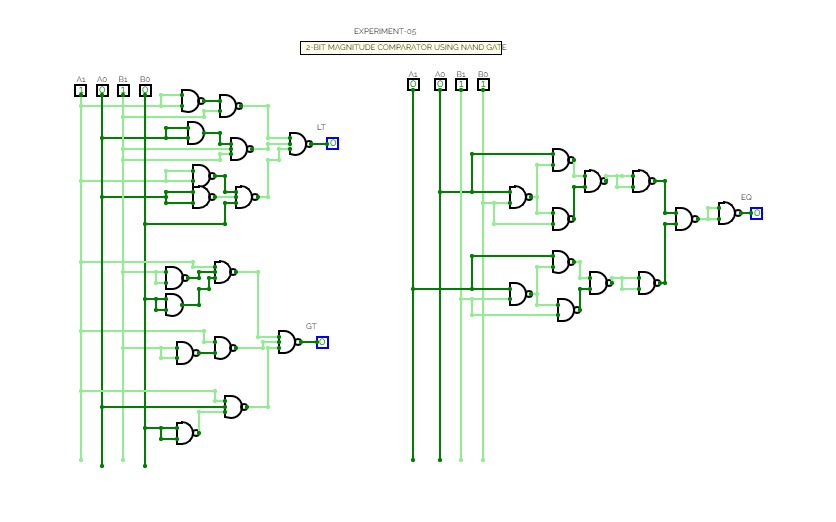

2-BIT MAGNITUDE COMPARATOR USING NAND GATE

2-BIT MAGNITUDE COMPARATOR USING NAND GATE

filp flop1

filp flop1

EXPERIMENT 5

EXPERIMENT 5

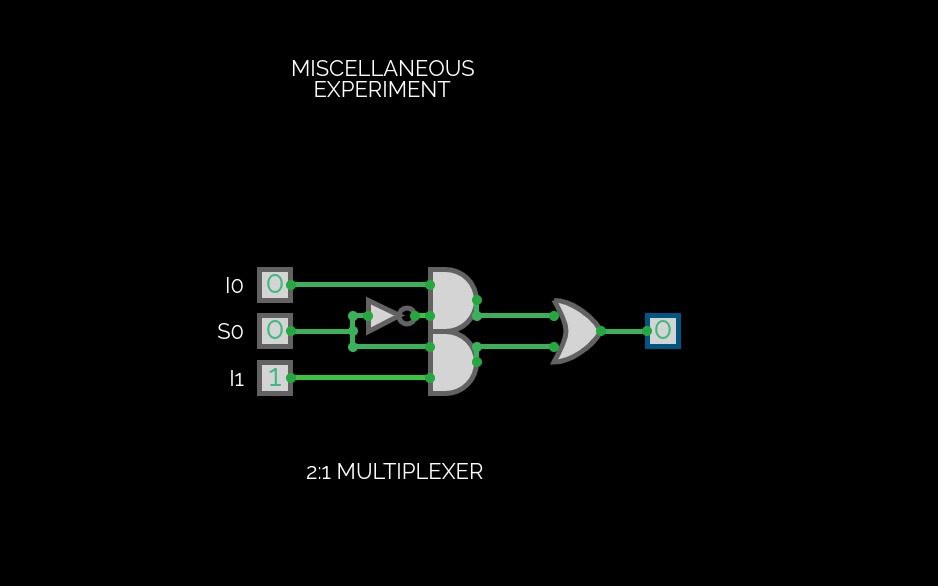

2:1 MULTIPLEXER

2:1 MULTIPLEXER

7 bit ckt

7 bit ckt

jk flip flop using nand gate

jk flip flop using nand gate

Full Adder using NAND Gate

Full Adder using NAND Gate

1 bit magnitude comparator using basic gates

1 bit magnitude comparator using basic gates

1-BIT COMPARATOR CIRCUIT USING NAND GATE

1-BIT COMPARATOR CIRCUIT USING NAND GATE

2-BIT MAGNITUDE COMPARATOR USING NAND GATE

2-BIT MAGNITUDE COMPARATOR USING NAND GATE

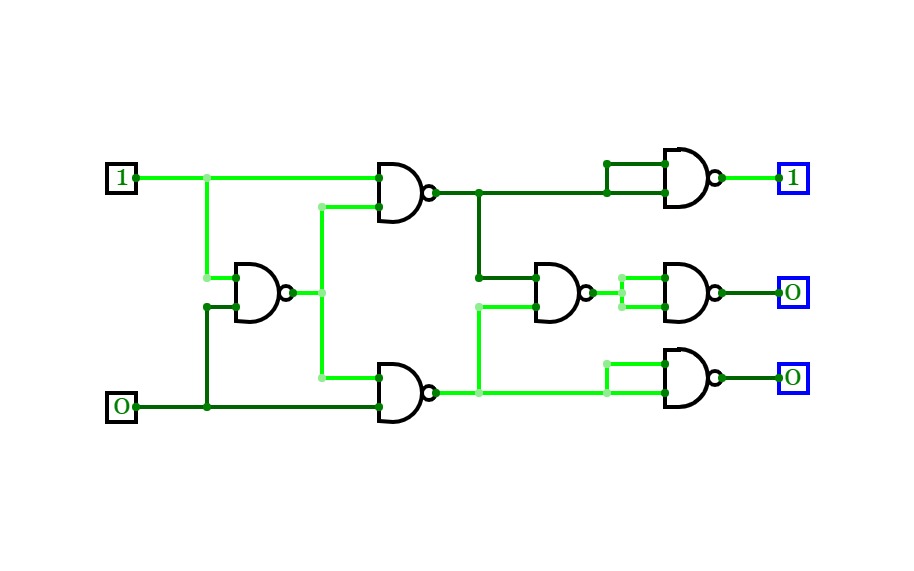

3X8 DECODER

3X8 DECODER

jk flip flop using nand gate

jk flip flop using nand gate

3 Bit Synchronous Up Counter J-K Flip Flops

3 Bit Synchronous Up Counter J-K Flip Flops

3 Bit Synchronous Up Counter J-K Flip Flops

3 Bit Synchronous Up Counter J-K Flip Flops

PROJECT 2.00

PROJECT 2.00