JOSE MARIA RUIZ

Member since: 10 months

Educational Institution: UNER

Country: Argentina

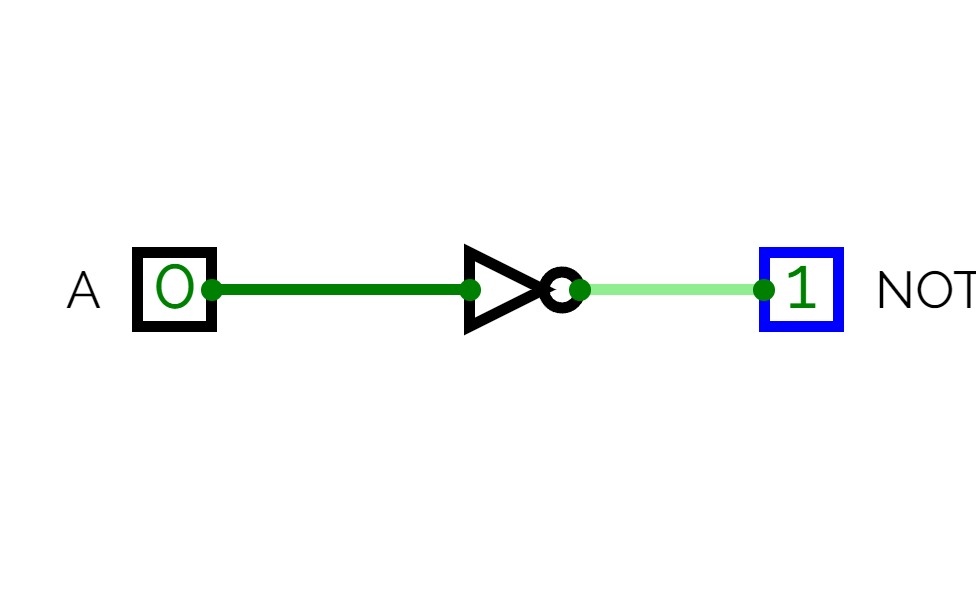

Puertas lógica NOT

Puertas lógica NOT

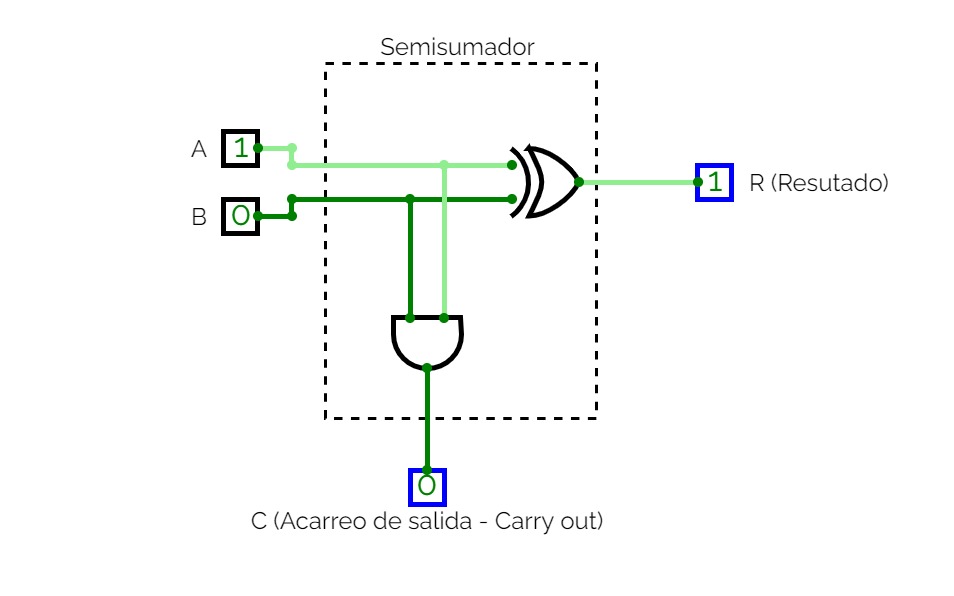

Orga - Semisumador

Orga - Semisumador

Semisumador - Circuitos combinacionales

Semisumador - Circuitos combinacionales

8. Carga inmediata (LDI) - Sim-AC-Harvard

8. Carga inmediata (LDI) - Sim-AC-Harvard

Sim-AC-Neumann

Sim-AC-Neumann

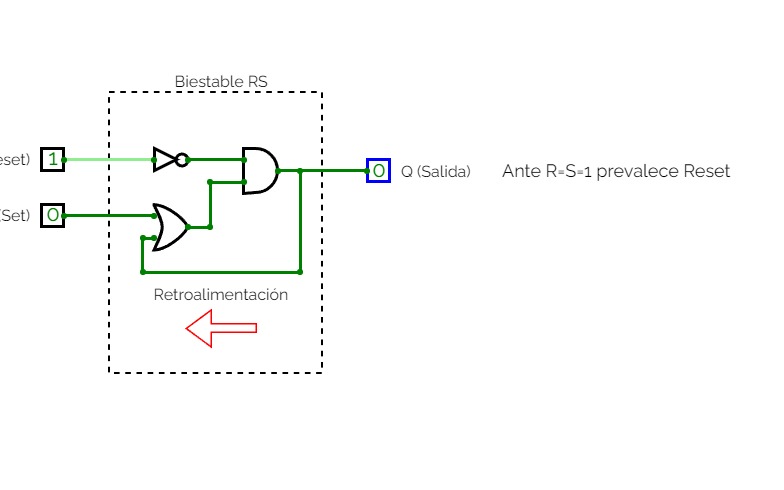

Biestable RS - Circuitos secuenciales

Biestable RS - Circuitos secuenciales

Retroalimentación

Retroalimentación

ALU 4 bits

ALU 4 bits

3. Registro Program Counter (PC) - Sim-AC-Harvard

3. Registro Program Counter (PC) - Sim-AC-Harvard

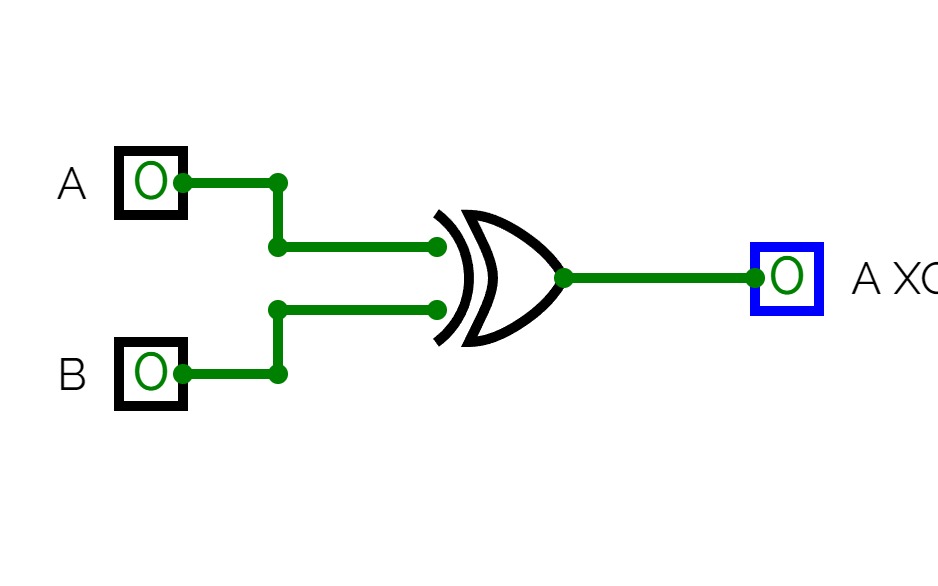

Puerta lógica XOR

Puerta lógica XOR

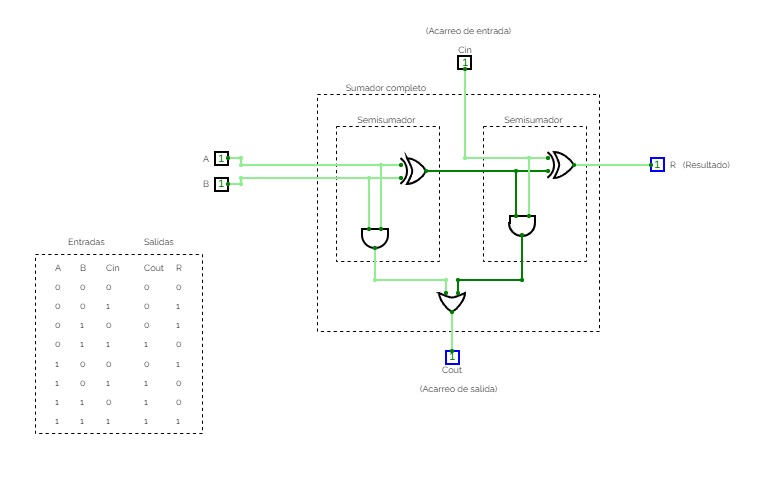

Sumador completo - Circuitos combinacionales

Sumador completo - Circuitos combinacionales

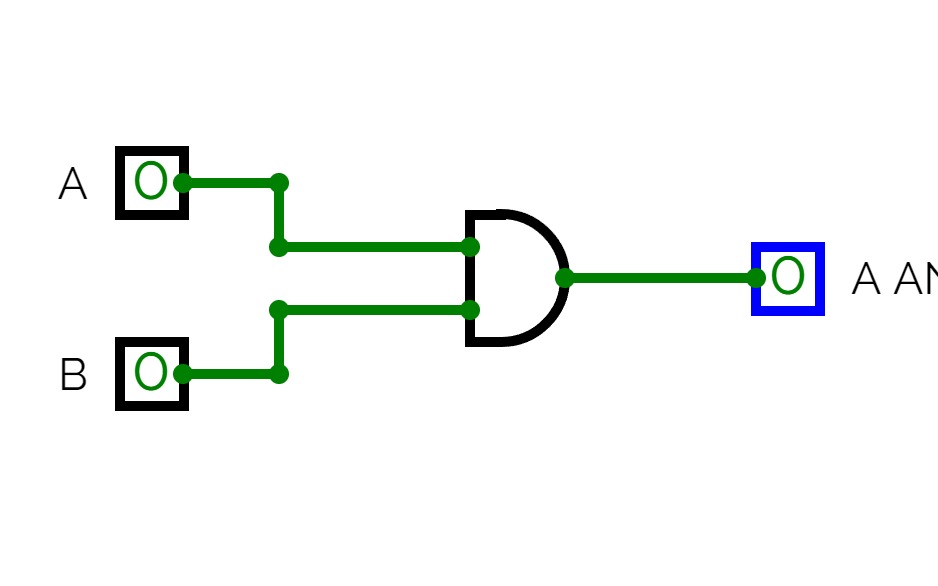

Puerta lógica AND

Puerta lógica AND

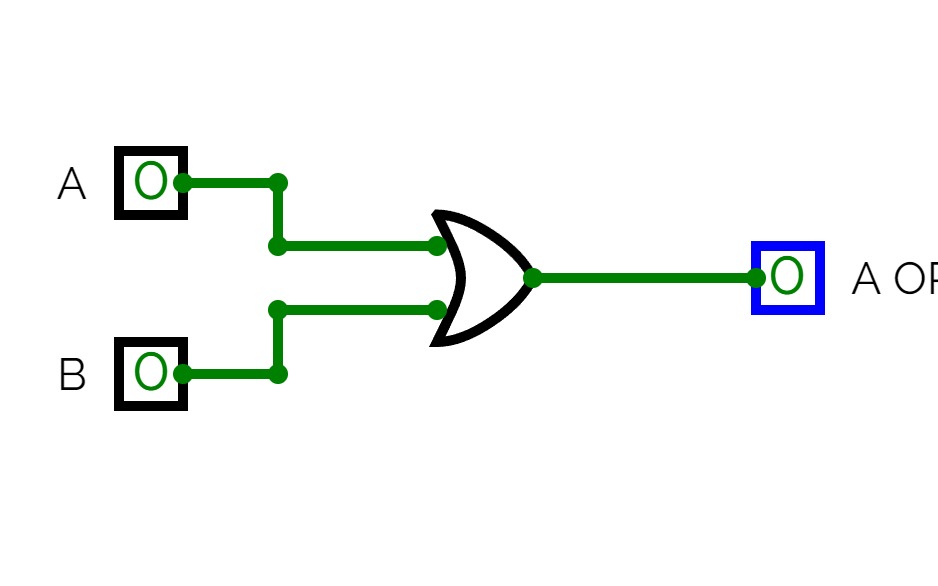

Puerta lógica OR

Puerta lógica OR

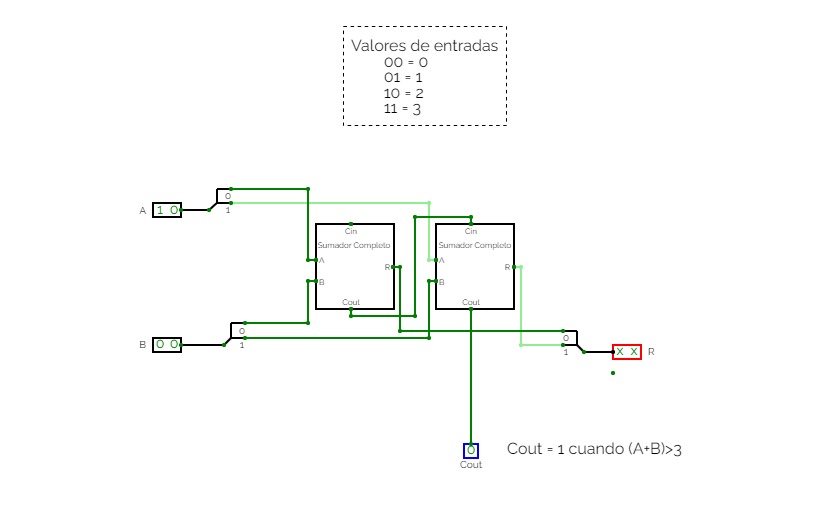

Sumador 2 bits - Circuitos combinacionales

Sumador 2 bits - Circuitos combinacionales

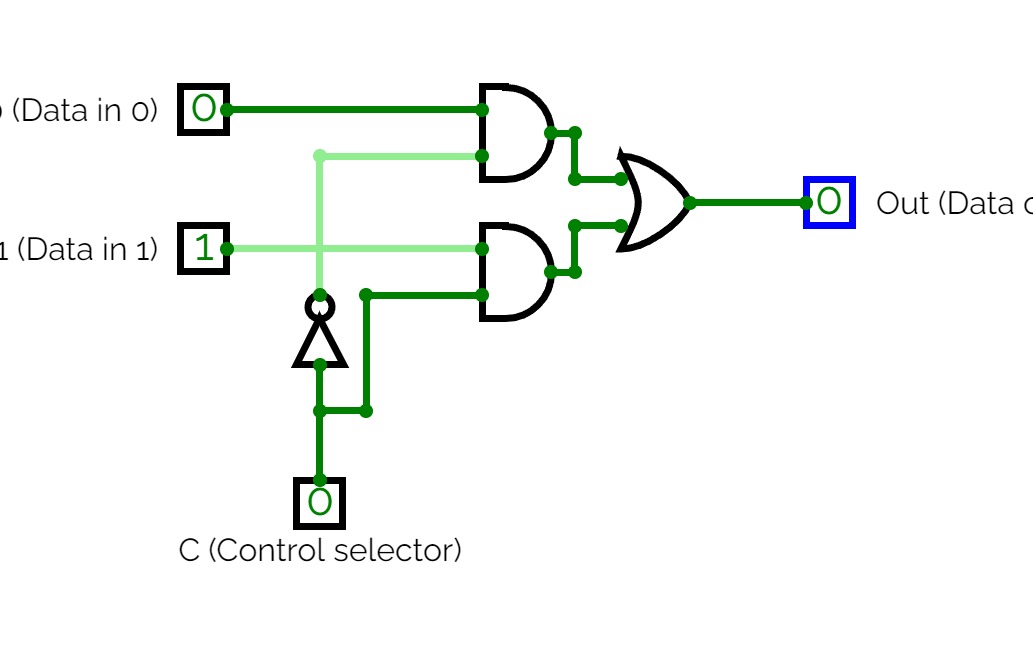

Multiplexor - Circuitos combinacionales

Multiplexor - Circuitos combinacionales

Sumador-restador 2 bits Mux - Circuitos combinacionales

Sumador-restador 2 bits Mux - Circuitos combinacionales

6. Saltos condicionales (JZ-JC) - Sim-AC-Harvard

6. Saltos condicionales (JZ-JC) - Sim-AC-Harvard

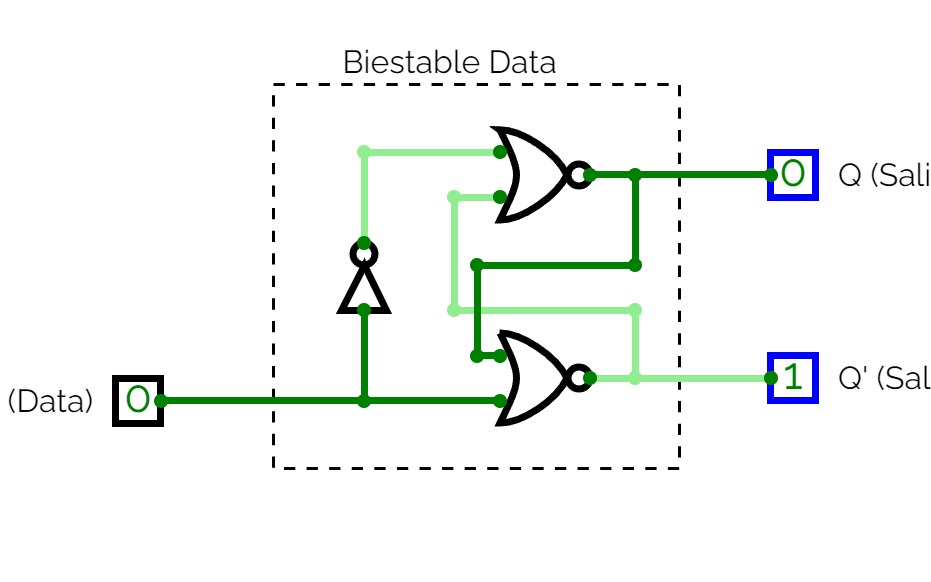

Biestable Data - Circuitos secuenciales

Biestable Data - Circuitos secuenciales

Biestable D activado por flanco de subida - Circuitos secuenciales

Biestable D activado por flanco de subida - Circuitos secuenciales

7. Detiene CPU (HLT) - Sim-AC-Harvard

7. Detiene CPU (HLT) - Sim-AC-Harvard

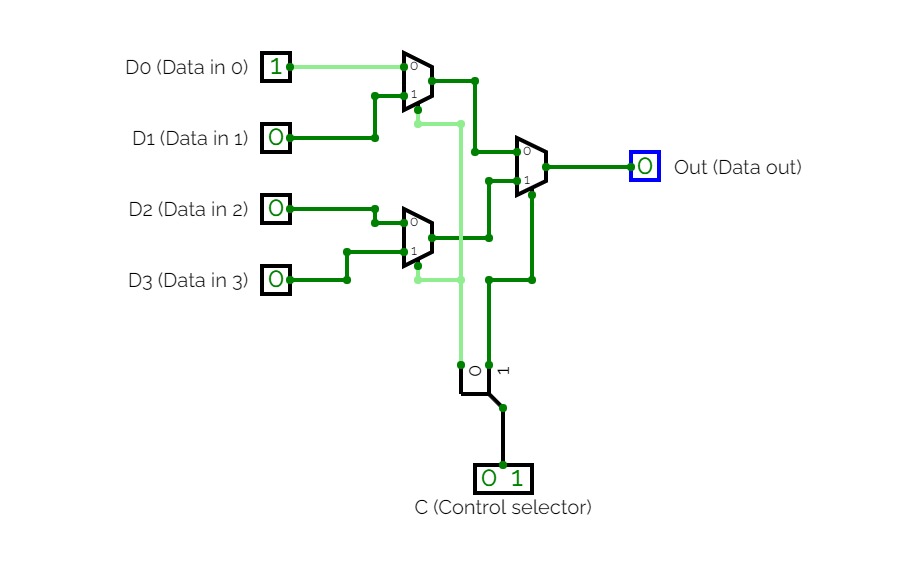

Multiplexor 4 entradas - Circuitos combinacionales

Multiplexor 4 entradas - Circuitos combinacionales

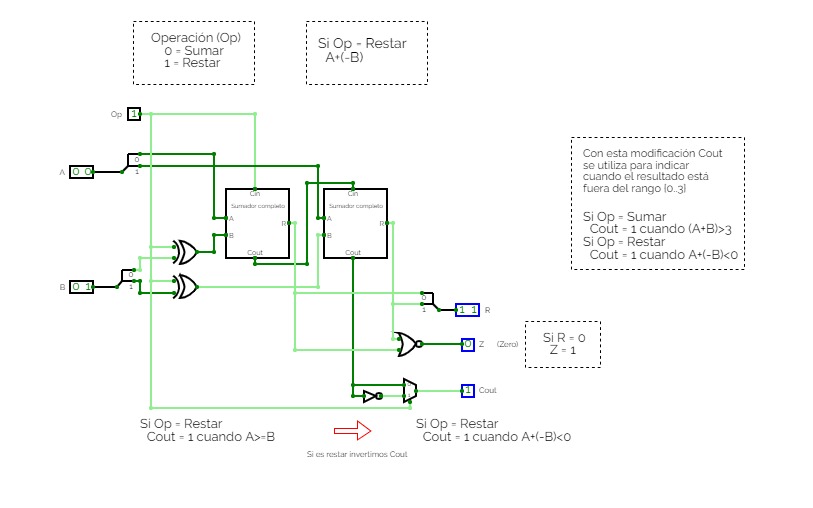

Sumador-restador 2 bits - Circuitos combinacionales

Sumador-restador 2 bits - Circuitos combinacionales

Decodificador - Circuitos combinacionales

Decodificador - Circuitos combinacionales

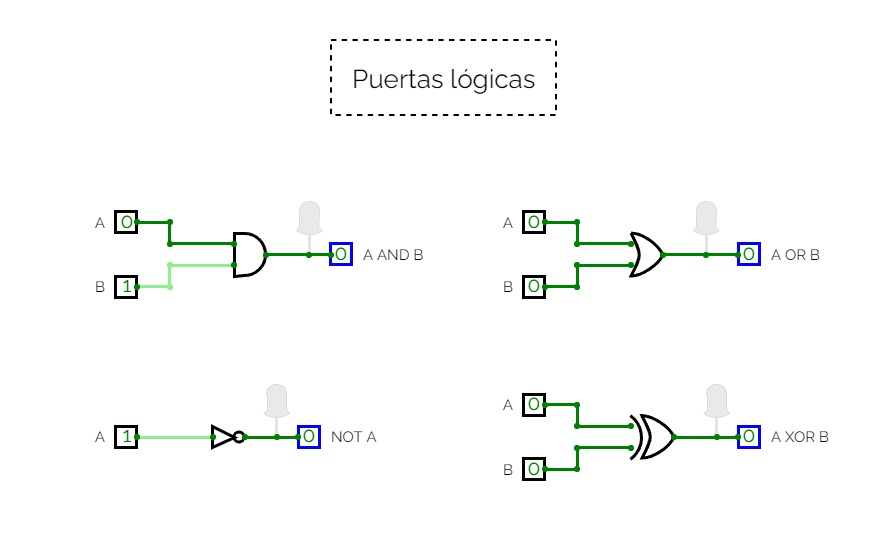

Orga - Puertas logicas

Orga - Puertas logicas

Biestable D con habilitación (Enable) - Circuitos secuenciales

Biestable D con habilitación (Enable) - Circuitos secuenciales

Orga - Semirestador

Orga - Semirestador

Flag Zero - Circuitos combinacionales

Flag Zero - Circuitos combinacionales

Multiplicador 2 bits - Circuitos combinacionales

Multiplicador 2 bits - Circuitos combinacionales

4. Almacenar en memoria (STA) - Sim-AC-Harvard

4. Almacenar en memoria (STA) - Sim-AC-Harvard

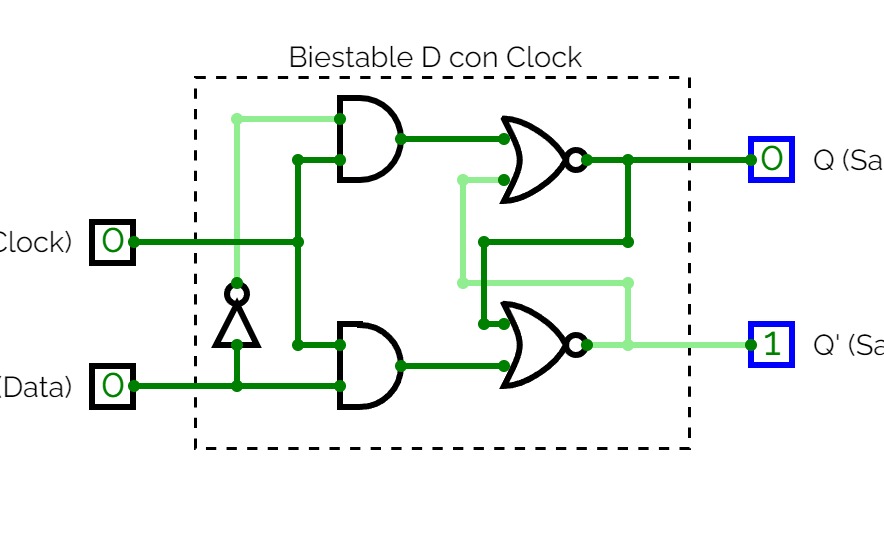

Biestable D con Clock - Circuitos secuenciales

Biestable D con Clock - Circuitos secuenciales

5. Salto incondiconal (JMP) - Sim-AC-Harvard

5. Salto incondiconal (JMP) - Sim-AC-Harvard

1. ALU (ADD-SUB) - Sim-AC-Harvard

1. ALU (ADD-SUB) - Sim-AC-Harvard

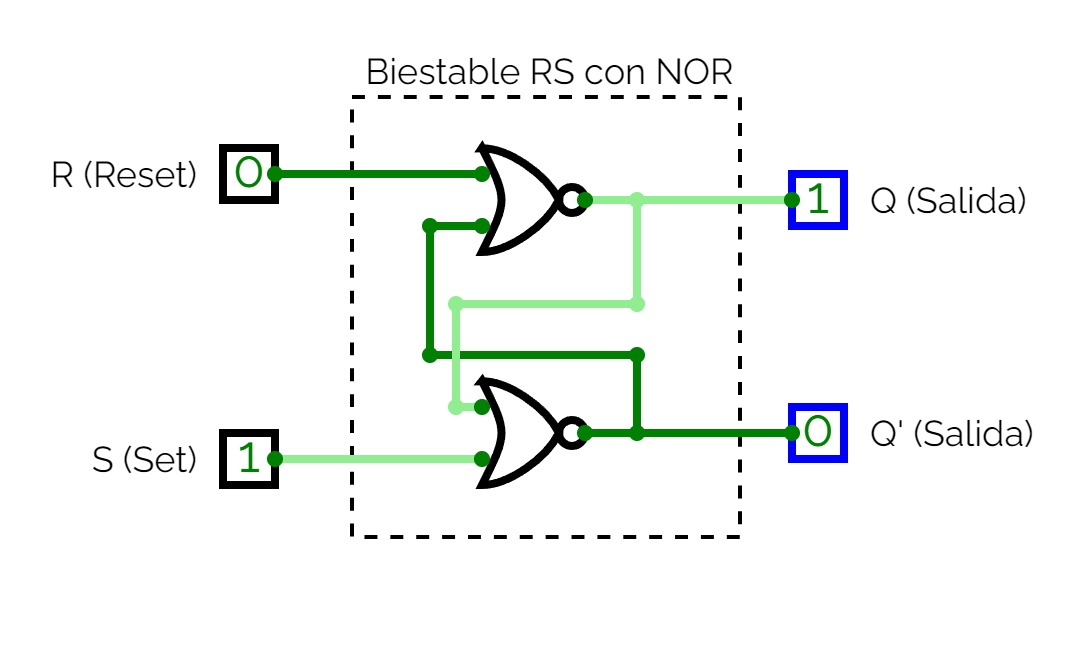

Biestable RS con NOR - Circuitos secuenciales

Biestable RS con NOR - Circuitos secuenciales

2. Cargar de memoria (LDA)- Sim-AC-Harvard

2. Cargar de memoria (LDA)- Sim-AC-Harvard