Mallika Reddy R

Member since: 9 months

Educational Institution: Not Entered

Country: Not Entered

1*2 DeMultiplexer Using Basic And NAND Gate

1*2 DeMultiplexer Using Basic And NAND Gate

2*1 Multiplexer Using Basic And NAND Gates

2*1 Multiplexer Using Basic And NAND Gates

LEVEL-1[2] Exp-4

LEVEL-1[2] Exp-4

DISTRIBUTIVE LAW

DISTRIBUTIVE LAW

IDEMPOTENT LAW

IDEMPOTENT LAW

ANNULMENT LAW

ANNULMENT LAW

IDENTITY LAW

IDENTITY LAW

COMPLEMENT LAW

COMPLEMENT LAW

COMMUTATIVE LAW

COMMUTATIVE LAW

ASSOCIATIVE LAW

ASSOCIATIVE LAW

Associative law

Associative law

SCENARIO-2

SCENARIO-2

SCENARIO-1

SCENARIO-1

ABSORPTION LAW

ABSORPTION LAW

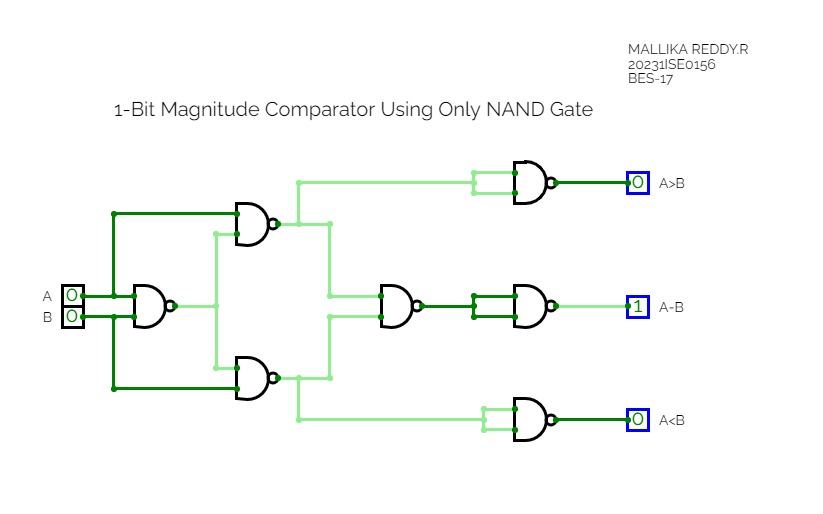

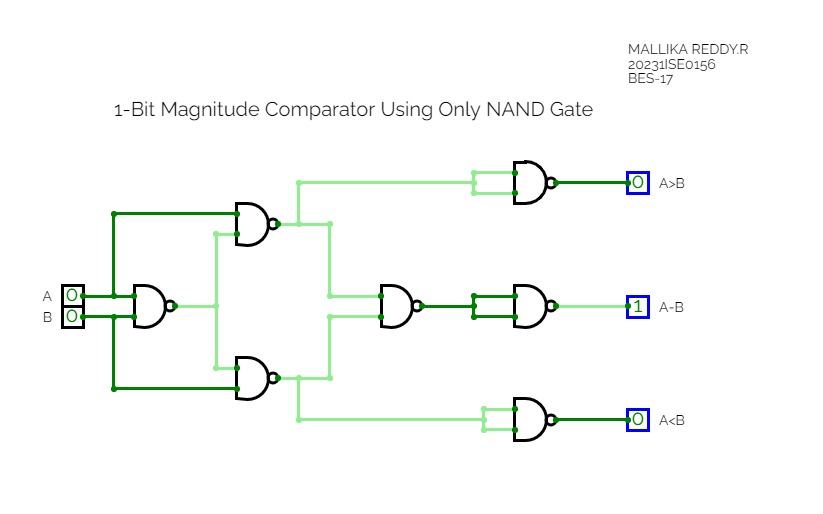

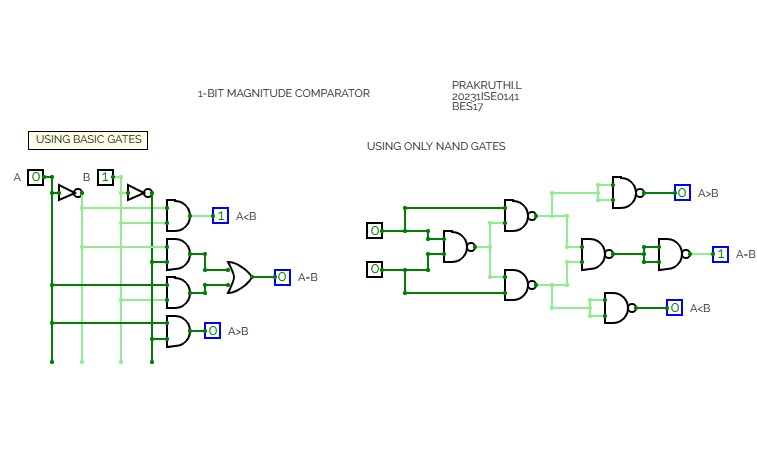

1-Bit Magnitude Comparator Using Only NAND Gate

1-Bit Magnitude Comparator Using Only NAND Gate

Demorgans1

Demorgans1

DE- MORGAN'S2

DE- MORGAN'S2

LEVEL-1 Exp-4

LEVEL-1 Exp-4

LEVEL-1(2) Exp-4

LEVEL-1(2) Exp-4

LEVEL-1 EXP-4

LEVEL-1 EXP-4

Full adder using basic gates

Full adder using basic gates

Full Adder Using NAND Gate

Full Adder Using NAND Gate

Full Subtractor Using NAND Gate

Full Subtractor Using NAND Gate

Full Subtractor Using Basic Gates

Full Subtractor Using Basic Gates

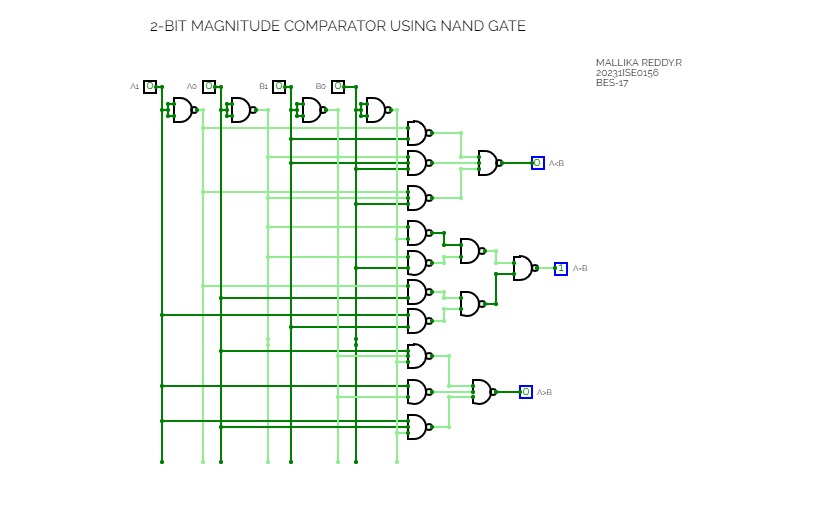

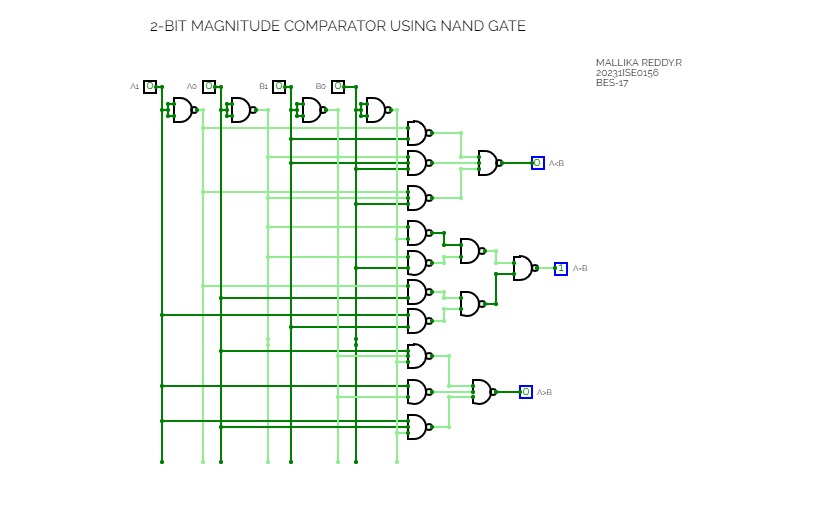

2-BIT MAGNITUDE COMPARATOR USING NAND GATE

2-BIT MAGNITUDE COMPARATOR USING NAND GATE

BASIC GATES USING NOR

BASIC GATES USING NOR

COMPLEMENT LAW

COMPLEMENT LAW

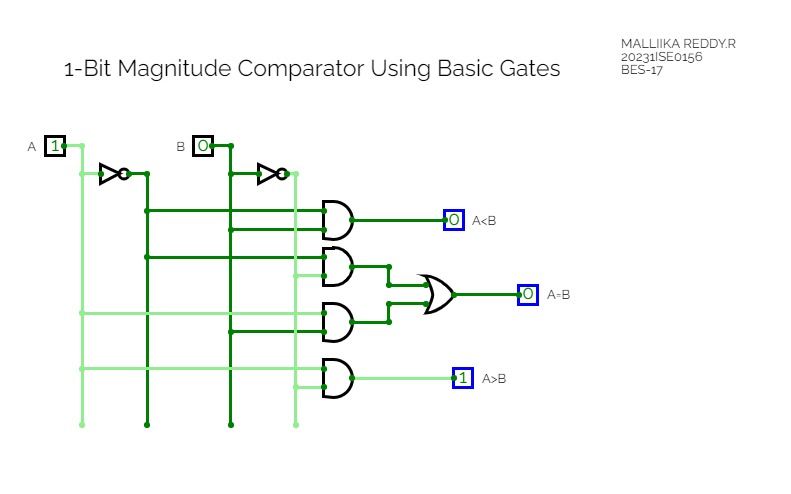

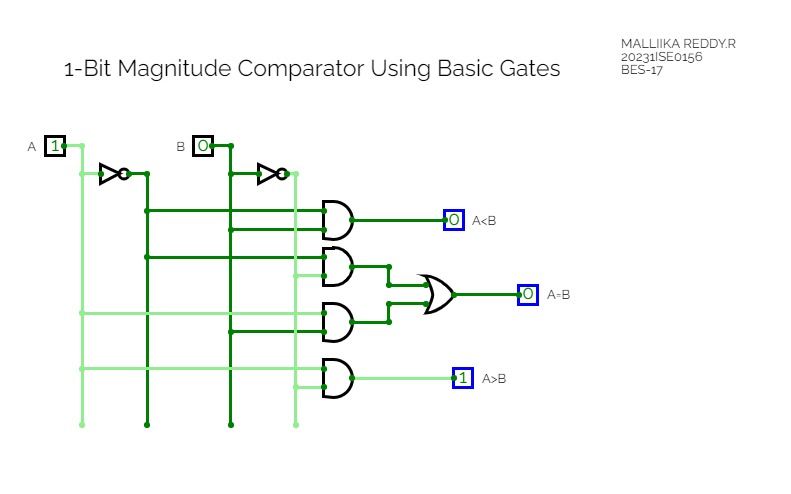

Untitled1-Bit Magnitude Comparator Using Basic Gates

Untitled1-Bit Magnitude Comparator Using Basic Gates

2-Bit Comparator Using Basic Gate

2-Bit Comparator Using Basic Gate

UNIVERSAL GATES

UNIVERSAL GATES

Circuit Diagram of JK FlipFlop

Circuit Diagram of JK FlipFlop

VERIFICATIONOF LOGIC GATE USING 2:1 MUX

VERIFICATIONOF LOGIC GATE USING 2:1 MUX

BASIC GATES

BASIC GATES

SPECIAL GATES

SPECIAL GATES

HALF ADDER

HALF ADDER

BASIC GATES USING NAND

BASIC GATES USING NAND

BASIC GATES USING NOR

BASIC GATES USING NOR

2-BIT USING BASIC GATES

2-BIT USING BASIC GATES

DE MORGANS LAW

DE MORGANS LAW

DISTRIBUTIVE LAW

DISTRIBUTIVE LAW

FULL SUBTRACTOR

FULL SUBTRACTOR

IDENTITY LAW

IDENTITY LAW

1-Bit Magnitude Comparator Using Only NAND Gate

1-Bit Magnitude Comparator Using Only NAND Gate

LEVEL-1 EXP-4

LEVEL-1 EXP-4

ASSOCIATIVE LAW

ASSOCIATIVE LAW

IDEMPOTENT LAW

IDEMPOTENT LAW

DISTRIBUTIVE LAW

DISTRIBUTIVE LAW

ANNULMENT LAW

ANNULMENT LAW

SCENARIO-2

SCENARIO-2

Untitled1-Bit Magnitude Comparator Using Basic Gates

Untitled1-Bit Magnitude Comparator Using Basic Gates

COMPLEMENT LAW

COMPLEMENT LAW

UNIVERSAL GATES

UNIVERSAL GATES

XOR XNOR USING NAND NOR

XOR XNOR USING NAND NOR

COMMUTATIVE LAW

COMMUTATIVE LAW

2 BIT USING NAND

2 BIT USING NAND

1-BIT COMPARATOR

1-BIT COMPARATOR

HALF SUBTRACTOR

HALF SUBTRACTOR

FULL ADDER

FULL ADDER

2 BIT USING BASIC GATES IMP

2 BIT USING BASIC GATES IMP

COMPLEMENT LAW

COMPLEMENT LAW

Associative law

Associative law

ASSOCIATIVE LAW

ASSOCIATIVE LAW

SCENARIO-1

SCENARIO-1

DE- MORGAN'S2

DE- MORGAN'S2

LEVEL-1 Exp-4

LEVEL-1 Exp-4

2-BIT MAGNITUDE COMPARATOR USING NAND GATE

2-BIT MAGNITUDE COMPARATOR USING NAND GATE

ANNULMENT LAW

ANNULMENT LAW

IDEMPOTENT LAW

IDEMPOTENT LAW

IDENTITY LAW

IDENTITY LAW

ABSORPTION LAW

ABSORPTION LAW

LEVEL-1(2) Exp-4

LEVEL-1(2) Exp-4

2-Bit Comparator Using Basic Gate

2-Bit Comparator Using Basic Gate

LEVEL1

LEVEL1

DISTRIBUTIVE LAW

DISTRIBUTIVE LAW

ABSORPTION

ABSORPTION

LEVEL-1[2] Exp-4

LEVEL-1[2] Exp-4

COMMUTATIVE LAW

COMMUTATIVE LAW

Demorgans1

Demorgans1

Full Subtractor Using NAND Gate

Full Subtractor Using NAND Gate

Full Subtractor Using Basic Gates

Full Subtractor Using Basic Gates