keerthan shetty

Member since: 1 year

Educational Institution: PRESIDENCY UNIVERSITY , BANGALORE

Country: India

2-bit magnitude compartors using NAND gates

2-bit magnitude compartors using NAND gates

Experiment 1: derivation of AND,OR,NOT ,NOR,XOR and XNOR using NAND gates

Experiment 1: derivation of AND,OR,NOT ,NOR,XOR and XNOR using NAND gates

Experiment 2:Verification Of Boolean Laws

Experiment 2:Verification Of Boolean Laws

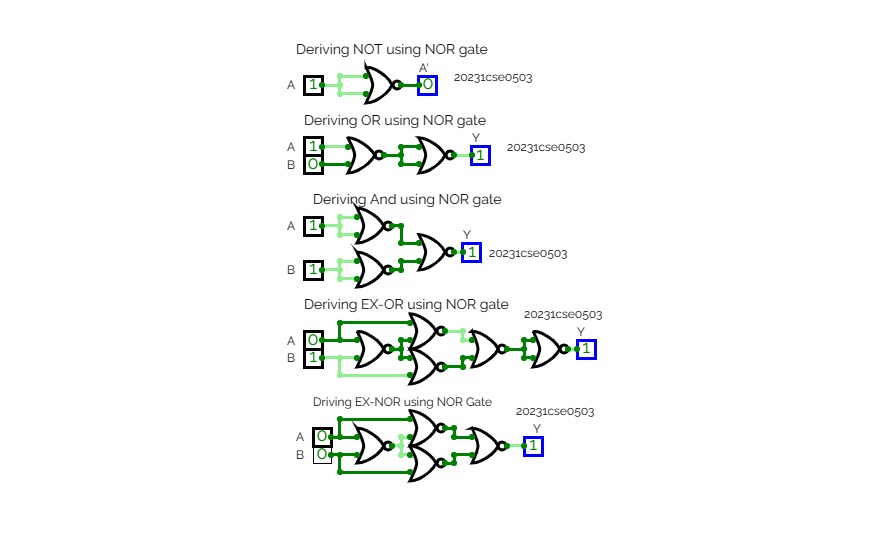

Derivation of NOT,OR,AND,EX-OR , EX-NOR using NOR gate

Derivation of NOT,OR,AND,EX-OR , EX-NOR using NOR gate

Implementing all basic gates using 2:1 mux

Implementing all basic gates using 2:1 mux

Experiment 3:Design of Combinational CirCuits

Experiment 3:Design of Combinational CirCuits

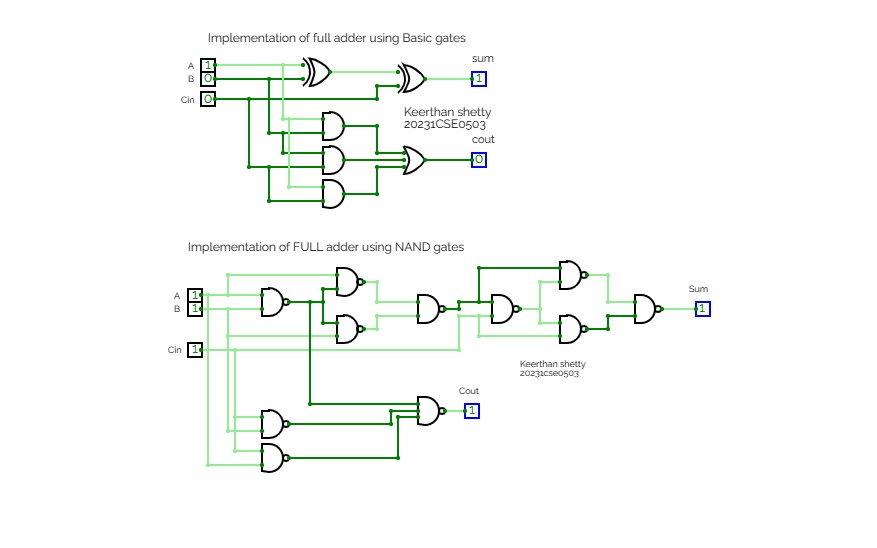

implementation of FULL Adder using basic gates

implementation of FULL Adder using basic gates

Experiment 4:design of adder substracter circuit

Experiment 4:design of adder substracter circuit

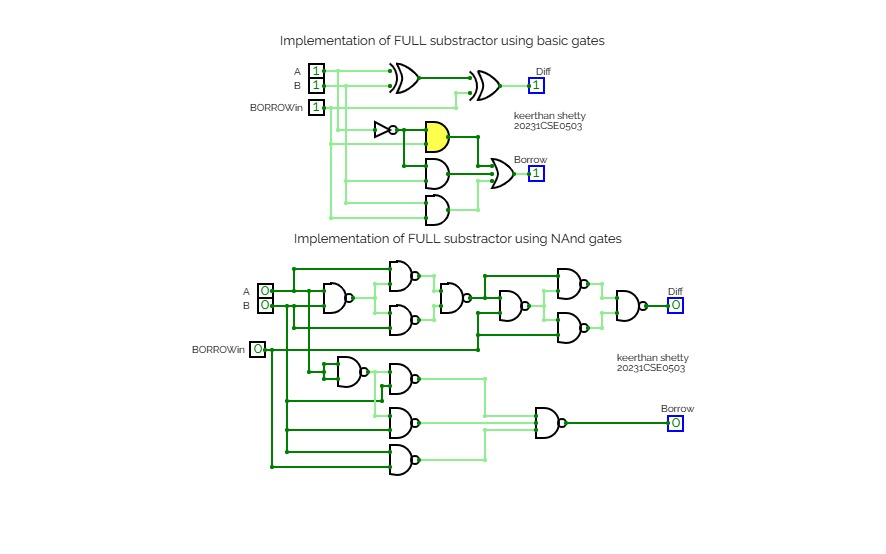

implementation of FULL substractor

implementation of FULL substractor

Implmentation of logic gates

Implmentation of logic gates

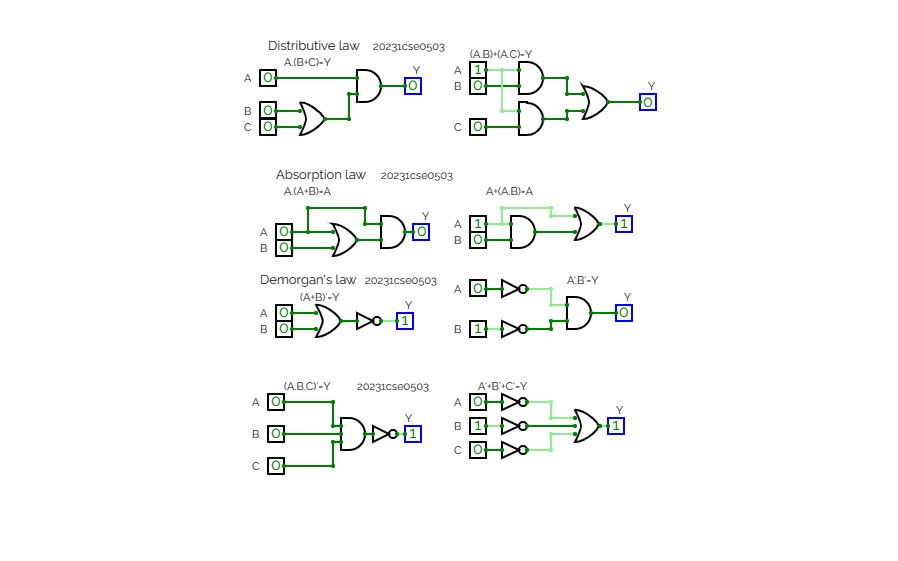

Experiment 2:verification of Distributive , Absoption And Demorgans law

Experiment 2:verification of Distributive , Absoption And Demorgans law

Experiment 4:Design Of Adder And Subtracter circuit

Experiment 4:Design Of Adder And Subtracter circuit

Magnitude Comparators 2-bit using basic gate

Magnitude Comparators 2-bit using basic gate

implementing full adder using 4:1 mux

implementing full adder using 4:1 mux

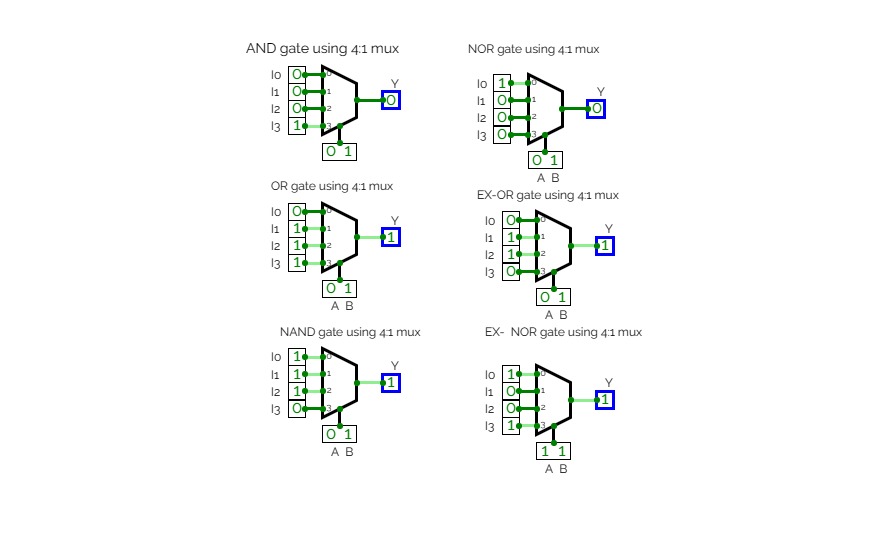

Implementing all basic gates using 4:1 mux

Implementing all basic gates using 4:1 mux

experiment 6: design of multiplexer and de-multiplexer

experiment 6: design of multiplexer and de-multiplexer

1 bit magnitude comparartors using Basic NAND gates

1 bit magnitude comparartors using Basic NAND gates