SRINIVAS KALYAN

Member since: 11 months

Educational Institution: Not Entered

Country: India

NAND & OR gates implementation

NAND & OR gates implementation

LAWS

LAWS

LAWS-2

LAWS-2

HALF SUBTRACTOR

HALF SUBTRACTOR

Half Adder

Half Adder

Full Subtractor Using Basic Gates

Full Subtractor Using Basic Gates

Full Adder Using Only NAND Gates

Full Adder Using Only NAND Gates

Full Adder using Basic gates

Full Adder using Basic gates

Full Subtractor Using Only NAND Gates

Full Subtractor Using Only NAND Gates

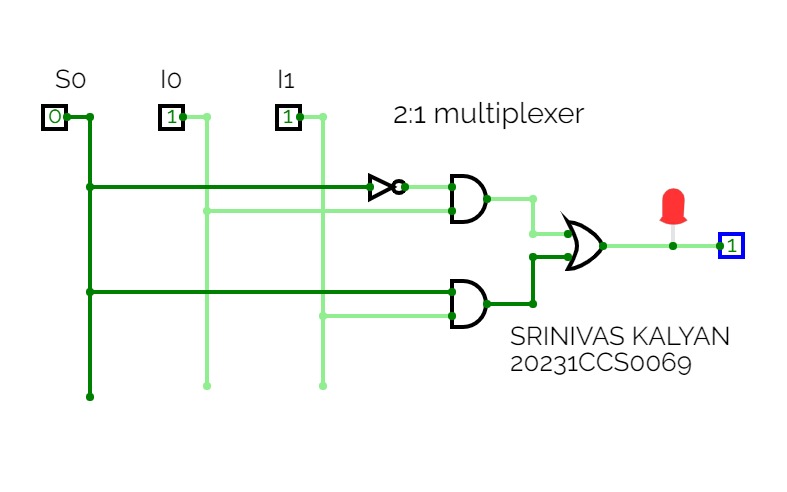

2:1 multiplexer

2:1 multiplexer

4:1 multiplexer

4:1 multiplexer

1:2 Demultiplexer using Basic Gates

1:2 Demultiplexer using Basic Gates

2*4 Decoder Using Basic Gates

2*4 Decoder Using Basic Gates

1:2 Demultiplexer Using Only NAND Gates

1:2 Demultiplexer Using Only NAND Gates

Distributive Law

Distributive Law

Basic Gates

Basic Gates

2-Bit Maganitude Comparator Using NAND Gates

2-Bit Maganitude Comparator Using NAND Gates

2-Bit Magnitude Comparator Using Basic Gates

2-Bit Magnitude Comparator Using Basic Gates

1-Bit Magnitude Comparator Using Basic Gates

1-Bit Magnitude Comparator Using Basic Gates

MULTIPLEXER'S

MULTIPLEXER'S

2:1 Multiplexer using only NAND Gates

2:1 Multiplexer using only NAND Gates

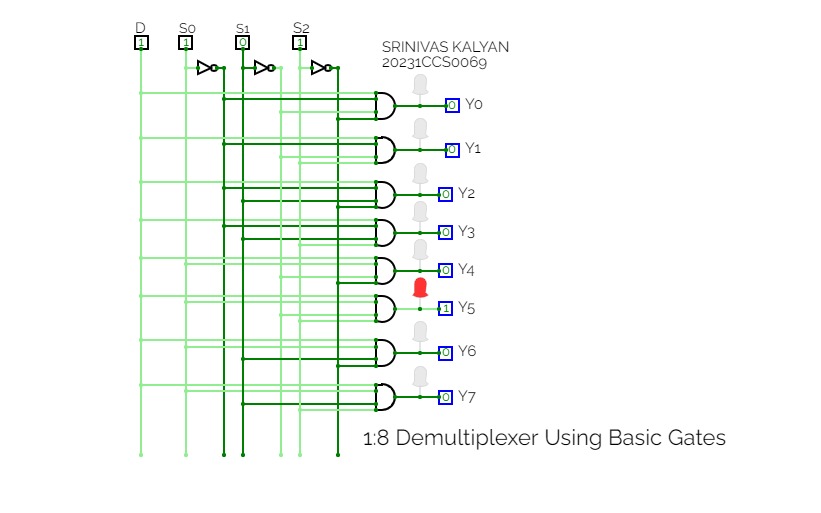

1:8 Demultiplexer Using Basic Gates

1:8 Demultiplexer Using Basic Gates

4*2 Encoder USing Basic Gates

4*2 Encoder USing Basic Gates

8*3 Encoder using Basic Gates

8*3 Encoder using Basic Gates

Implementation of Full Adder Using 4*1 Multiplexer

Implementation of Full Adder Using 4*1 Multiplexer

Implemntation of Gates using 2*1 Multiplexer

Implemntation of Gates using 2*1 Multiplexer

SR FilpFloop

SR FilpFloop

SR FlipFlop Using NAND Gates

SR FlipFlop Using NAND Gates

3-bit Synchronous Counter Using JK Flip Flop

3-bit Synchronous Counter Using JK Flip Flop

JK Filp Flop Using NAND Gate

JK Filp Flop Using NAND Gate

1-bit Magnitude Comparator Using NAND Gates

1-bit Magnitude Comparator Using NAND Gates