ARDRA

Member since: 1 year

Educational Institution: PRESIDENCY UNIVERSITY , BANGALORE

Country: India

2-BIT COMPARATOR USING NAND GATES

2-BIT COMPARATOR USING NAND GATES

SR LATCH FOR NOR GATES

SR LATCH FOR NOR GATES

GATED D-LATCH

GATED D-LATCH

HALF SUBTRACTOR NAND IMPLEMENTATION

HALF SUBTRACTOR NAND IMPLEMENTATION

Implementation of Half Adder using NOR gate

Implementation of Half Adder using NOR gate

1:2 DEMUX USING TWO INPUT NAND GATE

1:2 DEMUX USING TWO INPUT NAND GATE

1-bit comparator and NAND implementation

1-bit comparator and NAND implementation

NAND IMPLEMENTATION INCOMPLETE

NAND IMPLEMENTATION INCOMPLETE

AND GATE USING 2:1 MUX

AND GATE USING 2:1 MUX

EXPERIMENT 2

EXPERIMENT 2

2:1 MUX USING NAND GATES

2:1 MUX USING NAND GATES

2-bit COMPARATOR

2-bit COMPARATOR

1:2 demux using basic gates

1:2 demux using basic gates

ABSORPTION LAW AND DE-MORGAN'S LAW

ABSORPTION LAW AND DE-MORGAN'S LAW

OR GATE USING 2:1 MUX

OR GATE USING 2:1 MUX

NOT GATE USING 2:1 MUX

NOT GATE USING 2:1 MUX

4:1 MUX

4:1 MUX

FULL ADDER USING 4:1 MUX

FULL ADDER USING 4:1 MUX

2:1 MUX

2:1 MUX

IMPLEMENTATION OF BASIC GATES USING 2:1 MUX

IMPLEMENTATION OF BASIC GATES USING 2:1 MUX

SR FLIP FLOP

SR FLIP FLOP

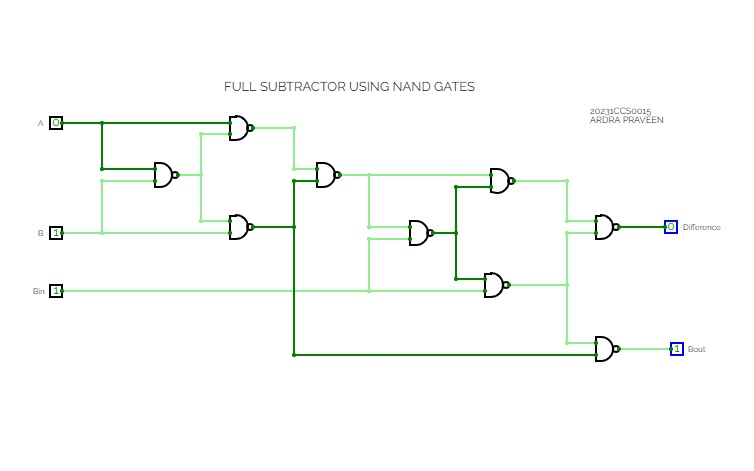

FULL SUBTRACTOR USING NAND GATES

FULL SUBTRACTOR USING NAND GATES