Dilip D

Member since: 11 months

Educational Institution: Not Entered

Country: Not Entered

DILIPD P2

DILIPD P2

Public

DILIP P3

DILIP P3

Public

Untitled

Untitled

Public

MUX USING NAND GATE

MUX USING NAND GATE

Public

DILIP P4

DILIP P4

Public

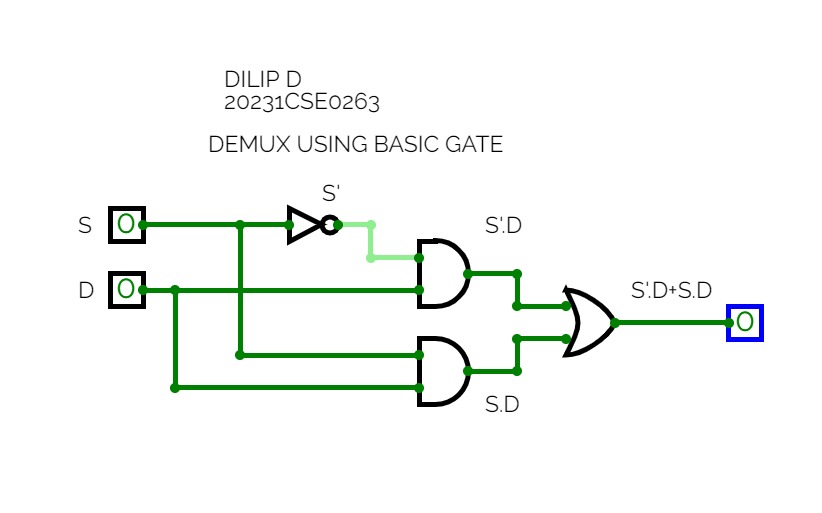

DEMUXPLEXER(1:2)

DEMUXPLEXER(1:2)

Public

DILIP P7

DILIP P7

Public

Untitled

Untitled

Public

1-BIT USING BASIC GATES

1-BIT USING BASIC GATES

Public

MULIPLEXER(2:1)

MULIPLEXER(2:1)

Public

1-BIT COMPARATOR1

1-BIT COMPARATOR1

Public

Untitled

Untitled

Public

DEMUX USING NAND GATE

DEMUX USING NAND GATE

Public

DILIP P5

DILIP P5

Public

DILIP P6

DILIP P6

Public

FULL LADDER USING BASIC GATE

FULL LADDER USING BASIC GATE

Public

FULL LADDER USING BASIC GATES

FULL LADDER USING BASIC GATES

Public

CIRCUITS-8

CIRCUITS-8

Public

CIRCUITS-8

CIRCUITS-8

Public

CIRCUITS-8

CIRCUITS-8

Public

1-BIT USING BASIC GATES

1-BIT USING BASIC GATES

Public

DILIP P3

DILIP P3

Public

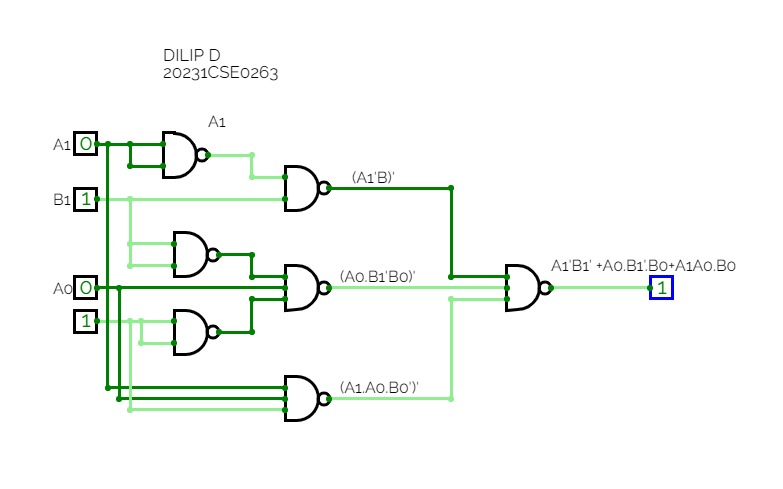

(A>B) 2-BIT USING NAND GATE (A=B)

(A>B) 2-BIT USING NAND GATE (A=B)

Public

MUX USING BASIC GATE

MUX USING BASIC GATE

Public

FULL ADDER CIRCUIT USING 4:1 MUX

FULL ADDER CIRCUIT USING 4:1 MUX

Public

2 BIT MAGNTUDE COMPARATOR USING NAND GATE

2 BIT MAGNTUDE COMPARATOR USING NAND GATE

Public