uma prasad

Member since: 12 months

Educational Institution: Not Entered

Country: Not Entered

LATCH USING NAND

LATCH USING NAND

Public

LATCH USING NOR

LATCH USING NOR

Public

FLIPFLOP USING NAND

FLIPFLOP USING NAND

Public

Q.3)assignment-2

Q.3)assignment-2

Public

ASSIGNMENT-3 Q.6)

ASSIGNMENT-3 Q.6)

Public

Q.2) assignment-2

Q.2) assignment-2

Public

ASSIGNMENT-3 Q.1)

ASSIGNMENT-3 Q.1)

Public

Q.5)HALF SUBTRACTOR

Q.5)HALF SUBTRACTOR

Public

ASSIGNMENT-4

ASSIGNMENT-4

Public

ASSIGNMENT-3

ASSIGNMENT-3

Public

CS

CS

Public

LOGIC GATES

LOGIC GATES

Public

LOGIC GATES

LOGIC GATES

Public

ASSIGNMENT-5

ASSIGNMENT-5

Public

Q.2) LOGIC GATES USING NOR

Q.2) LOGIC GATES USING NOR

Public

SUBTRACTOR

SUBTRACTOR

Public

ADDERS

ADDERS

Public

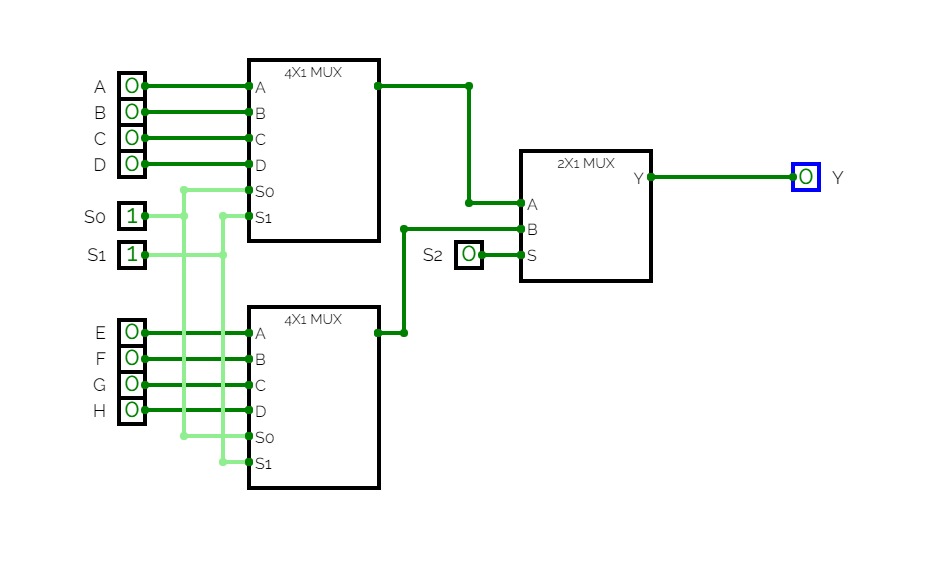

MUX

MUX

Public

Untitled

Untitled

Public

IMPLEMENT USING MUX

IMPLEMENT USING MUX

Public

Q.3)LOGIC GATES USING NAND

Q.3)LOGIC GATES USING NAND

Public

Q.1)LOGIC GATES

Q.1)LOGIC GATES

Public

Q.4)HALF ADDER

Q.4)HALF ADDER

Public

ASSIGNMENT-2

ASSIGNMENT-2

Public

ASSIGNMENT-3 Q.2)

ASSIGNMENT-3 Q.2)

Public

ASSIGNMENT-3 Q.4)

ASSIGNMENT-3 Q.4)

Public

ASSIGNMENT-3 Q.5)

ASSIGNMENT-3 Q.5)

Public

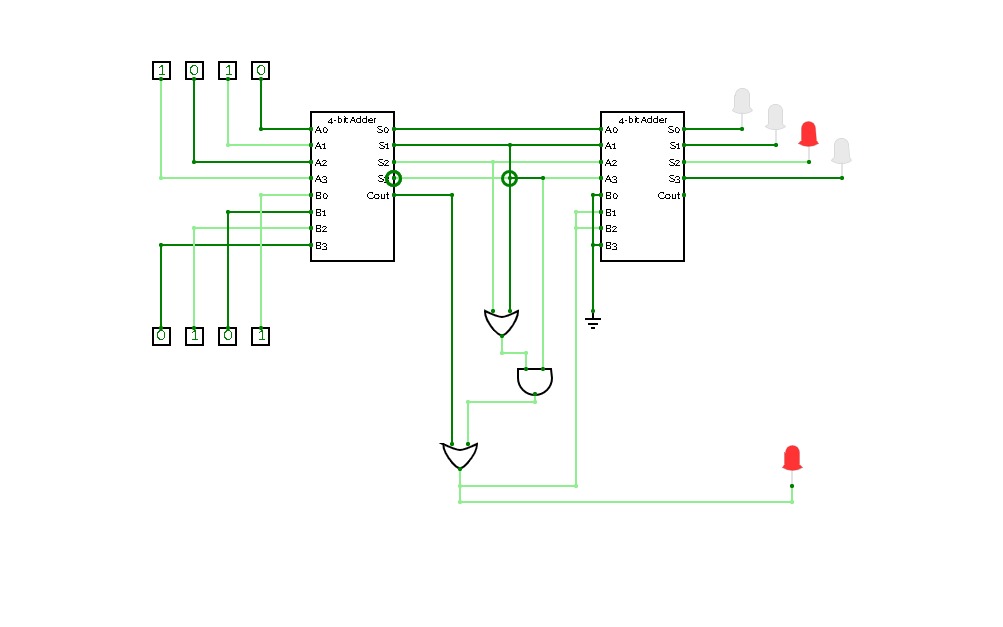

ALU DESIGN

ALU DESIGN

Public

DEC_ASSIGNMENT

DEC_ASSIGNMENT

Public

4-Bit BCD Adder

4-Bit BCD Adder

Public

DEC_ASSIGNMENT-1

DEC_ASSIGNMENT-1

Public

SEQUENTIAL CIRCUIT

SEQUENTIAL CIRCUIT

Public

DEC_ASSIGNMENT-2

DEC_ASSIGNMENT-2

Public

FLIPFLOP USING NOR

FLIPFLOP USING NOR

Public

ECL Lab 5

ECL Lab 5

Public