SHIVANANDA AP"20231CSE3039"

Member since: 5 months

Educational Institution: Not Entered

Country: Not Entered

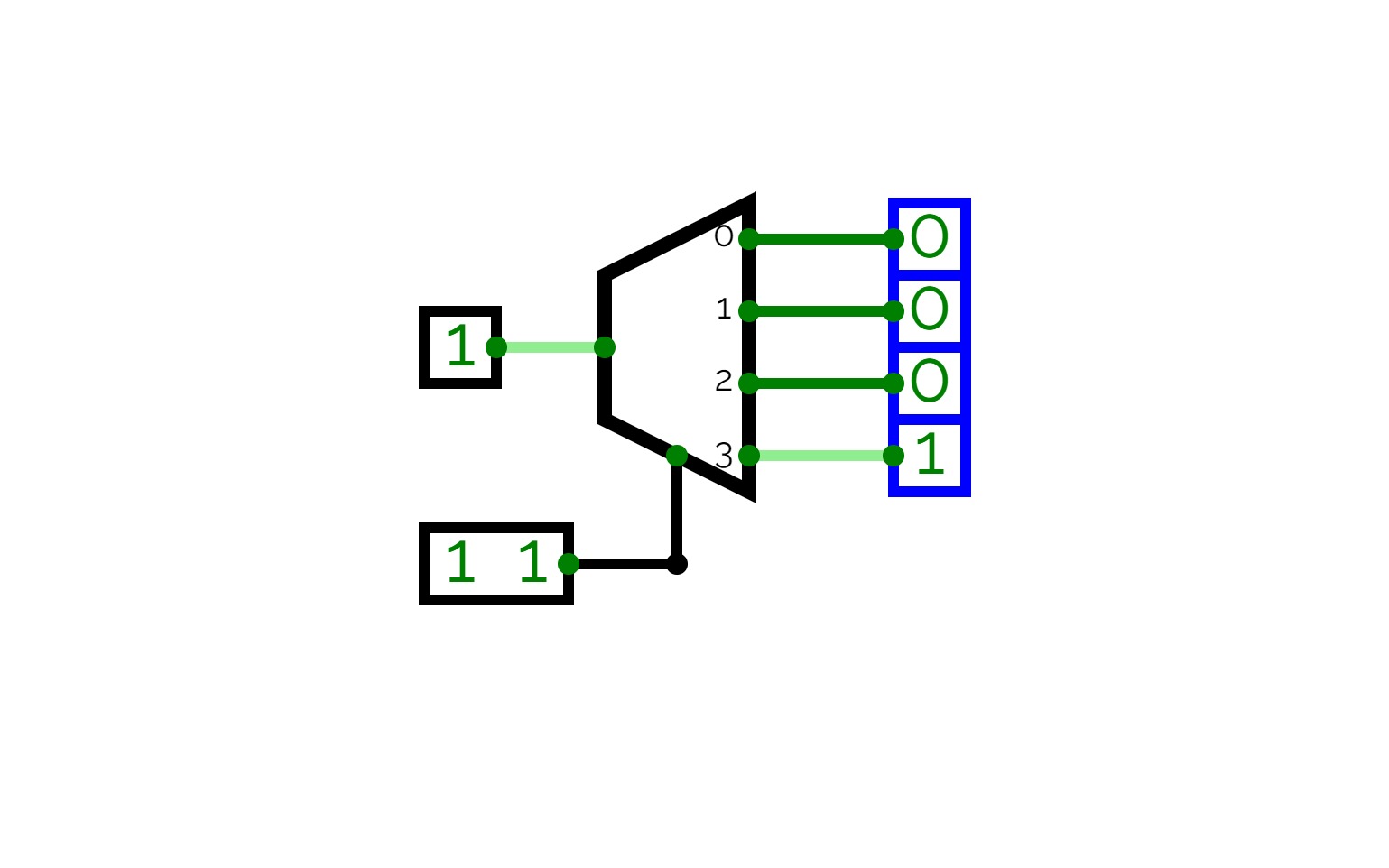

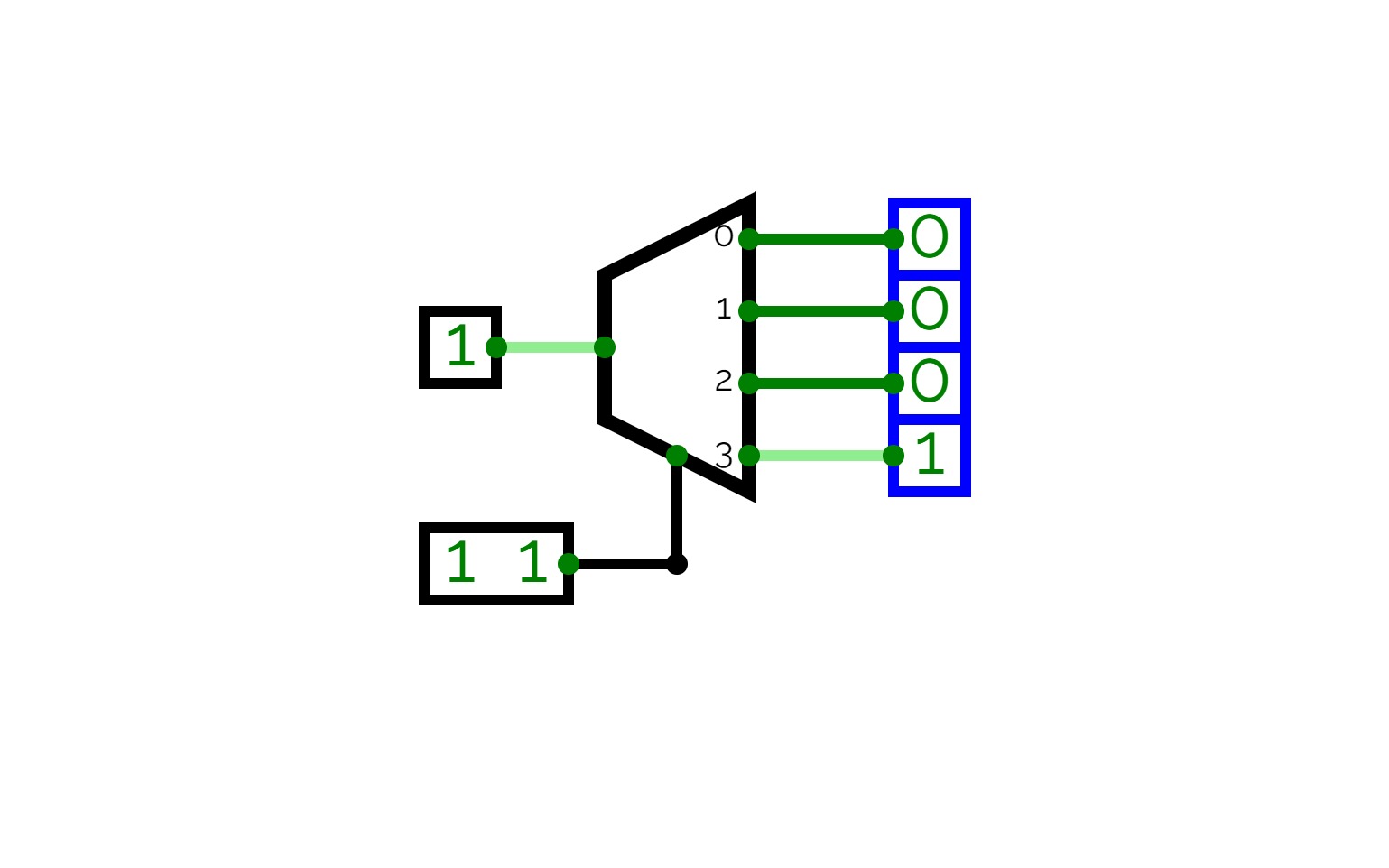

4:1 MUX

4:1 MUX

Realization of 1:4 DEMUX Using Basic Gates

Realization of 1:4 DEMUX Using Basic Gates

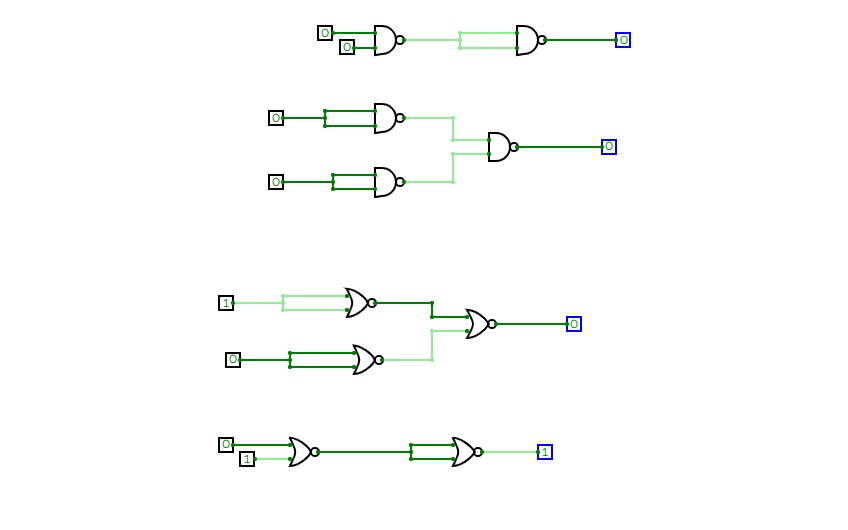

basic gate using NAND gate

basic gate using NAND gate

AND GATE

AND GATE

OR gate

OR gate

NOT gate

NOT gate

EXOR gate

EXOR gate

NOR gate

NOR gate

NAND gate

NAND gate

EX-NOR gate

EX-NOR gate

basic gate using NOR gate

basic gate using NOR gate

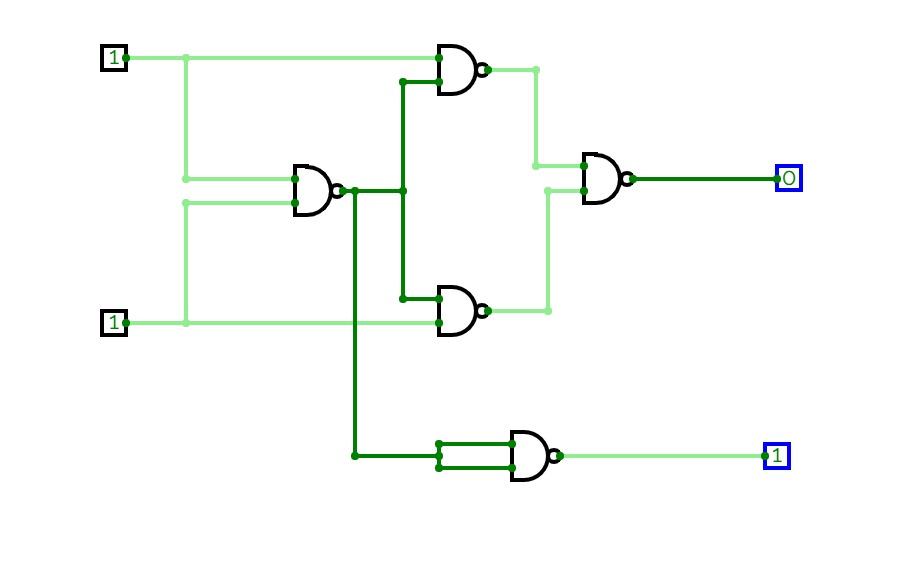

2bit half subtractor

2bit half subtractor

4:2 PRIORITY

4:2 PRIORITY

2:1 MUX Using Universal Gate

2:1 MUX Using Universal Gate

4:1 MUX Using Universal Gate

4:1 MUX Using Universal Gate

2:1 DEMUX Using Universal Gate

2:1 DEMUX Using Universal Gate

4:1 Demux Using Universal Gate

4:1 Demux Using Universal Gate

4:1 Demux Using Universal Gate

4:1 Demux Using Universal Gate

4:1 MUX Using Universal Gate

4:1 MUX Using Universal Gate

Realization of 2:1 Using Basic and XOR Gate

Realization of 2:1 Using Basic and XOR Gate

Realization of 1:4 DEMUX Using Basic Gates

Realization of 1:4 DEMUX Using Basic Gates

1:4 DEMUX

1:4 DEMUX

1:2 Demux

1:2 Demux

2:1 MUX

2:1 MUX

Realization of 2:1 Using Basic and XOR Gate

Realization of 2:1 Using Basic and XOR Gate

1:2 DEMUX Uisng Basic Gate

1:2 DEMUX Uisng Basic Gate

1:4 DEMUX

1:4 DEMUX

4:2 ENCODER

4:2 ENCODER

construct basic gate using nand gate

construct basic gate using nand gate

2 bit half adder nand

2 bit half adder nand

half subractor using nand gate only

half subractor using nand gate only

2 bit half adder

2 bit half adder

full subtractor using NAND gate only

full subtractor using NAND gate only

full adder using NAND gate only

full adder using NAND gate only

Untitled

Untitled

Untitled

Untitled

Realization of 4:1 MUX Using Basic Gates and XOR Gate

Realization of 4:1 MUX Using Basic Gates and XOR Gate

3 bit asynchrouns up counter

3 bit asynchrouns up counter

1:2 Demux

1:2 Demux

Realization of 1:4 DEMUX Using Basic Gates

Realization of 1:4 DEMUX Using Basic Gates

filpflop

filpflop

Realization of 2:1 Using Basic and XOR Gate

Realization of 2:1 Using Basic and XOR Gate

2:1 MUX Using Universal Gate

2:1 MUX Using Universal Gate

4:1 MUX Using Universal Gate

4:1 MUX Using Universal Gate

2:1 DEMUX Using Universal Gate

2:1 DEMUX Using Universal Gate

4:1 Demux Using Universal Gate

4:1 Demux Using Universal Gate

Realization of 1:4 DEMUX Using Basic Gates

Realization of 1:4 DEMUX Using Basic Gates

4:1 MUX

4:1 MUX

Realization of 4:1 MUX Using Basic Gates and XOR Gate

Realization of 4:1 MUX Using Basic Gates and XOR Gate

2:4 DECODER

2:4 DECODER

3 BIT SYNCHRONOUS UP/DOWN COUNTER

3 BIT SYNCHRONOUS UP/DOWN COUNTER

Untitled

Untitled

3 bit asynchrouns down counter

3 bit asynchrouns down counter

mama viva

mama viva