NANDAN TN

Member since: 1 year

Educational Institution: Not Entered

Country: Not Entered

2:1 MUX USING NAND GATES

2:1 MUX USING NAND GATES

Public

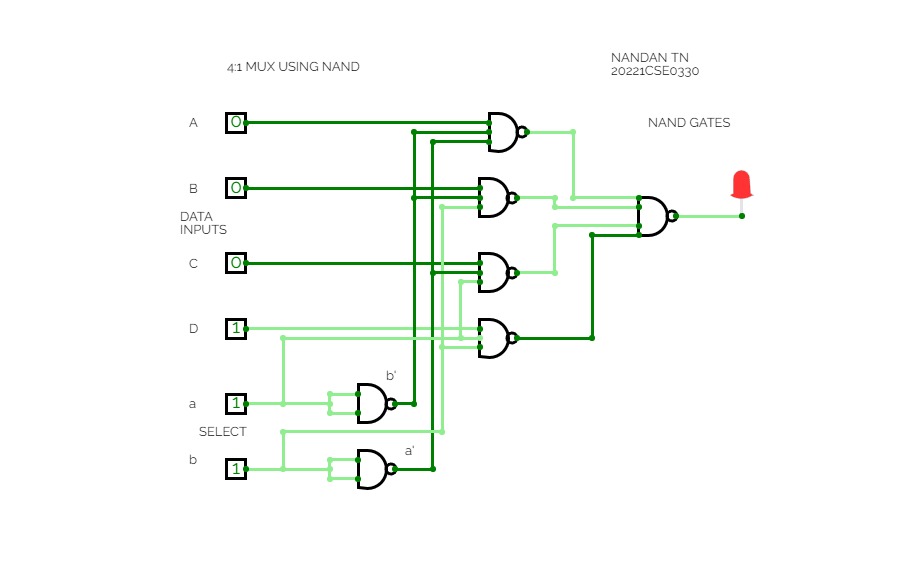

4:1 MUX USING NAND

4:1 MUX USING NAND

Public

1:4 DEMUX USING NAND

1:4 DEMUX USING NAND

Public

6.1

6.1

Public

Untitled

Untitled

Public

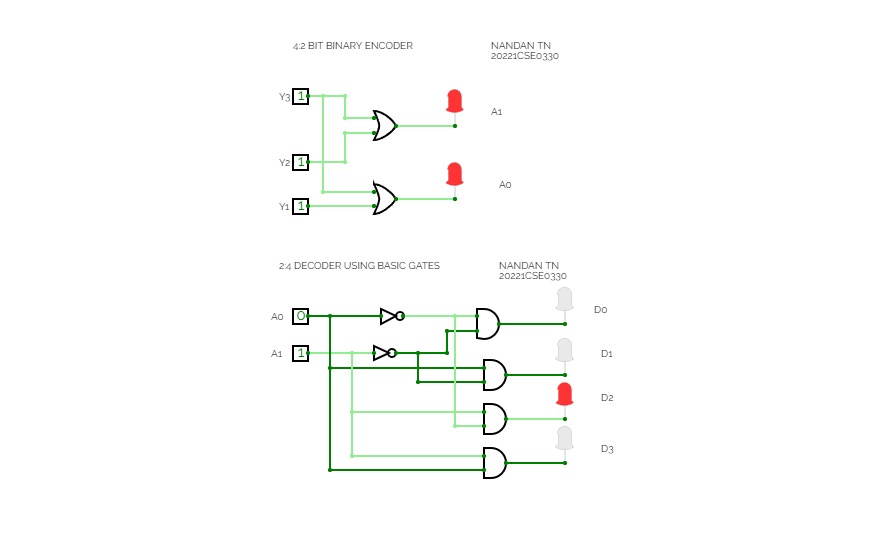

EXP 4 4:2 PRIORITY ENCODER

EXP 4 4:2 PRIORITY ENCODER

Public

EXP 4 LEVEL2 -2

EXP 4 LEVEL2 -2

Public

experiment1

experiment1

Public

experiment1

experiment1

Public

EXP5.2

EXP5.2

Public

nan.5

nan.5

Public

EXP5.2

EXP5.2

Public

EXP5.2

EXP5.2

Public

exp3.1

exp3.1

Public

Experiment5

Experiment5

Public

EXPERIMENT 6

EXPERIMENT 6

Public

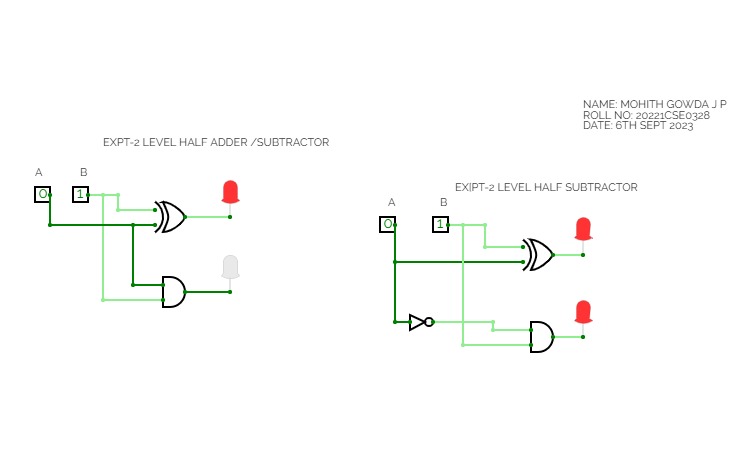

HALF ADDER AND HALF SUBTRACTOR

HALF ADDER AND HALF SUBTRACTOR

Public

FULL ADDER

FULL ADDER

Public

FULL SUBTRACTOR

FULL SUBTRACTOR

Public

EXP LEVEL2

EXP LEVEL2

Public

HALF SUBTRACTOR

HALF SUBTRACTOR

Public

HALF ADDER

HALF ADDER

Public

FULL ADDER

FULL ADDER

Public

FULL SUBTRACTOR

FULL SUBTRACTOR

Public

Untitled

Untitled

Public

EXP5-LEVEL2

EXP5-LEVEL2

Public

EXP7.3

EXP7.3

Public

Untitled

Untitled

Public

EXP7.4

EXP7.4

Public

EXPT-1 IMPLEMENTING BASIC GATES USING UNIVERSAL GATES

EXPT-1 IMPLEMENTING BASIC GATES USING UNIVERSAL GATES

Public

1:2 DEMUX USING BASIC AND NAND GATES

1:2 DEMUX USING BASIC AND NAND GATES

Public

logic diagram using basic gates

logic diagram using basic gates

Public

1:4 MUX USING BASIC GATES

1:4 MUX USING BASIC GATES

Public

NANDAN TN doesn't have any favourites.

Untitled

Untitled

Public