Pavan K

Member since: 1 year

Educational Institution: Presidency University, Bangalore

Country: India

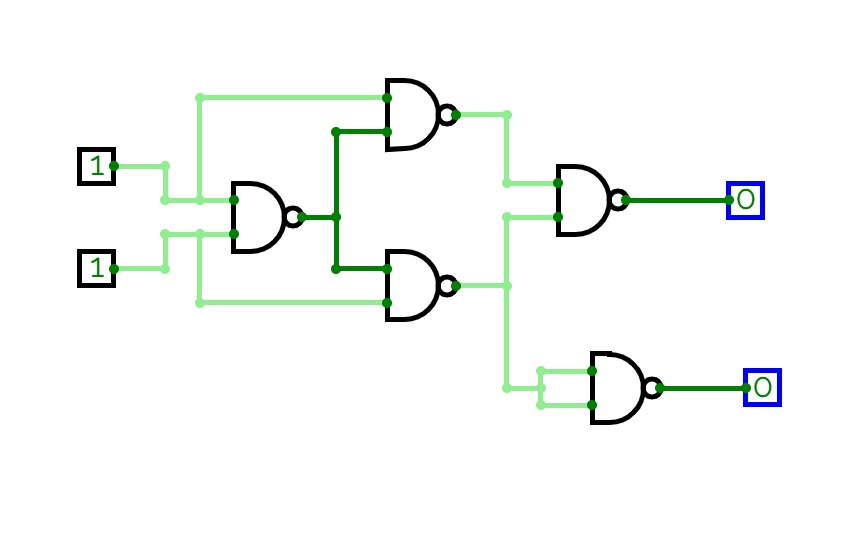

2 bit half subtractor using NAND Gates

2 bit half subtractor using NAND Gates

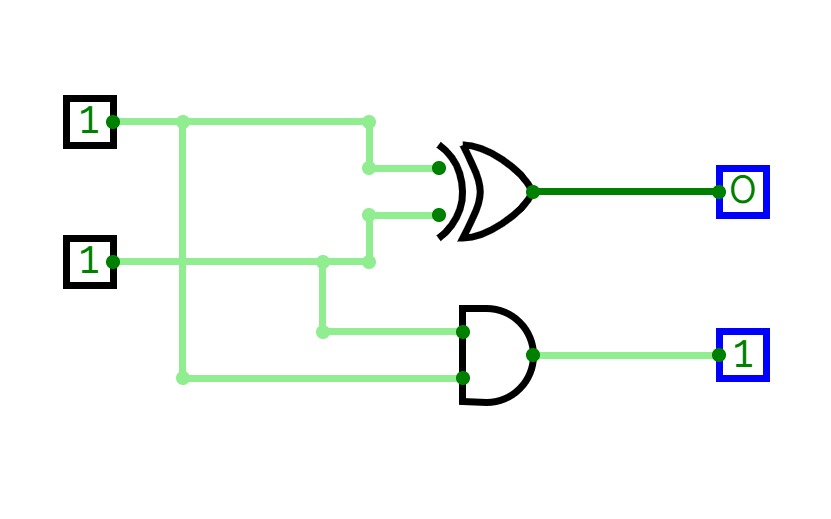

Half Adder

Half Adder

Half Subtractor

Half Subtractor

JK Flip Flop My version

JK Flip Flop My version

Months no of days

Months no of days

Decoder

Decoder

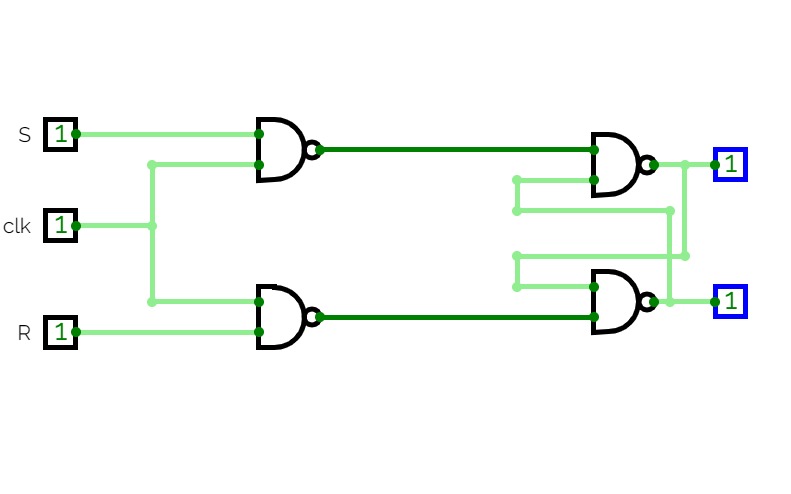

SR Flip Flop

SR Flip Flop

All Adders and Subtractors

All Adders and Subtractors

Multiplexer

Multiplexer

Experiment-5(Basic Gates)

Experiment-5(Basic Gates)

Experiment-5(NAND Gates)

Experiment-5(NAND Gates)

Assignment(Basic gates)

Assignment(Basic gates)

JK Flip Flop

JK Flip Flop

T Flip Flop

T Flip Flop

D flip flop

D flip flop

2:1 MUX

2:1 MUX

1:2 DEMUX

1:2 DEMUX

3 Bit Synchronous Up Counter J-K Flip Flops

3 Bit Synchronous Up Counter J-K Flip Flops

PRIORITY ENCODER

PRIORITY ENCODER

3 bit Synchronous up counter

3 bit Synchronous up counter

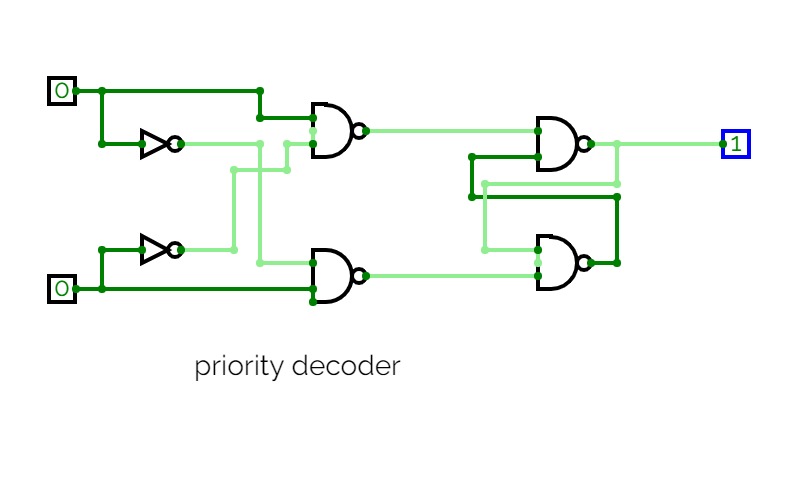

PRIORITY DECODER

PRIORITY DECODER

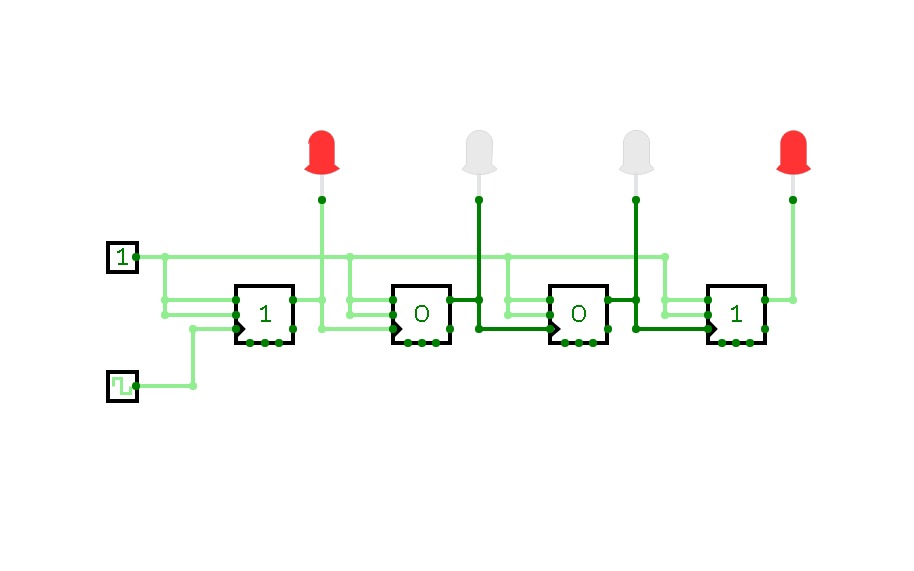

4:2 BINARY ENCODER

4:2 BINARY ENCODER

4-Bit Synchronous Up Counter

4-Bit Synchronous Up Counter

BASIC GATE USING NAND GATE

BASIC GATE USING NAND GATE

JK TO D FLIP FLOP NAND GATE

JK TO D FLIP FLOP NAND GATE

4-bit Asynchronous Up counter

4-bit Asynchronous Up counter

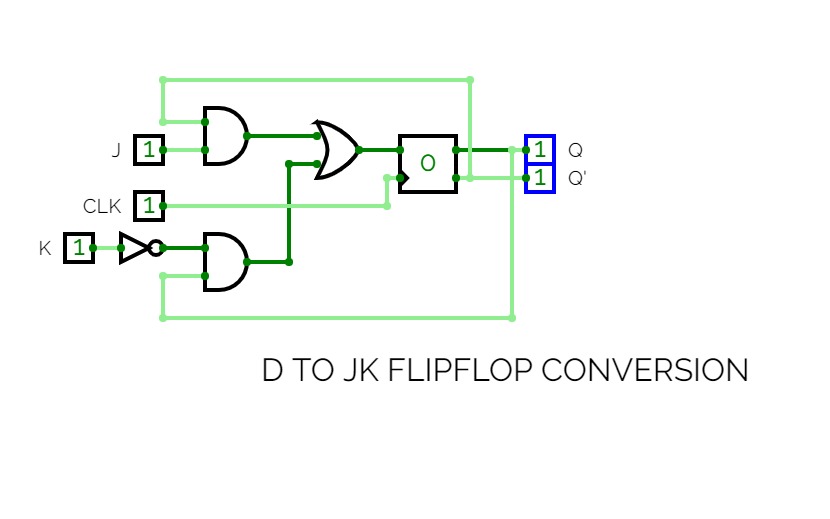

D TO JK CONVERSION FLIP FLOP

D TO JK CONVERSION FLIP FLOP

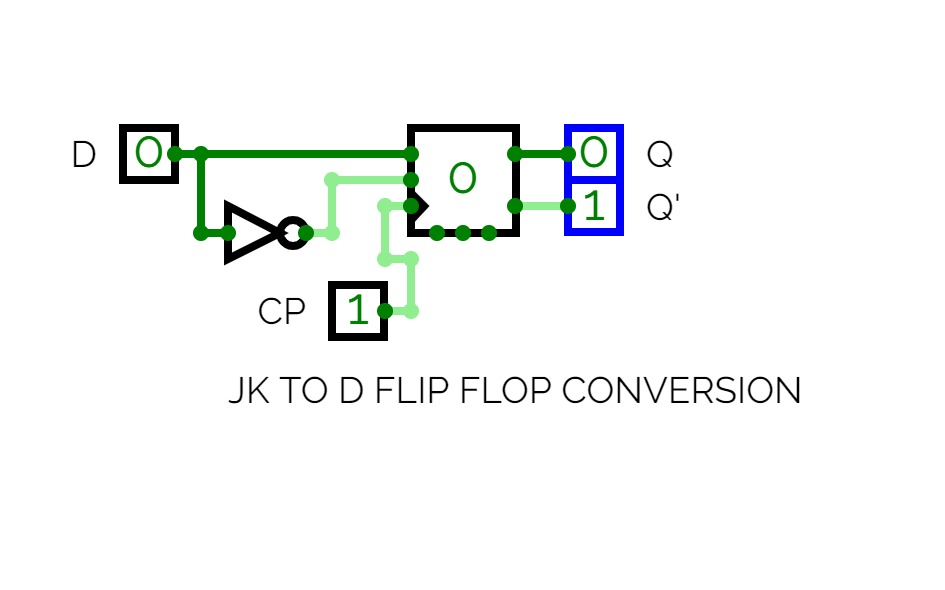

JK TO D CONVERSION

JK TO D CONVERSION

3 bit asynchronous up counter

3 bit asynchronous up counter

8:3 Encoder

8:3 Encoder

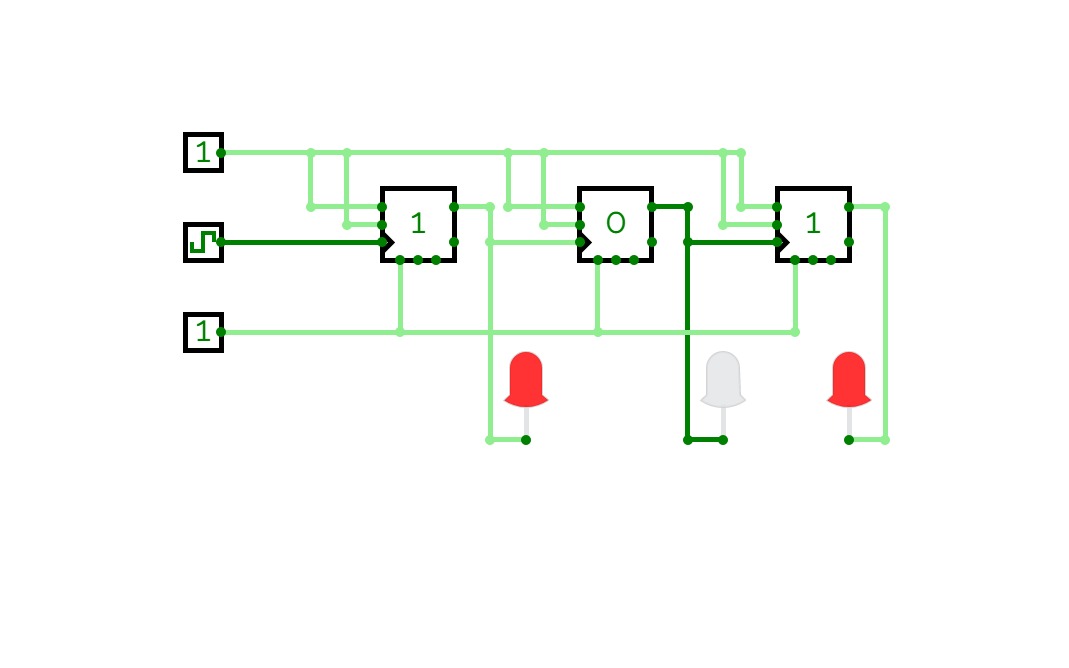

3 bit Magnitude Comparator

3 bit Magnitude Comparator

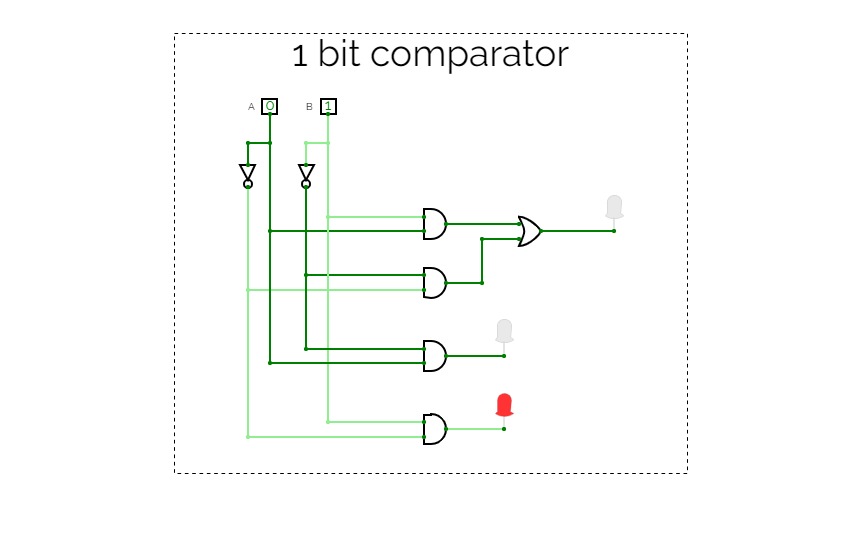

Comparator(1 and 2 bit)

Comparator(1 and 2 bit)

BASIC GATES

BASIC GATES

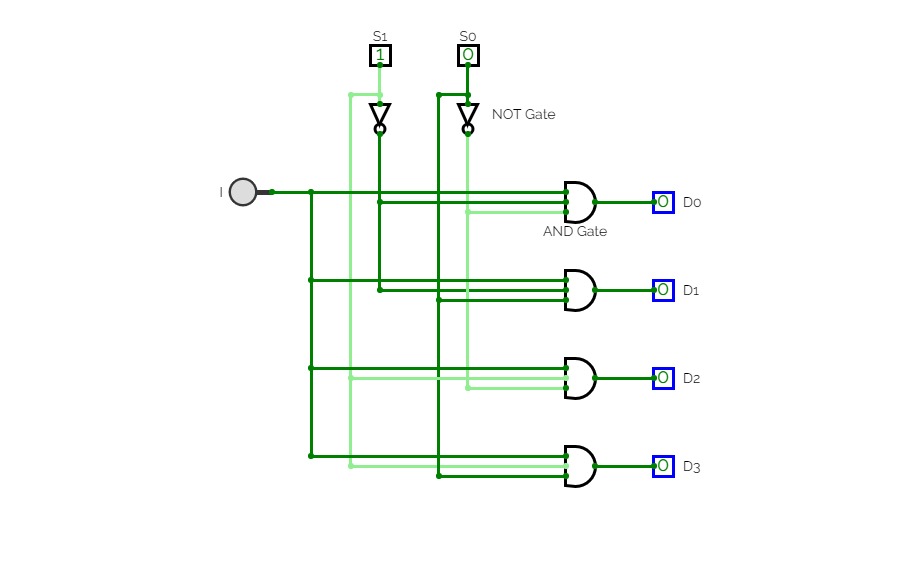

1:4 Demultiplexer

1:4 Demultiplexer