VIDYASAGAR M

Member since: 1 year

Educational Institution: Not Entered

Country: Not Entered

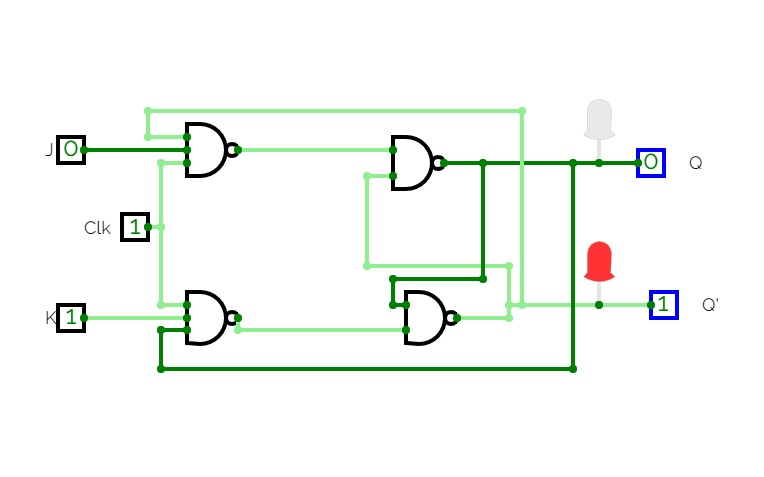

JK

JK

Probelm solving 01 using NAND gates

Probelm solving 01 using NAND gates

Untitled

Untitled

Experiment 5 using basic gates

Experiment 5 using basic gates

2 BIT USING BASIC GATE

2 BIT USING BASIC GATE

2 BIT COMPARATOR USING BASIC GATES

2 BIT COMPARATOR USING BASIC GATES

2 BIT COMPARATOR USING BASIC GATES

2 BIT COMPARATOR USING BASIC GATES

4:2 PRIORITY ENCODER

4:2 PRIORITY ENCODER

ENCODER

ENCODER

2:4 DECODER

2:4 DECODER

Untitled

Untitled

Flip flop

Flip flop

Untitled

Untitled

EXP 4 LV 2 FLIPFLOPS

EXP 4 LV 2 FLIPFLOPS

Untitled

Untitled

4;1 demux using NAND gate

4;1 demux using NAND gate

Full Adder

Full Adder

4:1 DEMUX

4:1 DEMUX

Half adder

Half adder

Half adder using NAND

Half adder using NAND

Half Subtractor

Half Subtractor

FULL SUBTRACTOR

FULL SUBTRACTOR

2:1 MUX

2:1 MUX

Half Subtractor

Half Subtractor

Full subtractor using NAND

Full subtractor using NAND

2:1 DEMUX

2:1 DEMUX

4:1 DEMUX

4:1 DEMUX

LOGIC GATES

LOGIC GATES

4:1 MUX

4:1 MUX

2:1 DEMUX USING NAND

2:1 DEMUX USING NAND

2:1 DEMUX USING NAND

2:1 DEMUX USING NAND

4:1 DEMUX USING NAND

4:1 DEMUX USING NAND

2:1 MUX USING NAND

2:1 MUX USING NAND

4:1 MUX USING NAND

4:1 MUX USING NAND

Probelm solving 01 using basic gates

Probelm solving 01 using basic gates

UNIVERSAL GATE IMPLEMENTATION USING NAND

UNIVERSAL GATE IMPLEMENTATION USING NAND

EXP5

EXP5

4:2 BINARY ENCODER

4:2 BINARY ENCODER

T FLIP FLOP

T FLIP FLOP

Half subtractor using NAND

Half subtractor using NAND

jk1

jk1

S-R FLIP FLOP(SET-RESET)

S-R FLIP FLOP(SET-RESET)

4 BIT SYNCHRONOUS UP COUNTER

4 BIT SYNCHRONOUS UP COUNTER

3 BIT Synchronous counter

3 BIT Synchronous counter

Half adder using NAND

Half adder using NAND

Half subtractor using NAND

Half subtractor using NAND

Full adder using NAND

Full adder using NAND