Karen Joseph Williams

Member since: 1 year

Educational Institution: Not Entered

Country: Not Entered

mux using 8:1

mux using 8:1

MUX using SOP

MUX using SOP

MUX using POS 22BCE2797

MUX using POS 22BCE2797

HS 4X1 MUX 22BKT0156

HS 4X1 MUX 22BKT0156

T2 HA 4:1 MUX

T2 HA 4:1 MUX

Half Subtractor

Half Subtractor

SOP using MUX

SOP using MUX

3*3 Multiplier

3*3 Multiplier

Half Subtractor

Half Subtractor

Untitled

Untitled

TASK 2 03 L43+L44 4x4 Multiplier

TASK 2 03 L43+L44 4x4 Multiplier

3*3 Multiplier

3*3 Multiplier

Untitled

Untitled

3x3 multiplier

3x3 multiplier

PISO SHIFT REGISTER

PISO SHIFT REGISTER

PISO

PISO

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

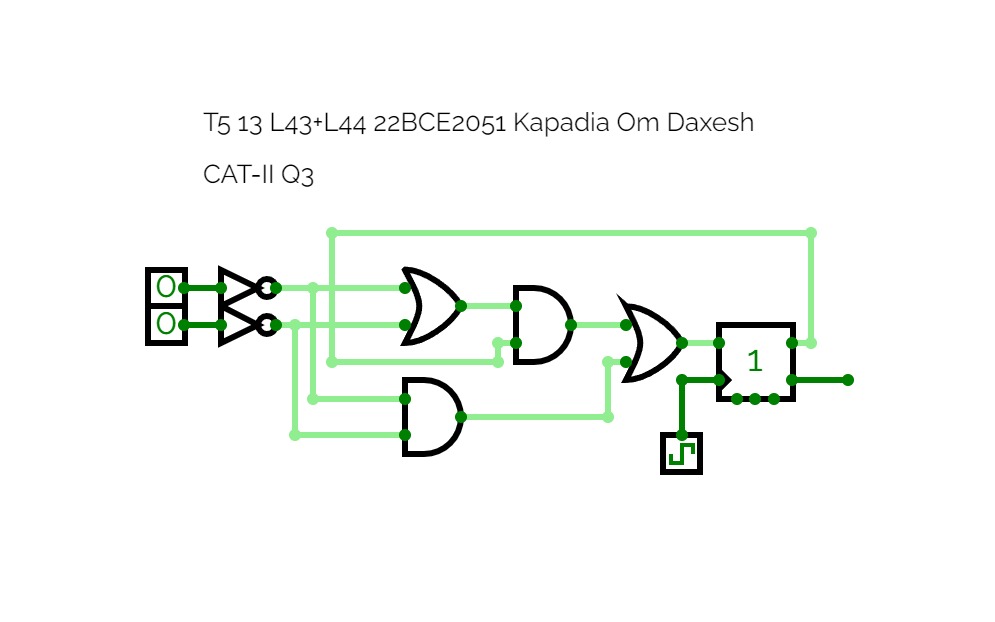

q3b1_2

q3b1_2

CAT 2 Q3 B1

CAT 2 Q3 B1

q1b2_2

q1b2_2

UntitledCAT2B1Q5

UntitledCAT2B1Q5

CAT 2 Q5 B1

CAT 2 Q5 B1

q3b2_2

q3b2_2

CAT2 Q4 B2

CAT2 Q4 B2

q5b2_2

q5b2_2

CAT2 Q5 B2

CAT2 Q5 B2

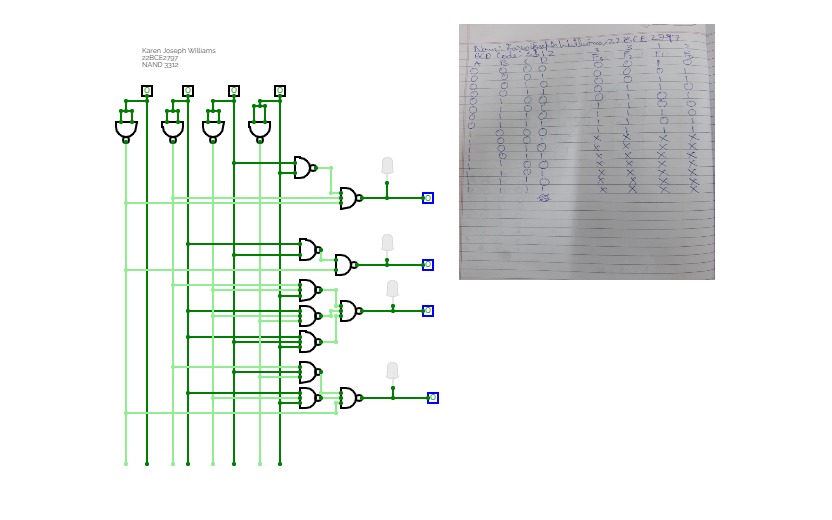

NAND 3312

NAND 3312

Half Adder Task 2

Half Adder Task 2

Half Adder Task 2

Half Adder Task 2

Full Adder Task 2

Full Adder Task 2

Full Subtractor Task 2

Full Subtractor Task 2

Half Subtractor Task 2

Half Subtractor Task 2

Untitled

Untitled

Untitled

Untitled

TASK 1 DSD

TASK 1 DSD

TASK 1 DSD

TASK 1 DSD

TASK 1 DSD POS

TASK 1 DSD POS

TASK 1 DSD POS NOR Gate

TASK 1 DSD POS NOR Gate

TASK 1 DSD POS NOR Gate

TASK 1 DSD POS NOR Gate

TASK 1 DSD SOP Using AND Gate

TASK 1 DSD SOP Using AND Gate

Untitled

Untitled

4x1 MUX Viva

4x1 MUX Viva

8x1 MUX VIVA

8x1 MUX VIVA

8x1 MUX 2 VIVA

8x1 MUX 2 VIVA

4x1 MUX 2 Viva

4x1 MUX 2 Viva

1 Bit ALU Task 3 22BCE2797

1 Bit ALU Task 3 22BCE2797

SOP canonical expression of MUX and circuit implemented in MUX

SOP canonical expression of MUX and circuit implemented in MUX

3 bit ODD parity VIVA q1 Karen Joseph Williams 22BCE2797

3 bit ODD parity VIVA q1 Karen Joseph Williams 22BCE2797

Decoder 1 Viva q2 Karen Joseph Williams

Decoder 1 Viva q2 Karen Joseph Williams

Untitled

Untitled

Decoder 2 Viva q2 Karen Joseph Williams 22BCE2797

Decoder 2 Viva q2 Karen Joseph Williams 22BCE2797

Multiplexer 1 Viva q2 Karen Joseph Williams 22BCE2797

Multiplexer 1 Viva q2 Karen Joseph Williams 22BCE2797

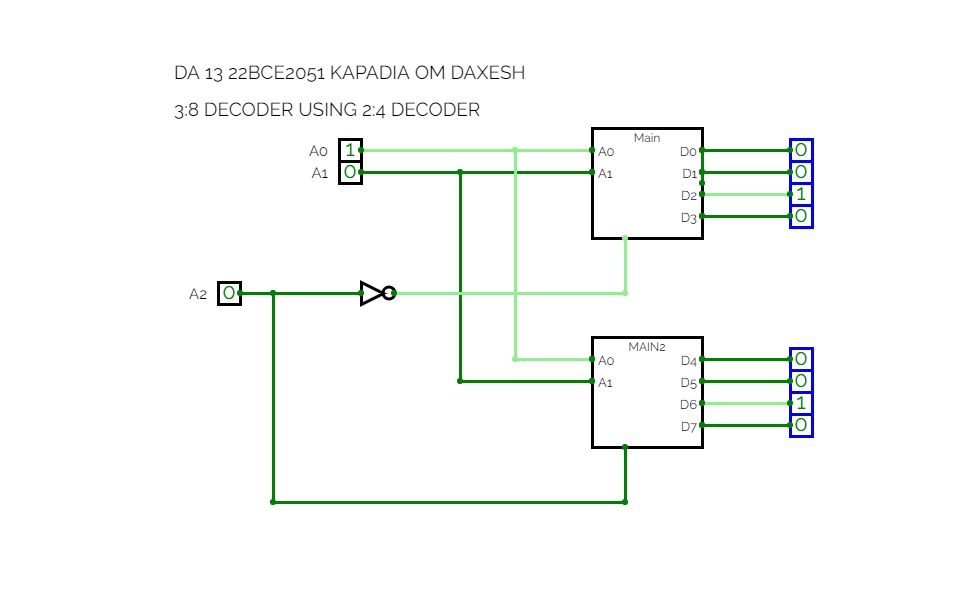

3*8 DECODER USING TWO 2*4 DECODERS

3*8 DECODER USING TWO 2*4 DECODERS

Untitled

Untitled

SISO SHIFT REGISTER

SISO SHIFT REGISTER

SIPO SHIFT REGISTER

SIPO SHIFT REGISTER

Decoder

Decoder

Decoder based design

Decoder based design

2:1 MUX

2:1 MUX

Odd bit Parity VIVA Karen 22BCE2797

Odd bit Parity VIVA Karen 22BCE2797

CAT 1 Q1 B2

CAT 1 Q1 B2

q2b1_2

q2b1_2

Untitled

Untitled

CAT2 Q2 B1

CAT2 Q2 B1

CAT 2 Q1 B2

CAT 2 Q1 B2

CAT2 Q3 B2

CAT2 Q3 B2

Untitled

Untitled

q4b2_2

q4b2_2

Untitled

Untitled

CAT 1 Q2

CAT 1 Q2

CAT1 B2

CAT1 B2

CAT1 B1

CAT1 B1

T5 Cat 1 Q4 22BCE2797

T5 Cat 1 Q4 22BCE2797

CAT 1 Q2 B2

CAT 1 Q2 B2

CAT 1 Q4 B2

CAT 1 Q4 B2

q4b1_2

q4b1_2

CAT 2 Q4 B1

CAT 2 Q4 B1

PIPO

PIPO

PIPO Shift Register

PIPO Shift Register

Bidirectional Shift Register

Bidirectional Shift Register

Untitled

Untitled

HALF SUBTRACTOR USING 4:1 MUX

HALF SUBTRACTOR USING 4:1 MUX

Pos Canonical Expression in MUX

Pos Canonical Expression in MUX

Half Subtractor using MUX

Half Subtractor using MUX

HALF ADDER USING 4:1 MUX

HALF ADDER USING 4:1 MUX

Pos Canonical Expression in MUX

Pos Canonical Expression in MUX

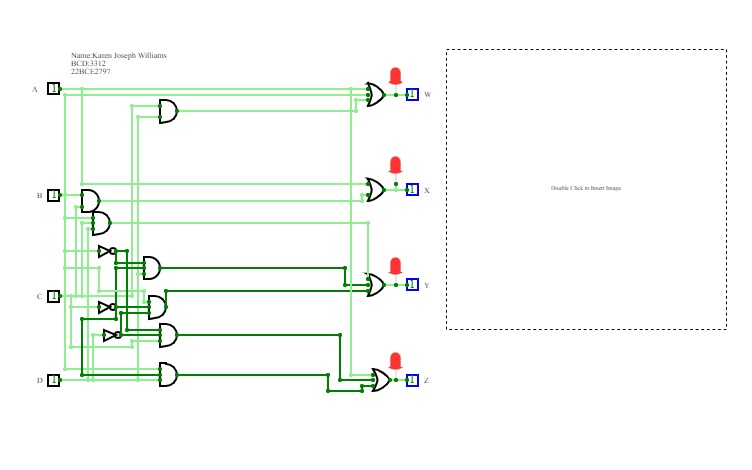

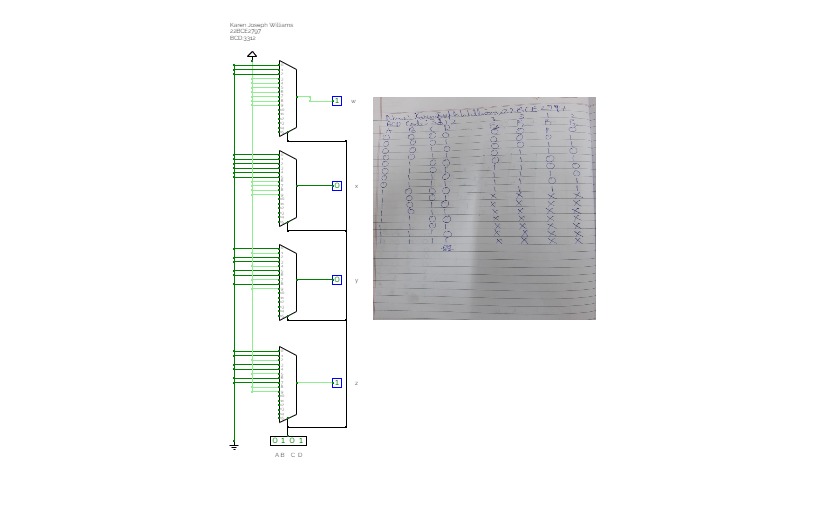

BCD:3312

BCD:3312

3312 Multiplexer

3312 Multiplexer

3312 Decoder

3312 Decoder

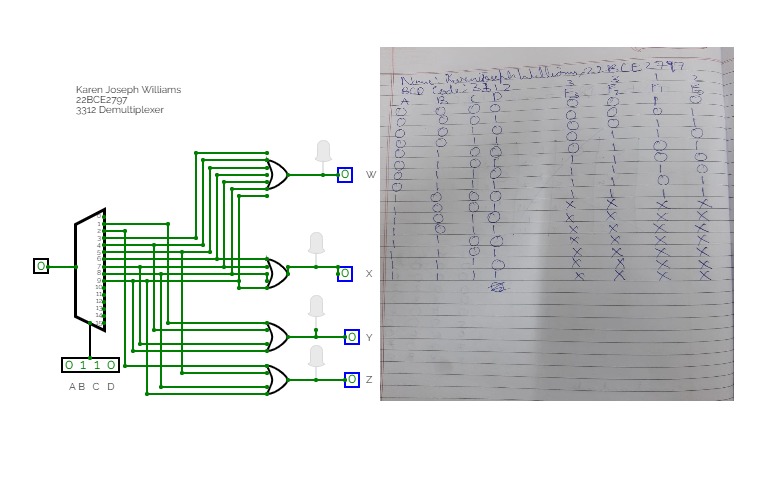

3312 Demultiplexer

3312 Demultiplexer

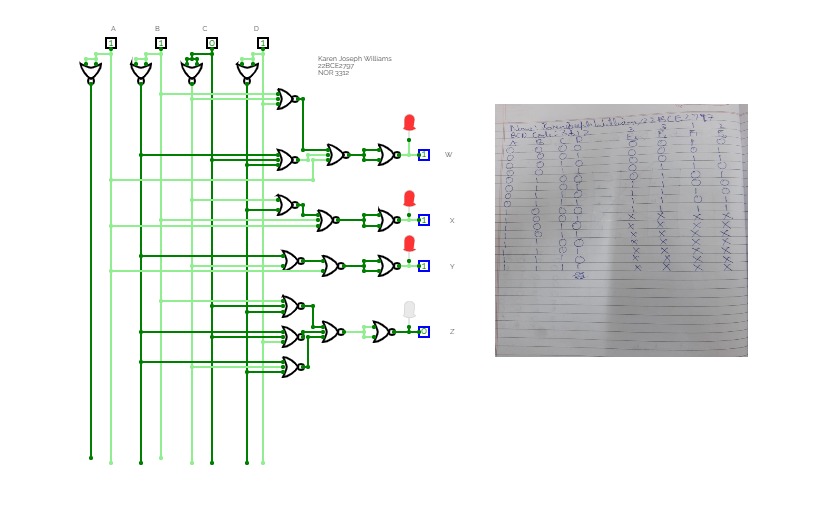

NOR 3312

NOR 3312

Multiplexer 2 Viva q2 Karen Joseph Williams 22BCE2797

Multiplexer 2 Viva q2 Karen Joseph Williams 22BCE2797

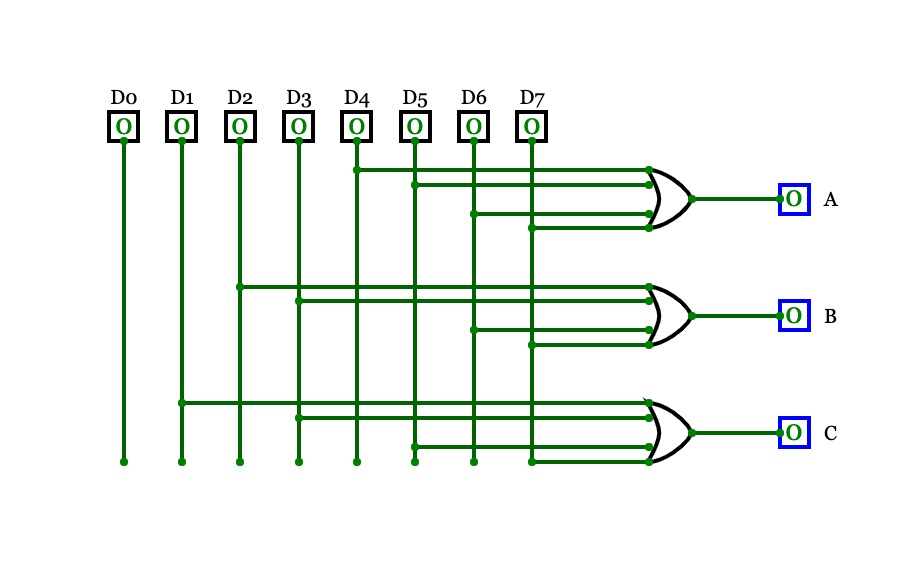

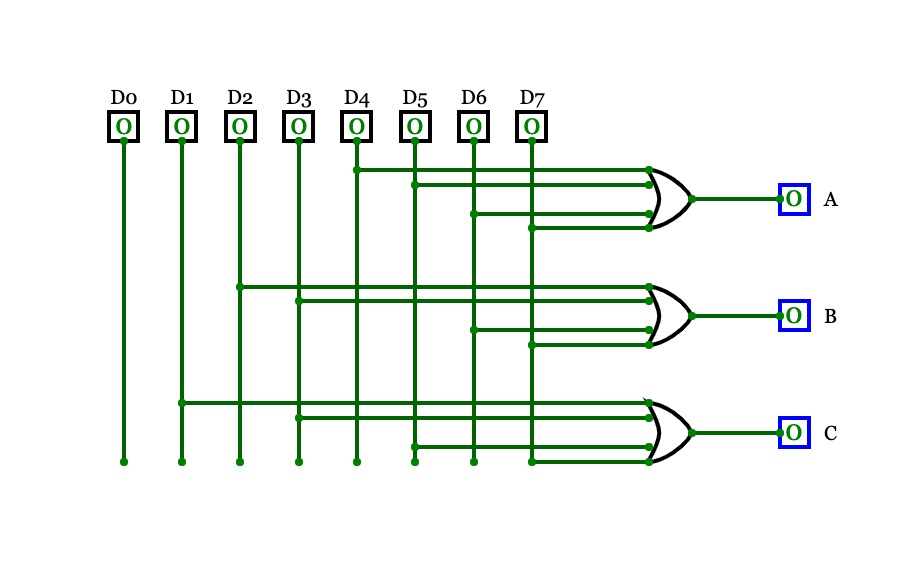

8:3 Encoder

8:3 Encoder

8:3 Encoder

8:3 Encoder

7 segment display using 1:16 decoder

7 segment display using 1:16 decoder