Naman Agrawal

Member since: 1 year

Educational Institution: Not Entered

Country: Not Entered

cat2 b2 q1

cat2 b2 q1

CAT2 B2 Q3

CAT2 B2 Q3

CAT 2 B2 Q3

CAT 2 B2 Q3

CAT1 B2 Q2

CAT1 B2 Q2

CAT1 B2 Q3

CAT1 B2 Q3

CAT B1 Q1

CAT B1 Q1

CAT 2 B1 Q3

CAT 2 B1 Q3

Half Adder

Half Adder

Full Adder

Full Adder

Half Subtractor

Half Subtractor

Full Subtractor

Full Subtractor

3*3 Multiplier

3*3 Multiplier

T1 25 L43+L44 22BCE2904 Naman Agrawal F’=Σm( 1,3,5,6,7,8,10,13,15 ) = AB’D’+A’BC+A’D+BD

T1 25 L43+L44 22BCE2904 Naman Agrawal F’=Σm( 1,3,5,6,7,8,10,13,15 ) = AB’D’+A’BC+A’D+BD

T1 25 L43+L44 22BCE2904 POS NOR F=πM( 1,3,5,6,7,8,10,13,15) = (A'+B+D)(A+B'+C')(A+D')(B'+D')

T1 25 L43+L44 22BCE2904 POS NOR F=πM( 1,3,5,6,7,8,10,13,15) = (A'+B+D)(A+B'+C')(A+D')(B'+D')

Q7

Q7

Q16

Q16

Pos Canonical Expression in MUX

Pos Canonical Expression in MUX

Circuit diagram of 2:1 MUX Circuit using SOP Equation --- NAND circuit

Circuit diagram of 2:1 MUX Circuit using SOP Equation --- NAND circuit

B1 CAT1 Q2

B1 CAT1 Q2

CAT2 B2 Q2

CAT2 B2 Q2

CAT2 B2 Q2

CAT2 B2 Q2

cat2 b2 q5

cat2 b2 q5

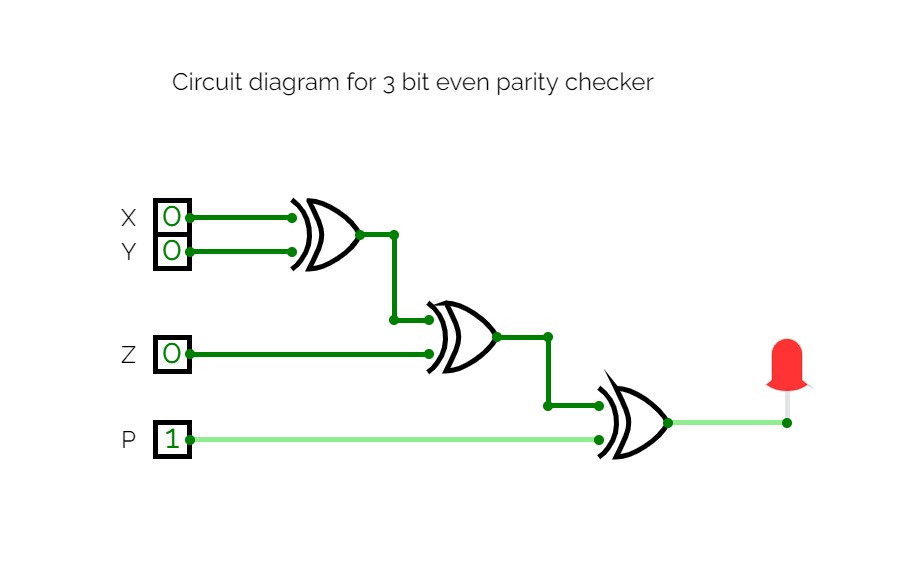

Circuit diagram for 3 bit even parity checker

Circuit diagram for 3 bit even parity checker

7 Seg Decoder

7 Seg Decoder

Decoder 22BCE2904

Decoder 22BCE2904

(x'y'z')+(xyz')Decoder Based design 22BCE2904

(x'y'z')+(xyz')Decoder Based design 22BCE2904

(x'y'z')+(x+y+z') 22BCE2904 Multiplexer

(x'y'z')+(x+y+z') 22BCE2904 Multiplexer

1 BIT alu

1 BIT alu

30_22BCE3117_1Bit_ALU

30_22BCE3117_1Bit_ALU

4 BIT ALU

4 BIT ALU

FS 8:1 MUX 22BKT0156

FS 8:1 MUX 22BKT0156

F POS decoder

F POS decoder

Ha decoder

Ha decoder

FADECODER 22BKT0156

FADECODER 22BKT0156

HS using Decoder

HS using Decoder

FA using Decoder

FA using Decoder

HS using Decoder

HS using Decoder

HS usiing Decoder

HS usiing Decoder

f sop using decoder

f sop using decoder

HS 4X1 MUX 22BKT0156

HS 4X1 MUX 22BKT0156

HS 4X1 MUX 22BKT0156

HS 4X1 MUX 22BKT0156

Half Subtractor MUX

Half Subtractor MUX

T2 HA 4:1 MUX

T2 HA 4:1 MUX

FS 4:1 MUX 22BKT0156

FS 4:1 MUX 22BKT0156

Half Subtractor using MUX

Half Subtractor using MUX

Untitled

Untitled

NAND logic circuit of 2:4 decoder 03 22BCE0220 L43+L44

NAND logic circuit of 2:4 decoder 03 22BCE0220 L43+L44

NAND logic circuit of 2:4 decoder 25 22BCE2904L43+L44

NAND logic circuit of 2:4 decoder 25 22BCE2904L43+L44

Untitled

Untitled

1:2 Decoder using Mux

1:2 Decoder using Mux

SOPBCD3321

SOPBCD3321

DA Q3 POS (OAI)

DA Q3 POS (OAI)

BCDMUX

BCDMUX

BCDPOSOAI

BCDPOSOAI

DA QUES 3 DECODER

DA QUES 3 DECODER

BCDDecoder

BCDDecoder

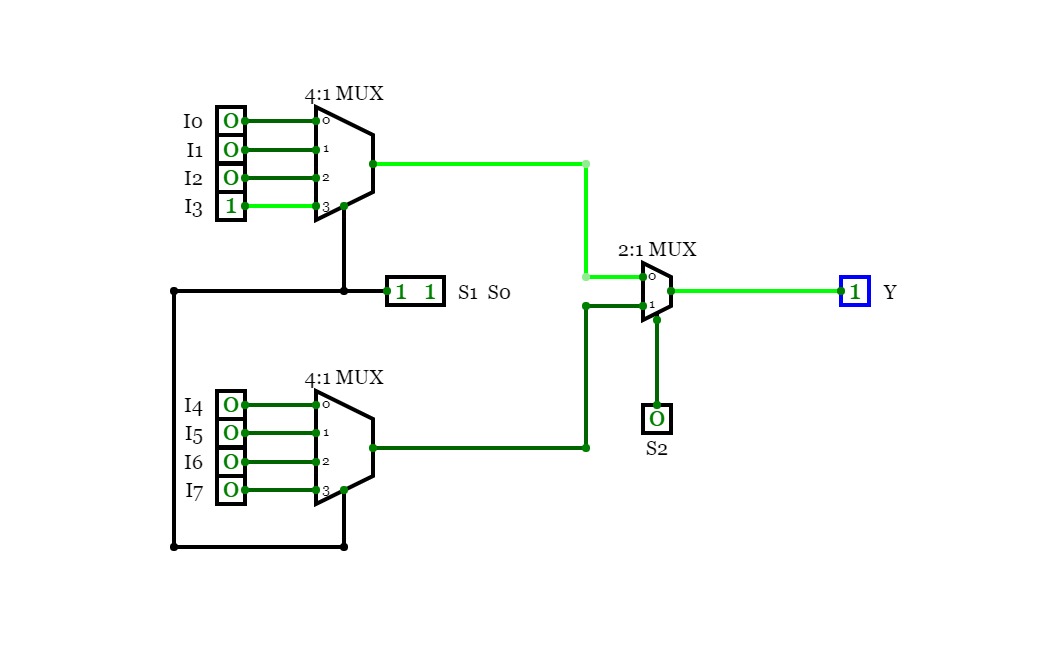

8:1 MUX USING 4:1 25 22BCE2904

8:1 MUX USING 4:1 25 22BCE2904

Untitled

Untitled

4:1 MUX using 2:1 MUX 22BCE2904 25

4:1 MUX using 2:1 MUX 22BCE2904 25

8:1 MUX using 4:1 MUX & 2:1 MUX

8:1 MUX using 4:1 MUX & 2:1 MUX

Question 1 DSD

Question 1 DSD

Bidirectional Shift Register

Bidirectional Shift Register

Bidirectional shift register 22BCE2904 24

Bidirectional shift register 22BCE2904 24

Ring Counter 22BCE2904 24

Ring Counter 22BCE2904 24

Johnson 24 22BCE2904

Johnson 24 22BCE2904

CAT2 B2 Q5

CAT2 B2 Q5

Decoder

Decoder

3 Bit Even Parity Checker 22BCE2904 Naman Agrawal

3 Bit Even Parity Checker 22BCE2904 Naman Agrawal

1:2 Decoder using Mux

1:2 Decoder using Mux

CAT2 B1 Q5

CAT2 B1 Q5

question 8 part A

question 8 part A

CAT1B1Q3

CAT1B1Q3

CAT 1 Q3 B1

CAT 1 Q3 B1

CAT 1 Q4 B1

CAT 1 Q4 B1

cat1 b1 q5

cat1 b1 q5

CAT1 B1 Q5

CAT1 B1 Q5

Cat2 B2 Q1

Cat2 B2 Q1

CAT2 B2 Q4

CAT2 B2 Q4

CAT2 B2 Q4

CAT2 B2 Q4

B1 CAT1 Q1

B1 CAT1 Q1

B1 CAT1 Q1

B1 CAT1 Q1

CAT1 B2 Q1

CAT1 B2 Q1

cat1b2q1

cat1b2q1

cat1b2q3

cat1b2q3

B2 Q4 CAT1

B2 Q4 CAT1

cat1b2q5

cat1b2q5

CAT-I Q4 B2

CAT-I Q4 B2

cat2 b1 q2

cat2 b1 q2

CAT2 B1 Q4

CAT2 B1 Q4

cat2b1q4

cat2b1q4

CAT2 B1 Q3

CAT2 B1 Q3

CAT1 B2 Q5

CAT1 B2 Q5

cat2b1q1

cat2b1q1

CAT2 B1 Q5

CAT2 B1 Q5

DA QUES3 MUX

DA QUES3 MUX

SOPBCD

SOPBCD

DA Q3 NOR

DA Q3 NOR

DA QUES 3 DEMUX

DA QUES 3 DEMUX

DA Q3 NAND

DA Q3 NAND

BCDNOR

BCDNOR

BCDDEmux

BCDDEmux

BCDNAND

BCDNAND

T1 25 L43+L44 22BCE2904 POS NAND F(0,2,4,9,11,12,14)=A’B’D’+A’C’D’+AB’D+ABD’

T1 25 L43+L44 22BCE2904 POS NAND F(0,2,4,9,11,12,14)=A’B’D’+A’C’D’+AB’D+ABD’

T1 25 L43+L44 22BCE2904 SOP NAND F’=Σm( 1,3,5,6,7,8,10,13,15 ) = AB’D’+A’BC+A’D+BD

T1 25 L43+L44 22BCE2904 SOP NAND F’=Σm( 1,3,5,6,7,8,10,13,15 ) = AB’D’+A’BC+A’D+BD

T1 25 L43+L44 22BCE2904 POS F’=πM( 0,2,4,9,11,12,14) = (A+B+D)(A+C+D)(A’+B+D’)(A’+B’+D)

T1 25 L43+L44 22BCE2904 POS F’=πM( 0,2,4,9,11,12,14) = (A+B+D)(A+C+D)(A’+B+D’)(A’+B’+D)

(x+y')(x'+y)(z')Multiplexer based design 22BCE2904

(x+y')(x'+y)(z')Multiplexer based design 22BCE2904

Circuit diagram of 2:1 MUX Circuit using SOP Equation -- AOI circuit

Circuit diagram of 2:1 MUX Circuit using SOP Equation -- AOI circuit

AOI logic circuit of 4:2 encode25 22BCE2904 L43+L44

AOI logic circuit of 4:2 encode25 22BCE2904 L43+L44

NAND logic circuit of 4:2 encoder 03 22BCE0220 L43+L44

NAND logic circuit of 4:2 encoder 03 22BCE0220 L43+L44

30_22BCE3117_4Bit ALU

30_22BCE3117_4Bit ALU

Circuit diagram of 2:1 MUX Circuit using POS Equation --- NOR circuit

Circuit diagram of 2:1 MUX Circuit using POS Equation --- NOR circuit

AOI logic circuit of 2:4 decoder 03 22BCE0220 L43+L44

AOI logic circuit of 2:4 decoder 03 22BCE0220 L43+L44

Circuit diagram of 2:1 MUX Circuit using POS Equation --- OAI circuit

Circuit diagram of 2:1 MUX Circuit using POS Equation --- OAI circuit

Half Adder using Mux

Half Adder using Mux

4 Bit Adder

4 Bit Adder

Synchronous 4 bit up down counter

Synchronous 4 bit up down counter

T1 25 L43+L44 22BCE2904 Naman Agrawal SOP Circuit F=Σm( 0,2,4,9,11,12,14 )=A’B’D’+A’C’D’+AB’D+ABD’

T1 25 L43+L44 22BCE2904 Naman Agrawal SOP Circuit F=Σm( 0,2,4,9,11,12,14 )=A’B’D’+A’C’D’+AB’D+ABD’

AOI logic circuit of 4:2 encoder 03 22BCE0220 L43+L44

AOI logic circuit of 4:2 encoder 03 22BCE0220 L43+L44

cat2b1q2

cat2b1q2

4 bit Johnson Counter

4 bit Johnson Counter

T1 25 L43+L44 22BCE2904 POS F=πM( 1,3,5,6,7,8,10,13,15) = (A'+B+D)(A+B'+C')(A+D')(B'+D')

T1 25 L43+L44 22BCE2904 POS F=πM( 1,3,5,6,7,8,10,13,15) = (A'+B+D)(A+B'+C')(A+D')(B'+D')

DA Q3 NOR

DA Q3 NOR

T1 25 L43+L44 22BCE2904 Naman Agrawal POS F’=πM( 0,2,4,9,11,12,14) = (A+B+D)(A+C+D)(A’+B+D’)(A’+B’+D)

T1 25 L43+L44 22BCE2904 Naman Agrawal POS F’=πM( 0,2,4,9,11,12,14) = (A+B+D)(A+C+D)(A’+B+D’)(A’+B’+D)