Sanchita Jindal

Member since: 1 year

Educational Institution: Not Entered

Country: Not Entered

Bidirectional Shift Register

Bidirectional Shift Register

VIVA Q2

VIVA Q2

Task2_Half_Adder

Task2_Half_Adder

Task II Full Adder

Task II Full Adder

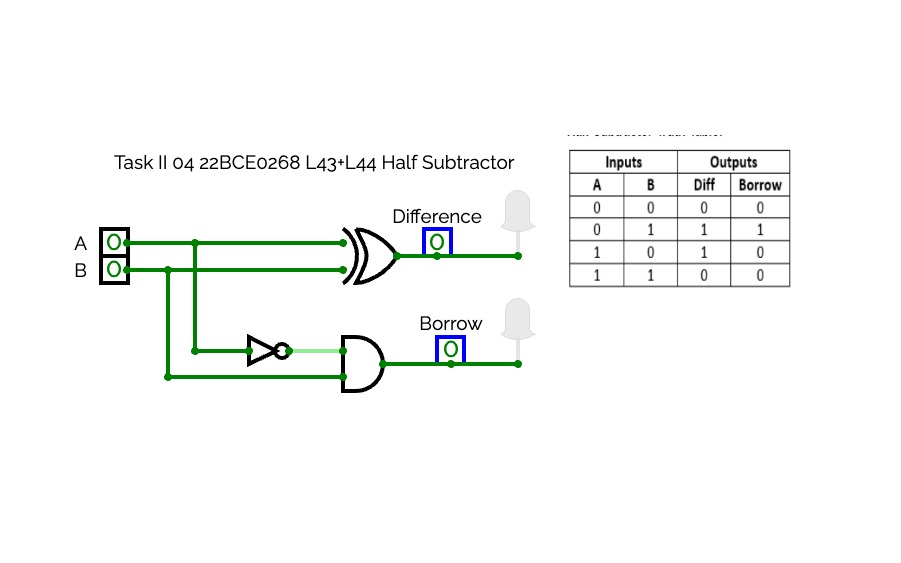

Task II Half Subtrator

Task II Half Subtrator

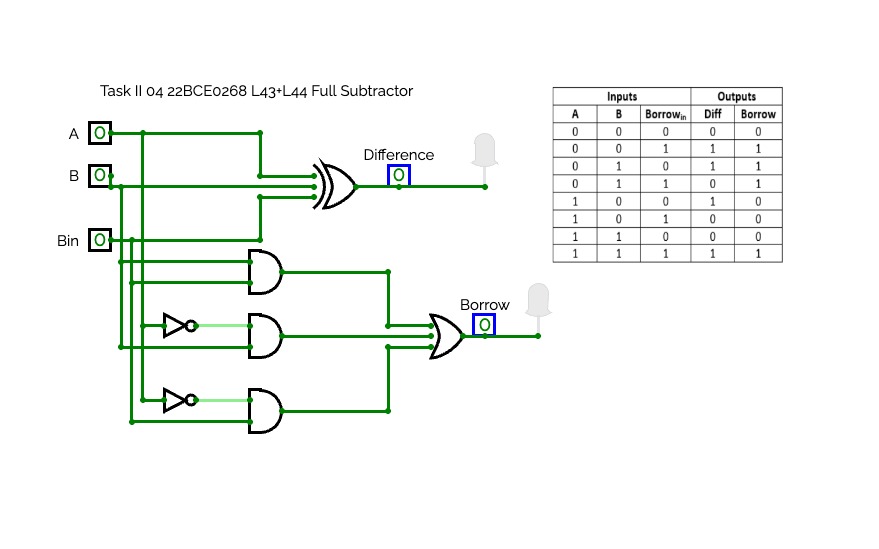

Task II Full Subtractor

Task II Full Subtractor

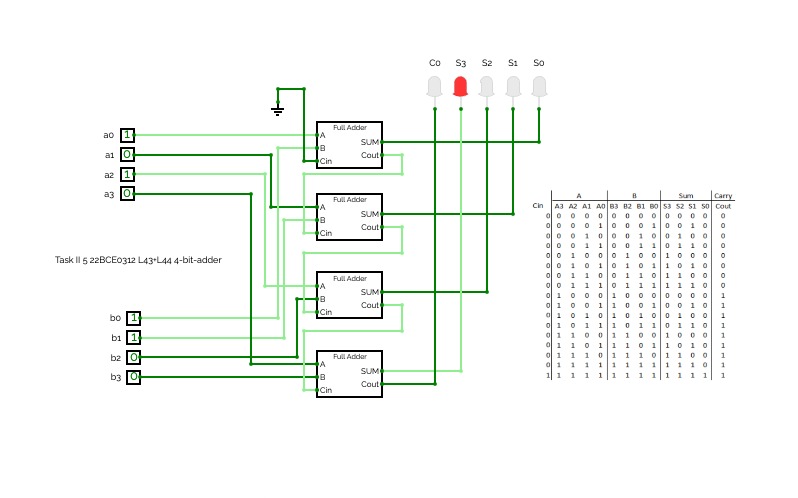

Task II 4-Bit Adder

Task II 4-Bit Adder

Task II 2x2 Multiplier

Task II 2x2 Multiplier

Untitled

Untitled

Untitled

Untitled

TASK1 F'(POS) NOR Implementation

TASK1 F'(POS) NOR Implementation

Task1 F'(SOP) NAND Impementation

Task1 F'(SOP) NAND Impementation

4 Bit ALU

4 Bit ALU

PIPO Shift Register

PIPO Shift Register

SIPO Shift Register

SIPO Shift Register

PIPO Shift Register

PIPO Shift Register

random counter

random counter

cat2 B1 q2

cat2 B1 q2

Untitled

Untitled

B1_Q5

B1_Q5

B2_Q2

B2_Q2

B2_Q4

B2_Q4

B2_Q5

B2_Q5

SISO Shift Register

SISO Shift Register

B1_Q2

B1_Q2

Full Adder Using 4:1 MUX

Full Adder Using 4:1 MUX

2:1 Multiplexer circuit using NOR logic

2:1 Multiplexer circuit using NOR logic

Task 1 POS Active High Logic

Task 1 POS Active High Logic

1Bit ALU

1Bit ALU

POS_MUX

POS_MUX

DA QUES3 MUX

DA QUES3 MUX

DA Q3 POS (OAI)

DA Q3 POS (OAI)

DA QUES 3 DECODER

DA QUES 3 DECODER

Untitled

Untitled

Task 1 using decoder SOP

Task 1 using decoder SOP

Task 1 using 4:16 Decoder POS

Task 1 using 4:16 Decoder POS

Task 1 Multiplexer

Task 1 Multiplexer

2:1 MUX NOR IMPLEMENTATION

2:1 MUX NOR IMPLEMENTATION

2:1 MUX NAND IMPLEMENTATION

2:1 MUX NAND IMPLEMENTATION

Half Adder using 4:1 MUX

Half Adder using 4:1 MUX

Half Adder using 4:1 MUX

Half Adder using 4:1 MUX

Half Subtractor using 4:1 MUX

Half Subtractor using 4:1 MUX

Task 1 using 8:1 MUX

Task 1 using 8:1 MUX

Full adder using 8:1 MUX

Full adder using 8:1 MUX

Full Subtractor using 4:1 MUX

Full Subtractor using 4:1 MUX

Full adder using 8:1 MUX

Full adder using 8:1 MUX

Full Subtractor using 8:1 MUX

Full Subtractor using 8:1 MUX

Untitled

Untitled

B1_Q3

B1_Q3

B2_Q1

B2_Q1

Mod N Counter

Mod N Counter

DA Q3 NAND

DA Q3 NAND

DA Q3 NOR

DA Q3 NOR

DA Q3 POS (OAI)

DA Q3 POS (OAI)

DA QUES 3 DEMUX

DA QUES 3 DEMUX

2:1 MUX POS OAI

2:1 MUX POS OAI

Task 1 SOP Active Low Logic

Task 1 SOP Active Low Logic