Kapadia Om Daxesh 22BCE2051

Member since: 1 year

Educational Institution: Not Entered

Country: Not Entered

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Task1

Task1

Task1

Task1

Task1

Task1

Task1

Task1

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

ren_mo_using_mux

ren_mo_using_mux

Untitled

Untitled

Untitled

Untitled

full and half adder using MUX

full and half adder using MUX

Untitled

Untitled

Untitled

Untitled

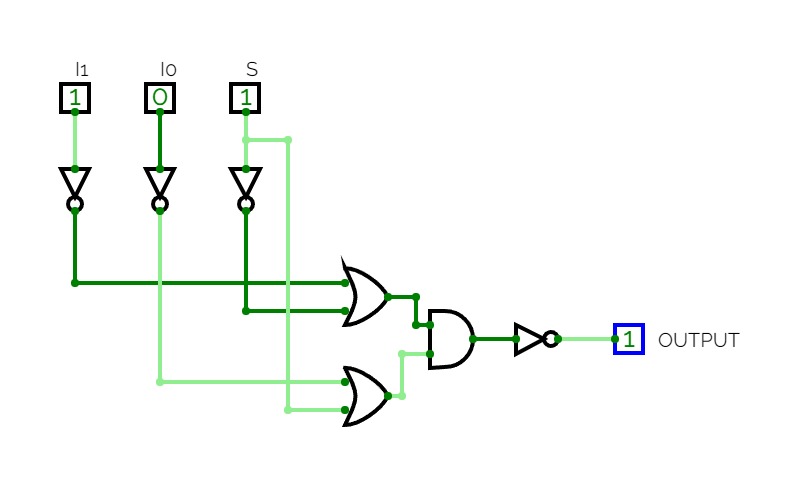

2:1 MUX Circuit using POS Equation

2:1 MUX Circuit using POS Equation

Circuit diagram of 2:1 MUX Circuit using SOP Equation -- AOI circuit

Circuit diagram of 2:1 MUX Circuit using SOP Equation -- AOI circuit

Untitled

Untitled

AOI logic circuit of 2:4 Decoder

AOI logic circuit of 2:4 Decoder

AOI logic circuit of 4:2 encoder

AOI logic circuit of 4:2 encoder

NAND logic circuit of 4:2 encoder

NAND logic circuit of 4:2 encoder

Untitled

Untitled

Untitled

Untitled

b1q1_1

b1q1_1

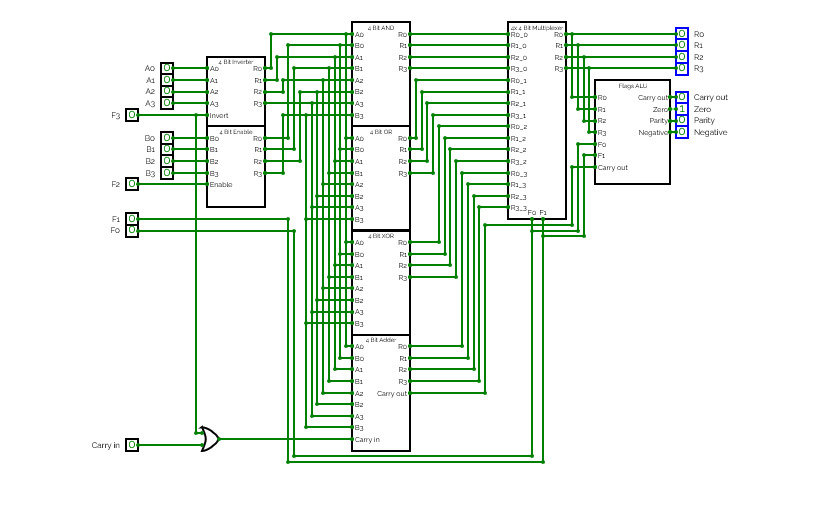

ALU

ALU

ALU

ALU

Untitled

Untitled

Full adder using mux

Full adder using mux

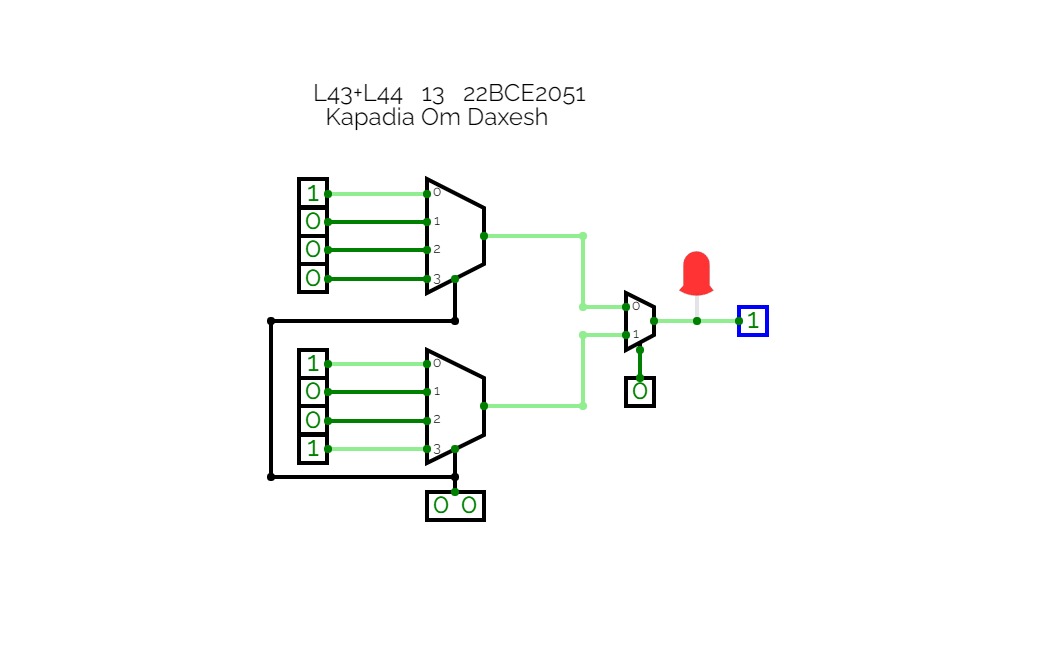

A-13

A-13

Untitled

Untitled

4 Bit ALU 2

4 Bit ALU 2

Untitled

Untitled

SIPO

SIPO

Untitled

Untitled

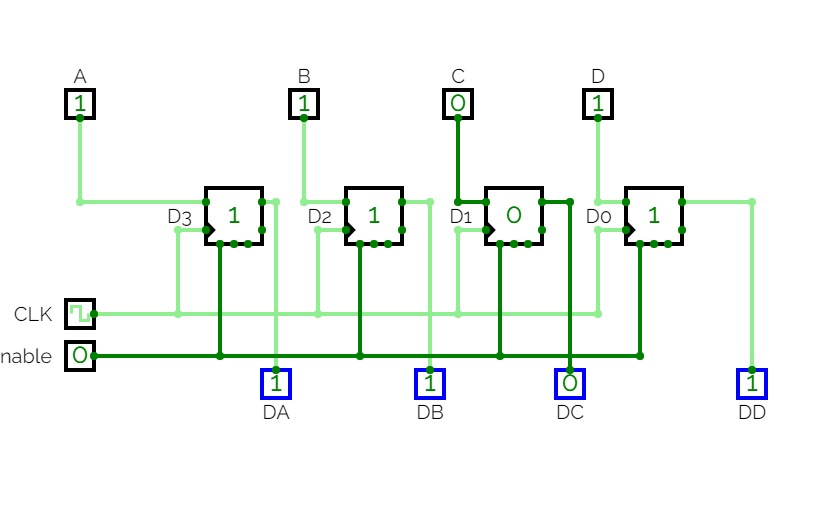

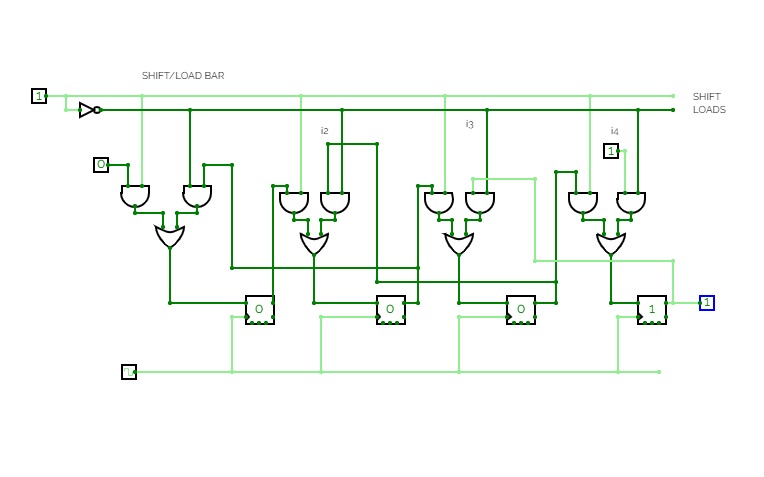

Parallel in Parallel Out Shift Register

Parallel in Parallel Out Shift Register

PIPO

PIPO

PISO SHIFT REGISTER

PISO SHIFT REGISTER

bidirectional shift register

bidirectional shift register

Bidirectional Shift Register

Bidirectional Shift Register

CAT1 B1

CAT1 B1

Untitled

Untitled

Untitled

Untitled

CAT1 B2

CAT1 B2

q1b2_1

q1b2_1

q2b2_1

q2b2_1

q5b2_1

q5b2_1

Untitled

Untitled

q1b2_2

q1b2_2

q3b2_2

q3b2_2

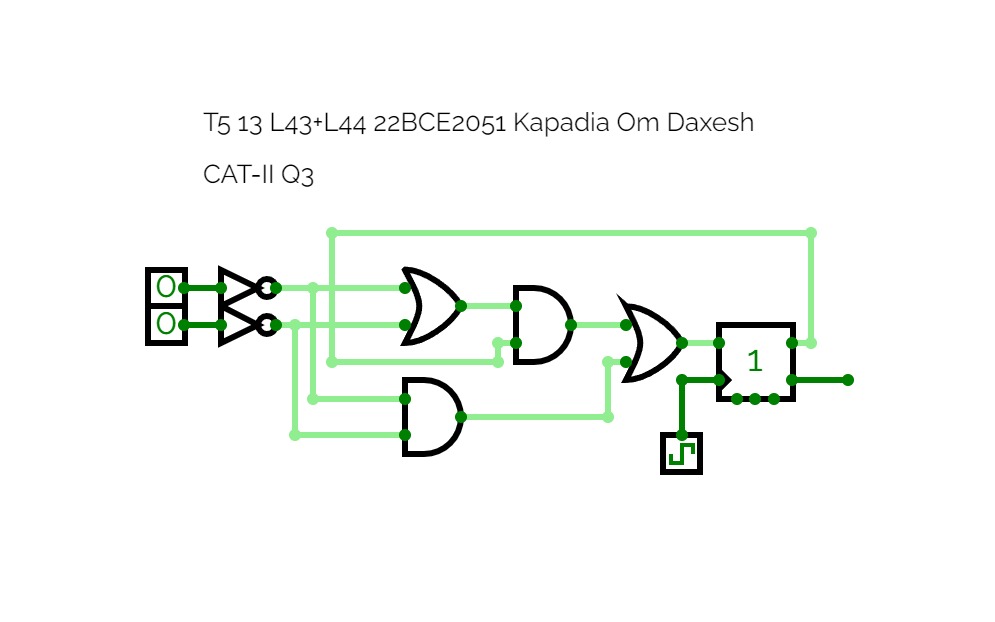

UntitledCAT2B1Q3

UntitledCAT2B1Q3

q3b1_2

q3b1_2

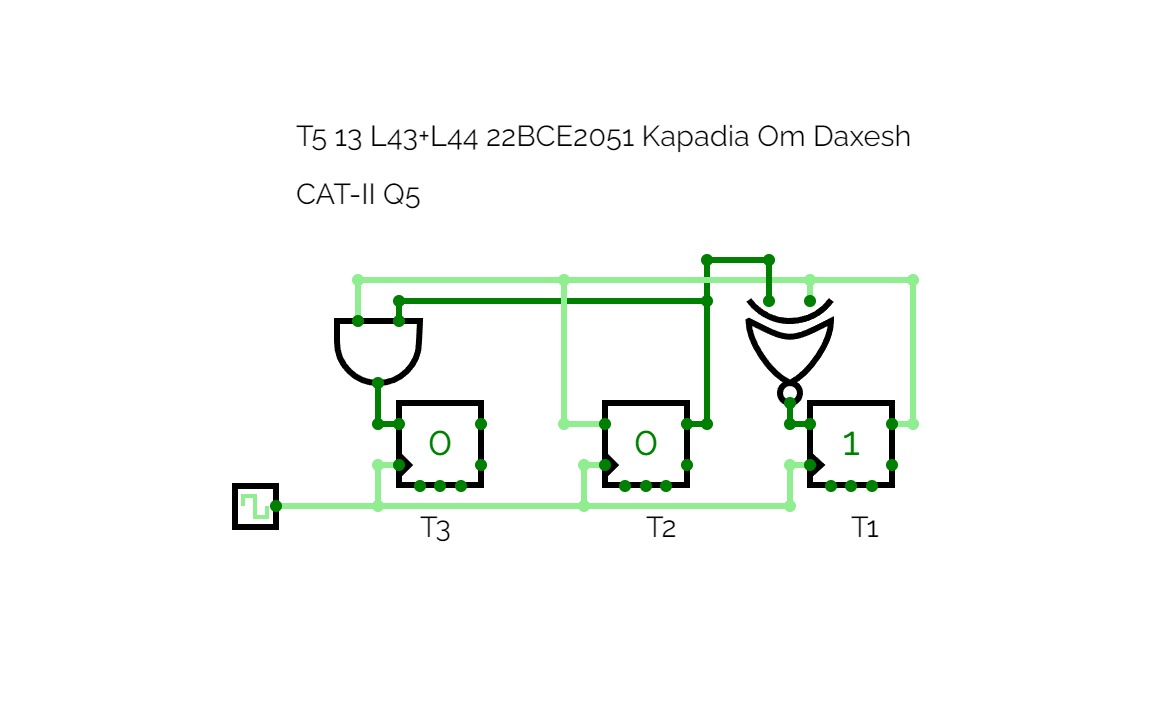

UntitledCAT2B1Q5

UntitledCAT2B1Q5

q5b1_2

q5b1_2

Untitledcat2b2q1

Untitledcat2b2q1

Untitledcat2b2q3

Untitledcat2b2q3

UntitledCAT2B2Q5

UntitledCAT2B2Q5

q4b2_2

q4b2_2

q5b2_2

q5b2_2

reg_no_16:1 mux

reg_no_16:1 mux

Full Subtractor using 3 to 8 Decoder

Full Subtractor using 3 to 8 Decoder

HALF ADDER USING MUX

HALF ADDER USING MUX

HALF SUBTRACTOR USING MUX

HALF SUBTRACTOR USING MUX

full subtractor using mux

full subtractor using mux

full adder using decoder

full adder using decoder

Untitled

Untitled

Circuit diagram of 2:1 MUX Circuit using SOP Equation -- NAND circuit:

Circuit diagram of 2:1 MUX Circuit using SOP Equation -- NAND circuit:

Untitled

Untitled

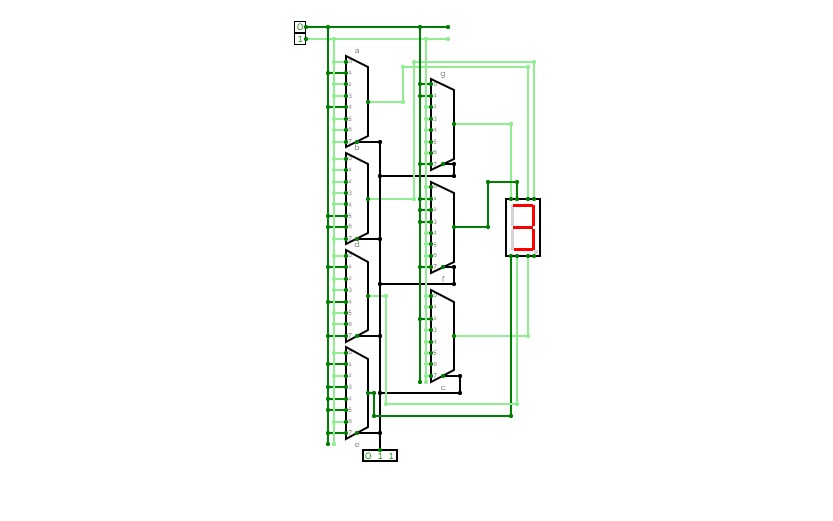

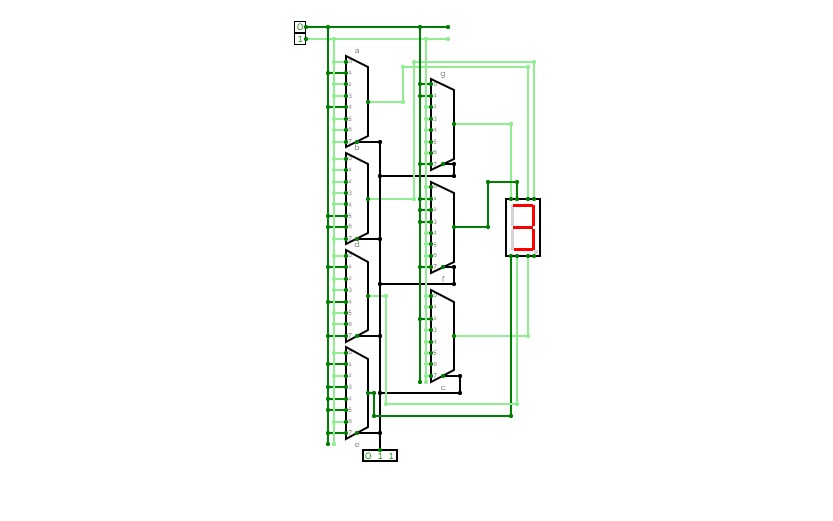

7 segment display using 8x1 mux

7 segment display using 8x1 mux

7 segment display using 8x1 mux

7 segment display using 8x1 mux

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

7 segment display using 1:16 decoder

7 segment display using 1:16 decoder

Untitled

Untitled

7 segment display using 1:16 decoder

7 segment display using 1:16 decoder

Untitled

Untitled

Untitled

Untitled

7 segment display using 8x1 mux

7 segment display using 8x1 mux

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

q2b1_2

q2b1_2

Untitled

Untitled

q4b1_2

q4b1_2

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Q3_hw

Q3_hw

Que4_hw

Que4_hw

1:4 DEMUX using 1:2 DEMUX

1:4 DEMUX using 1:2 DEMUX

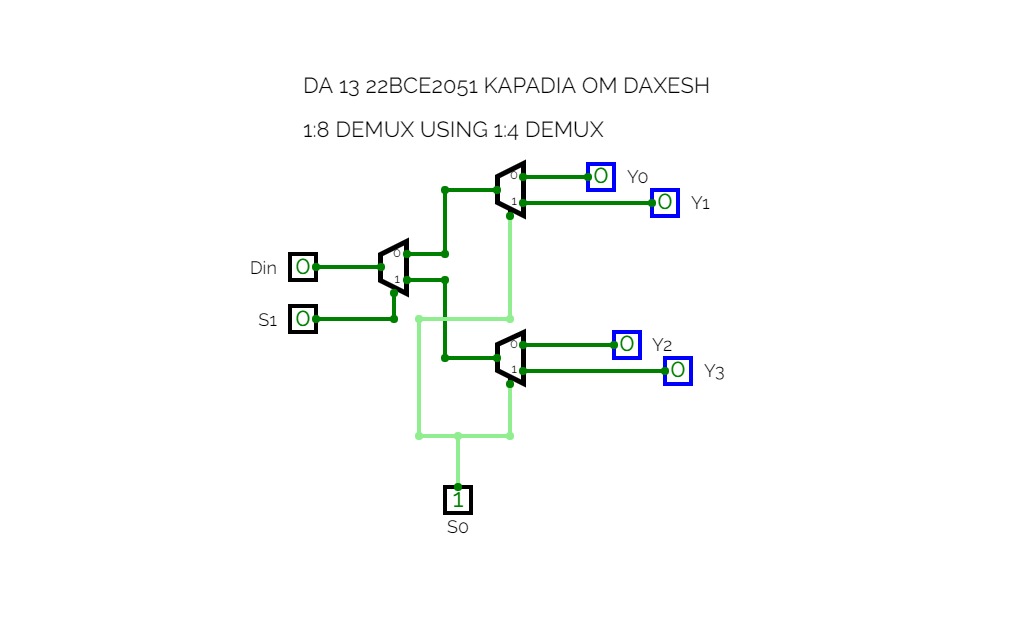

3*8 DECODER USING TWO 2*4 DECODERS

3*8 DECODER USING TWO 2*4 DECODERS

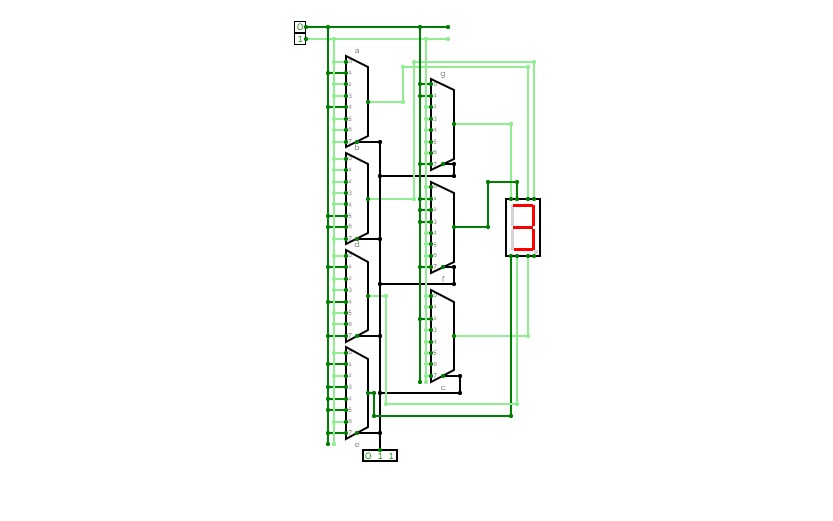

1:8 DEMUX using 1:4 DEMUX

1:8 DEMUX using 1:4 DEMUX

MUX

MUX

Untitled

Untitled

Design Complementor using DeMultiplexer

Design Complementor using DeMultiplexer

2:1 Multiplexer using Decoder

2:1 Multiplexer using Decoder

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

q4b2_1

q4b2_1

Serial In Serial Out Shift Register - D flip flop

Serial In Serial Out Shift Register - D flip flop

Untitled

Untitled

7 segment display using 1:16 decoder

7 segment display using 1:16 decoder

Full Adder using 2, 4*1 MUX

Full Adder using 2, 4*1 MUX

mux using 8:1

mux using 8:1

q5b1_1

q5b1_1

one bit DR ALU

one bit DR ALU

DE MTE

DE MTE

Half Adder Using 2x4 Decoder

Half Adder Using 2x4 Decoder

NAND logic circuit of 2:4 Decoder

NAND logic circuit of 2:4 Decoder

4 bit SIPO Shift Register

4 bit SIPO Shift Register

1-BIT ALU CIRCUIT

1-BIT ALU CIRCUIT