S.Varun

Member since: 1 year

Educational Institution: Not Entered

Country: Not Entered

Task 2 03 L43+L44 Full Adder

Task 2 03 L43+L44 Full Adder

TASK 2 03 L43+L44 Half Adder

TASK 2 03 L43+L44 Half Adder

Task 2 03 L43+L44 4 Bit Adder

Task 2 03 L43+L44 4 Bit Adder

SISO Shift Register 03 22BCE0220 S.Varun L43+L44

SISO Shift Register 03 22BCE0220 S.Varun L43+L44

SIPO Shift Register 03 22BCE0220 S.Varun L43+L44

SIPO Shift Register 03 22BCE0220 S.Varun L43+L44

random counter 03 22BCE0220 S.Varun L43+L44

random counter 03 22BCE0220 S.Varun L43+L44

PIPO Shift Register 03 22BCE0220 S.Varun L43+L44

PIPO Shift Register 03 22BCE0220 S.Varun L43+L44

Bidirectional Shift Register

Bidirectional Shift Register

cat2b1q1 _03_L43_L44_22BCE0220

cat2b1q1 _03_L43_L44_22BCE0220

cat1 b1 q1

cat1 b1 q1

cat1b2q1_03_L43_L44_22BCE0220

cat1b2q1_03_L43_L44_22BCE0220

cat1b2q1

cat1b2q1

cat1b2q1

cat1b2q1

TASK 2 03 L43+L44 3x3 Multiplier

TASK 2 03 L43+L44 3x3 Multiplier

TASK 2 03 L43+L44 4x4 Multiplier

TASK 2 03 L43+L44 4x4 Multiplier

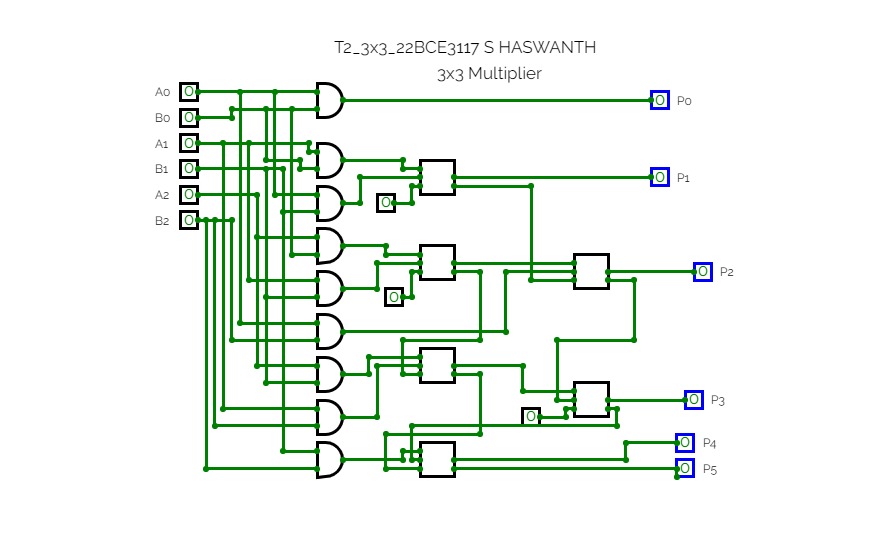

T2_3x3_22BCE3117_S Haswanth

T2_3x3_22BCE3117_S Haswanth

T2_4x4_22BCE3117_S Haswanth

T2_4x4_22BCE3117_S Haswanth

Task 2 03 FS 22BCE0220 S.Varun

Task 2 03 FS 22BCE0220 S.Varun

Task 2 03 HS 22BCE0220 S.Varun

Task 2 03 HS 22BCE0220 S.Varun

TASK 1 03 L43+L44 22BCE0220 S.Varun SOP F

TASK 1 03 L43+L44 22BCE0220 S.Varun SOP F

TASK 1 03 L43-L44 22BCE0220 S.Varun SOP F'

TASK 1 03 L43-L44 22BCE0220 S.Varun SOP F'

Untitled

Untitled

cat1b1q2

cat1b1q2

FA using the 4:1 MUX 03 22BCE0220 L43+L44

FA using the 4:1 MUX 03 22BCE0220 L43+L44

FS using the 4:1 MUX 03 22BCE0220 L43+L44

FS using the 4:1 MUX 03 22BCE0220 L43+L44

8:1 Using The 4:1 MUX 03 22BCE0220 L43+L44

8:1 Using The 4:1 MUX 03 22BCE0220 L43+L44

SOP on the MUX 03 22BCE0220 L43+L44

SOP on the MUX 03 22BCE0220 L43+L44

FA using the 8:1 MUX 03 22BCE0220 L43+L44

FA using the 8:1 MUX 03 22BCE0220 L43+L44

FS using the 8:1 MUX 03 22BCE0220 L43+L44

FS using the 8:1 MUX 03 22BCE0220 L43+L44

SOP using the 4:1 MUX 03 22BCE0220 L43+L44

SOP using the 4:1 MUX 03 22BCE0220 L43+L44

cat2 b2 q1 _03_L43_L44_22BCE0220

cat2 b2 q1 _03_L43_L44_22BCE0220

cat1 b1 q1 _03_L43_L44_22BCE0220

cat1 b1 q1 _03_L43_L44_22BCE0220

2:1 MUX using the SOP equation 03 22BCE0220 L43+L44

2:1 MUX using the SOP equation 03 22BCE0220 L43+L44

2:1 MUX using the POS NOR 03 22BCE0220 L43+L44

2:1 MUX using the POS NOR 03 22BCE0220 L43+L44

POS using the 4:1 MUX 03 22BCE0220 L43+L44

POS using the 4:1 MUX 03 22BCE0220 L43+L44

POS 16:1 MUX 03 22BCE0220 L43+L44

POS 16:1 MUX 03 22BCE0220 L43+L44

2x1_Multiplexer_NAND_03_22BCE0220_S.Varun_L43_L44_HOTVIVA_Q1

2x1_Multiplexer_NAND_03_22BCE0220_S.Varun_L43_L44_HOTVIVA_Q1

AOI logic circuit of 2:4 decoder 03 22BCE0220 L43+L44

AOI logic circuit of 2:4 decoder 03 22BCE0220 L43+L44

NAND logic circuit of 4:2 encoder 03 22BCE0220 L43+L44

NAND logic circuit of 4:2 encoder 03 22BCE0220 L43+L44

Half adder using Decoder 03 22BCE0220 L43+L44

Half adder using Decoder 03 22BCE0220 L43+L44

Half subtractor using Decoder 03 22BCE0220 L43+L44

Half subtractor using Decoder 03 22BCE0220 L43+L44

16:1 Using The 8:1 MUX 03 22BCE0220 S.Varun L43+L44

16:1 Using The 8:1 MUX 03 22BCE0220 S.Varun L43+L44

DA Q3 SOP (AOI)

DA Q3 SOP (AOI)

DA Q3 POS (OAI)

DA Q3 POS (OAI)

DA Q3 NAND

DA Q3 NAND

DA QUES 3 DEMUX

DA QUES 3 DEMUX

DA QUES 3 DECODER

DA QUES 3 DECODER

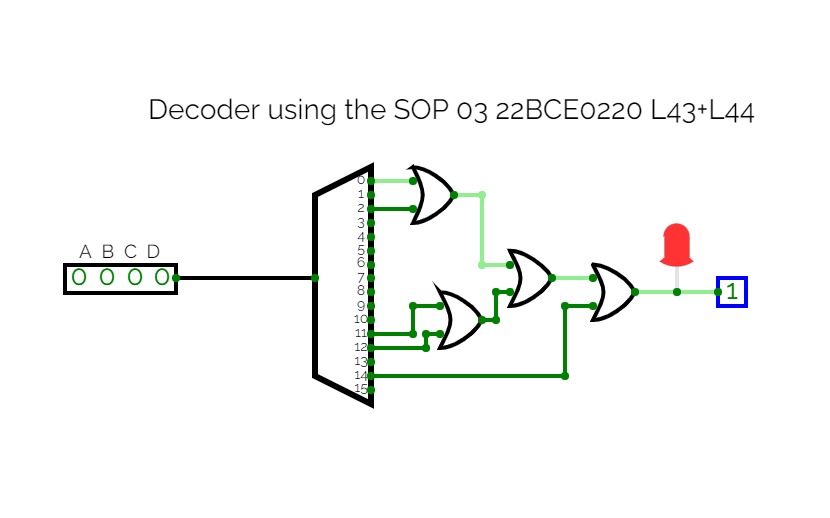

Decoder using the SOP 03 22BCE0220 L43+L44

Decoder using the SOP 03 22BCE0220 L43+L44

4:1 Using The 2:1 MUX 03 22BCE0220 L43+L44

4:1 Using The 2:1 MUX 03 22BCE0220 L43+L44

cat2b1q1

cat2b1q1

cat1b2q1

cat1b2q1

B2 Q4 CAT1 03 22BCE0220 S.Varun L43+L44

B2 Q4 CAT1 03 22BCE0220 S.Varun L43+L44

DA QUES 3 DECODER

DA QUES 3 DECODER

DA QUES3 MUX

DA QUES3 MUX

TASK 1 03 L43-L44 22BCE0220 S.Varun POS F'

TASK 1 03 L43-L44 22BCE0220 S.Varun POS F'

2:1 using the POS equation 03 22BCE0220 L43+L44

2:1 using the POS equation 03 22BCE0220 L43+L44

CAT1 B1 Q2 03 22BCE0220 S.Varun L43+L44

CAT1 B1 Q2 03 22BCE0220 S.Varun L43+L44

Full adder using Decoder 03 22BCE0220 L43+L44

Full adder using Decoder 03 22BCE0220 L43+L44

SOP 16:1 MUX 03 22BCE0220 L43+L44

SOP 16:1 MUX 03 22BCE0220 L43+L44

POS using the MUX 03 22BCE0220 L43+L44

POS using the MUX 03 22BCE0220 L43+L44

2:1 MUX using the SOP NAND equation 03 22CE0220 L43+L44

2:1 MUX using the SOP NAND equation 03 22CE0220 L43+L44

Decoder_To_NOR_Implementation_03_22BCE0220_S.Varun_HOTVIVA_Q2

Decoder_To_NOR_Implementation_03_22BCE0220_S.Varun_HOTVIVA_Q2

NAND logic circuit of 2:4 decoder 03 22BCE0220 L43+L44

NAND logic circuit of 2:4 decoder 03 22BCE0220 L43+L44

Full subtractor using Decoder 03 22BCE0220 L43+L44

Full subtractor using Decoder 03 22BCE0220 L43+L44

Mod N Counter 03 22BCE0220 S.Varun L43+L44

Mod N Counter 03 22BCE0220 S.Varun L43+L44

CAT1 B2 Q2 cat1 b2 q2 03 22BCE0220 S.Varun L43+L44

CAT1 B2 Q2 cat1 b2 q2 03 22BCE0220 S.Varun L43+L44

DA Q3 NOR

DA Q3 NOR

AOI logic circuit of 4:2 encoder 03 22BCE0220 L43+L44

AOI logic circuit of 4:2 encoder 03 22BCE0220 L43+L44