Nitin S 22BCE3344

Member since: 1 year

Educational Institution: Not Entered

Country: Not Entered

Full Adder using 4:1 MUX

Full Adder using 4:1 MUX

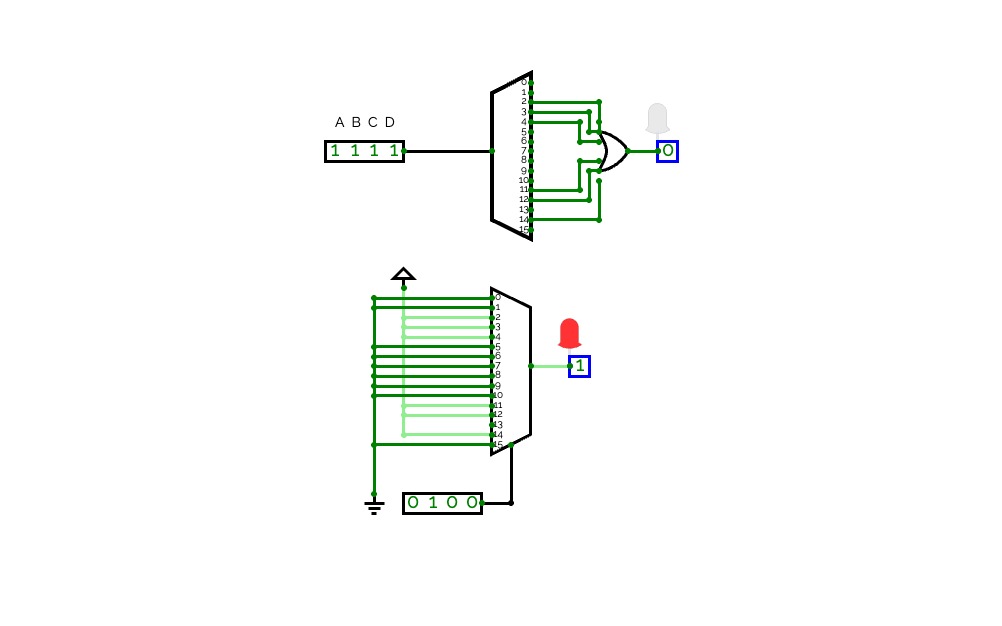

CAT 2 B2 Q3

CAT 2 B2 Q3

CAT 2 B2 Q5

CAT 2 B2 Q5

HA

HA

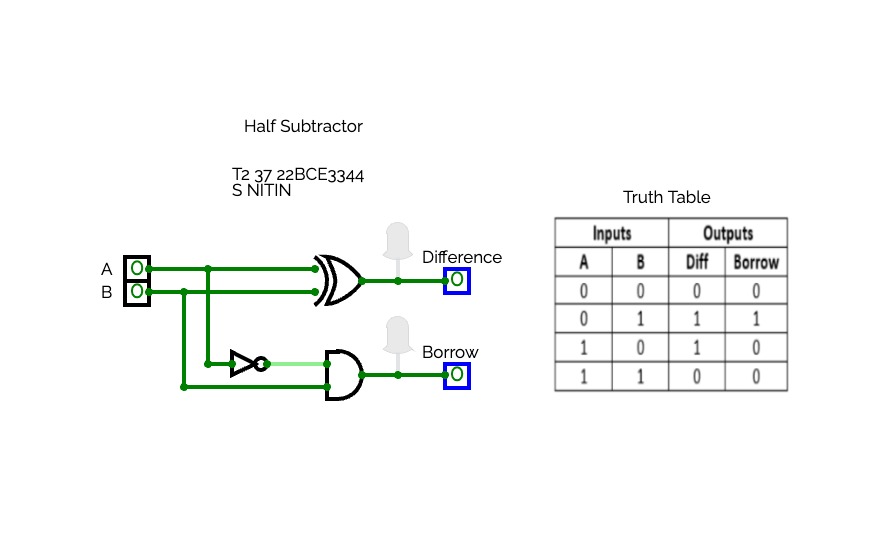

HS

HS

FA

FA

FS

FS

3*3 multi

3*3 multi

2*2 multi

2*2 multi

4*4 multi

4*4 multi

4 Bit adder

4 Bit adder

f sop nand

f sop nand

f sop nor

f sop nor

f' sop nor

f' sop nor

f' sop nand

f' sop nand

f pos nor

f pos nor

f pos nand

f pos nand

f sop

f sop

f sop

f sop

f sop

f sop

f' sop

f' sop

f pos nand

f pos nand

f' pos

f' pos

4 Bit SISO Shift Register

4 Bit SISO Shift Register

4 Bit SIPO Shift Register

4 Bit SIPO Shift Register

4 BIT PISO SHIFT REGISTER

4 BIT PISO SHIFT REGISTER

4 Bit PIPO Shift Register

4 Bit PIPO Shift Register

CAT 1 B2 Q1

CAT 1 B2 Q1

BCD to 4321 using NOR Logic with dc

BCD to 4321 using NOR Logic with dc

BCD to 4321 using NAND logic with dc

BCD to 4321 using NAND logic with dc

4 BIT ALU NIT

4 BIT ALU NIT

BCD to 4321 without dc

BCD to 4321 without dc

NAND logic circuit of 2:4 Decoder

NAND logic circuit of 2:4 Decoder

AOI logic circuit of 2:4 Decoder

AOI logic circuit of 2:4 Decoder

AOI logic circuit of 4:2 encoder

AOI logic circuit of 4:2 encoder

NAND logic circuit of 4:2 encoder

NAND logic circuit of 4:2 encoder

F SOP using decoder

F SOP using decoder

F POS using Decoder

F POS using Decoder

Half adder using Decoder

Half adder using Decoder

4:1 MUX using AOI

4:1 MUX using AOI

CAT 1 B1 Q2

CAT 1 B1 Q2

f' pos nand

f' pos nand

8:1 MUX A - SL

8:1 MUX A - SL

8:1 MUX B - SL

8:1 MUX B - SL

Full Subtractor using 8:1 MUX

Full Subtractor using 8:1 MUX

4:1 MUX SOP

4:1 MUX SOP

4:1 MUX POS

4:1 MUX POS

Half Adder using 4:1 MUX

Half Adder using 4:1 MUX

Half Subtractor using 4:1 MUX

Half Subtractor using 4:1 MUX

Full Subtractor using 4:1 MUX

Full Subtractor using 4:1 MUX

2:1 MUX POS

2:1 MUX POS

Full Adder using 8:1 MUX

Full Adder using 8:1 MUX

POS MUX Circuit

POS MUX Circuit

2:1 MUX SOP

2:1 MUX SOP

SOP MUX Circuit

SOP MUX Circuit

2:1 MUX NAND

2:1 MUX NAND

2:1 MUX NOR

2:1 MUX NOR

16:1 MUX SOP

16:1 MUX SOP

16:1 MUX POS

16:1 MUX POS

Full adder using Decoder

Full adder using Decoder

Half subtractor using Decoder

Half subtractor using Decoder

Full subtractor using Decoder

Full subtractor using Decoder

Full Adder USING FA

Full Adder USING FA

full adder

full adder

f' pos nor

f' pos nor

decoder

decoder

CAT 2 B1 Q5

CAT 2 B1 Q5

CAT 2 B2 Q1

CAT 2 B2 Q1

Bidirectional Shift Register

Bidirectional Shift Register

MOD 10 Counter

MOD 10 Counter

CAT 1 B1 Q1

CAT 1 B1 Q1

CAT I B1 Q4

CAT I B1 Q4

CAT 1 B2 Q4

CAT 1 B2 Q4

CAT 2 B2 Q4

CAT 2 B2 Q4

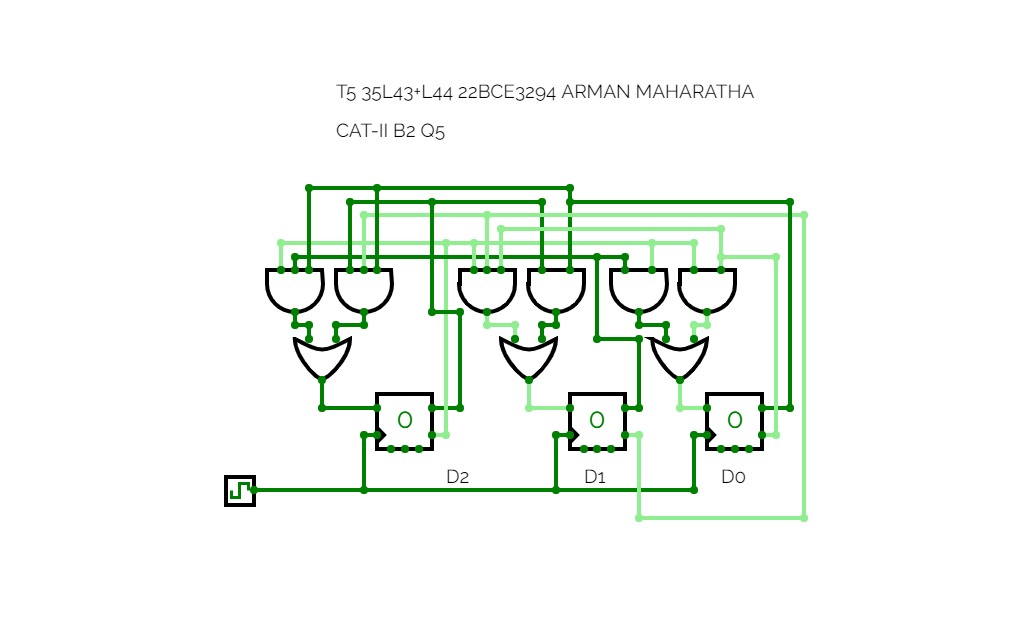

CAT-2 B2 Q5

CAT-2 B2 Q5

f' sop nor

f' sop nor

f pos

f pos

BCD to 4321 POS without dc

BCD to 4321 POS without dc

BCD to 4321 using MUX with Don't Care

BCD to 4321 using MUX with Don't Care

BCD to 4321 using DeMultiplexer with Don't Care

BCD to 4321 using DeMultiplexer with Don't Care

BCD to 4321 using Decoder with Don't Care

BCD to 4321 using Decoder with Don't Care

CAT 1 B2 Q2

CAT 1 B2 Q2

CAT 1 B2 Q5

CAT 1 B2 Q5

Decoder Task 2

Decoder Task 2

BCD to 4321 using AOI Logic with Don't Care

BCD to 4321 using AOI Logic with Don't Care

BCD to 4321 using OAI Logic with Don't Care

BCD to 4321 using OAI Logic with Don't Care

CAT 1 B1 Q5

CAT 1 B1 Q5

bcd to gray code converter using 16x1 mux

bcd to gray code converter using 16x1 mux

CAT 2 B1 Q3

CAT 2 B1 Q3

4 BIT ALU

4 BIT ALU