Yashasvi Verma 22BCE2504

Member since: 1 year

Educational Institution: VIT VELLORE

Country: India

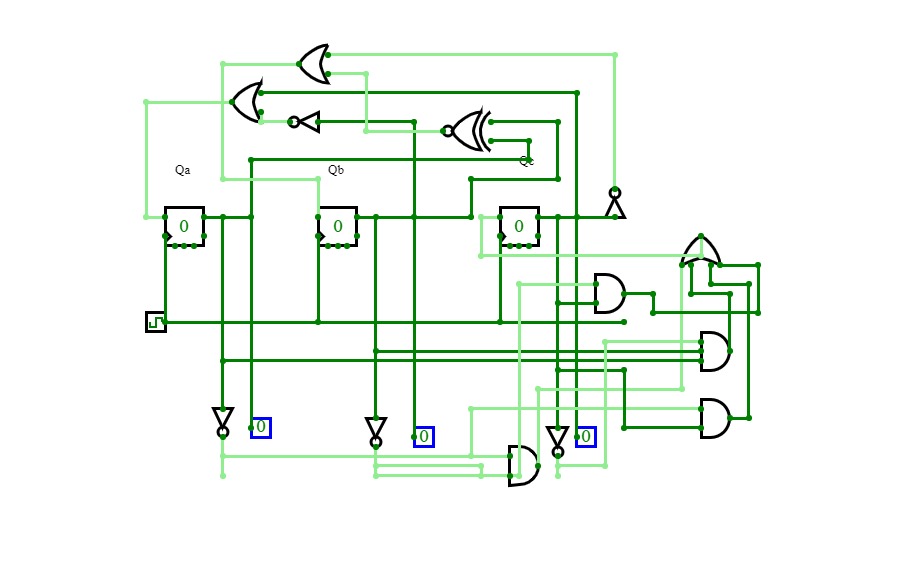

random counter

random counter

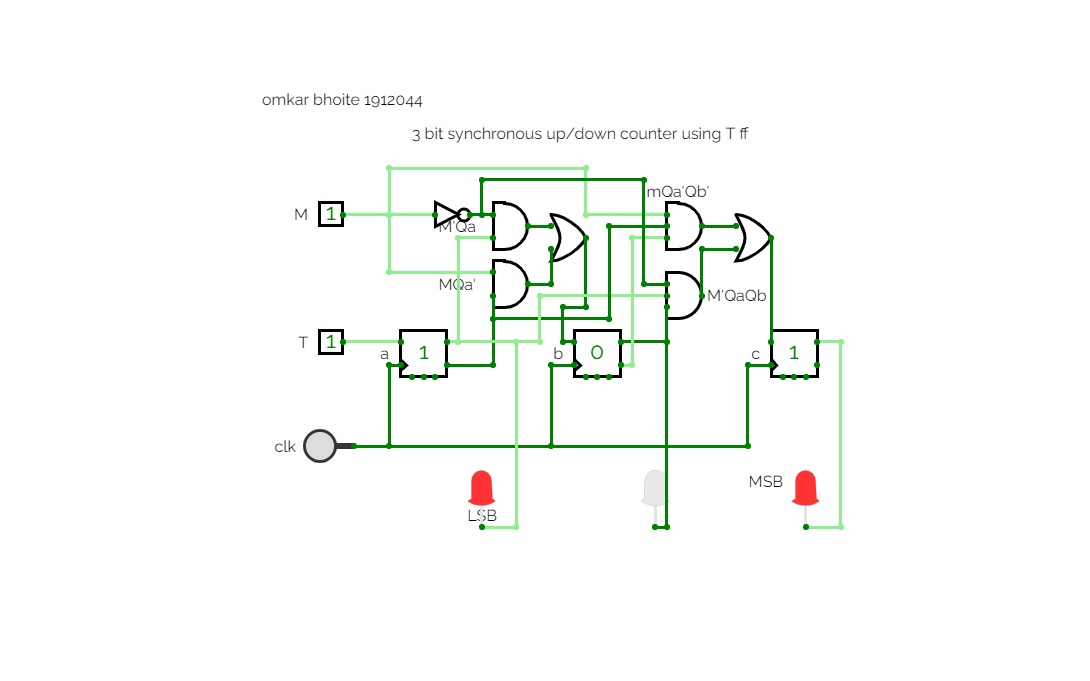

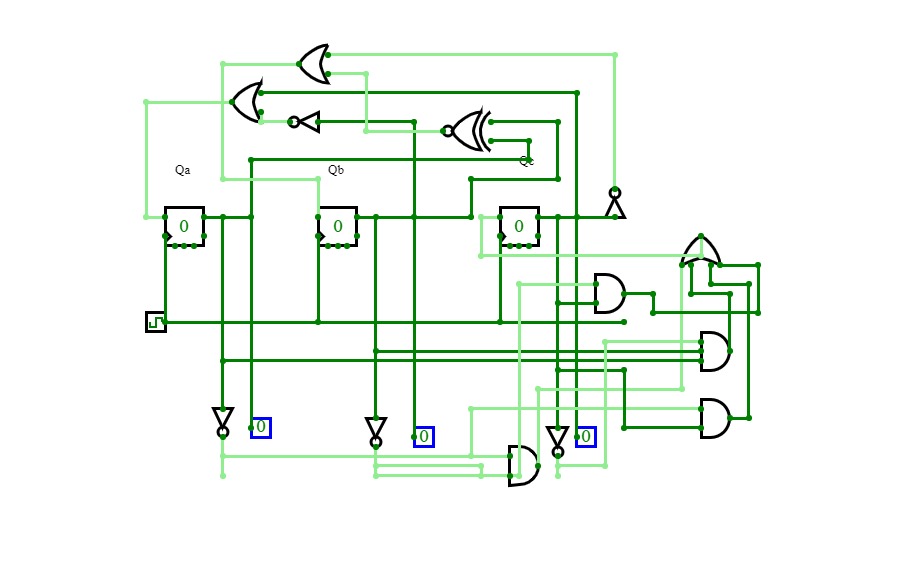

3 bit synchronous up/down counter using T flipflop

3 bit synchronous up/down counter using T flipflop

RANDON counter

RANDON counter

MOD n counter

MOD n counter

4 -BIT Adder

4 -BIT Adder

Mux for (b) y1

Mux for (b) y1

Mux for (b) y1

Mux for (b) y1

Mux for (B) y2

Mux for (B) y2

Full Adder

Full Adder

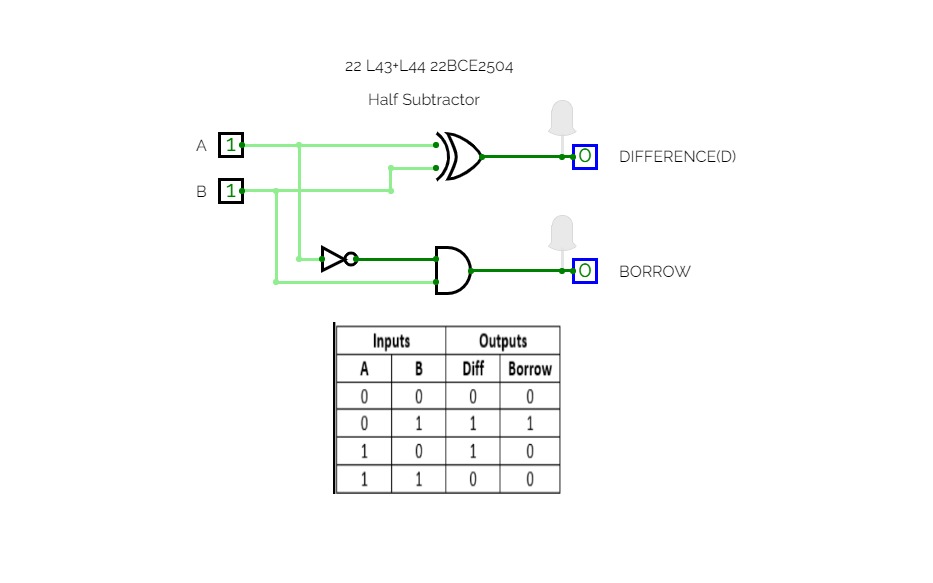

Half Subtractor

Half Subtractor

Full Subtractor

Full Subtractor

SOP expression Using MUX

SOP expression Using MUX

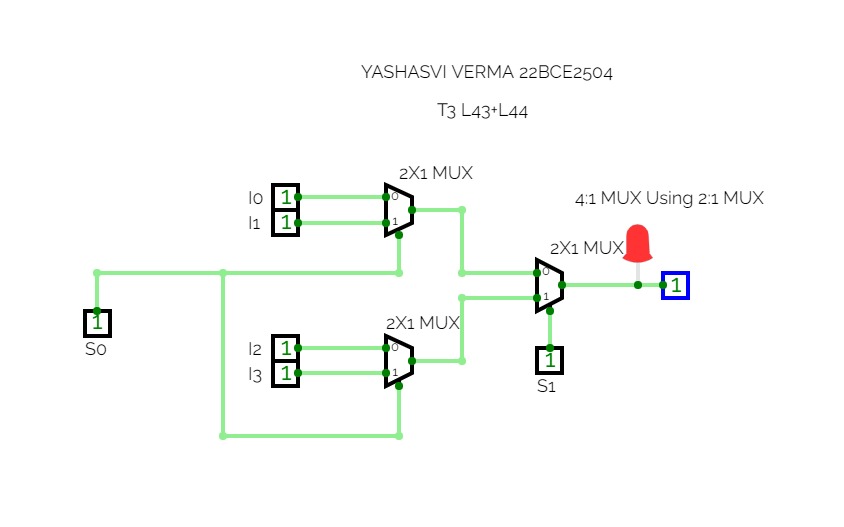

4:1 Mux Using 2:1 Mux

4:1 Mux Using 2:1 Mux

8:1 USING 4:1

8:1 USING 4:1

Multiplexer Based Circuit Using 8:1 MUX

Multiplexer Based Circuit Using 8:1 MUX

AOI logic circuit of 2:4 Decoder

AOI logic circuit of 2:4 Decoder

NAND logic circuit of 2:4 Decoder

NAND logic circuit of 2:4 Decoder

NAND logic circuit of 4:2 encoder

NAND logic circuit of 4:2 encoder

Task I (SOP) implemented using Decoder Active Low logic

Task I (SOP) implemented using Decoder Active Low logic

POS Expression Using MUX

POS Expression Using MUX

Homework Q18

Homework Q18

Q2 java 2

Q2 java 2

q2 dsd 1

q2 dsd 1

1 BIT ALU

1 BIT ALU

7 Segment Decoder common cathode

7 Segment Decoder common cathode

Task I (POS) implemented using Decoder Active High logic

Task I (POS) implemented using Decoder Active High logic

Circuit verse link for code convertor circuit using NAND logic

Circuit verse link for code convertor circuit using NAND logic

Circuit verse link for code convertor circuit using NOR logic

Circuit verse link for code convertor circuit using NOR logic

Hot Question 2 mux (a)

Hot Question 2 mux (a)

SISO SIPO

SISO SIPO

PISO PIPO

PISO PIPO

Bi-Directional Shift Registers

Bi-Directional Shift Registers

CAT-1 Q1

CAT-1 Q1

CAT-1 Q2

CAT-1 Q2

CAT-1 Q4

CAT-1 Q4

CAT1 Q5

CAT1 Q5

CAT1 Q1 B2

CAT1 Q1 B2

CAT1 B2 Q2

CAT1 B2 Q2

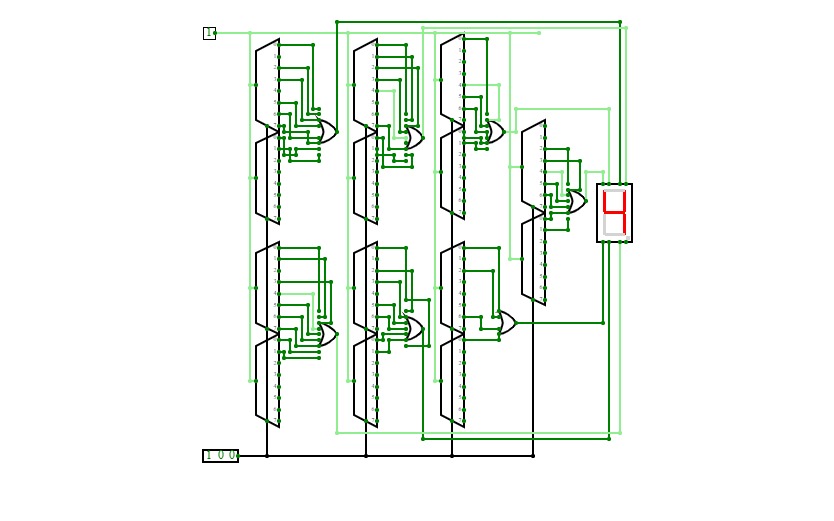

Binary to 7 Segment

Binary to 7 Segment

Q3_2_2

Q3_2_2

Untitled

Untitled

Untitled

Untitled

CAT1 B2 Q4

CAT1 B2 Q4

Half Adder

Half Adder

CAT1 B2 Q5

CAT1 B2 Q5

CAT2 B1 Q3

CAT2 B1 Q3

CAT2 B1 Q5

CAT2 B1 Q5

CAT2 B2 Q1

CAT2 B2 Q1

CAT2 B2 Q3

CAT2 B2 Q3

CAT2 B2 Q4

CAT2 B2 Q4

DA Q9_1

DA Q9_1

DA Q9_2

DA Q9_2

7 segment display using 1:16 demux

7 segment display using 1:16 demux

Q9_3 DA

Q9_3 DA

7 segment display using 4:16 decoder

7 segment display using 4:16 decoder

7 segment display using 3:8 decoder

7 segment display using 3:8 decoder

CAT2 B2 Q5

CAT2 B2 Q5

Circuit vese code convertor circuit link using Multiplexer

Circuit vese code convertor circuit link using Multiplexer

Circuit vese code convertor circuit link using Demultiplexer

Circuit vese code convertor circuit link using Demultiplexer

CAT2 B1 Q4

CAT2 B1 Q4

CAT2 B2 Q2

CAT2 B2 Q2

AOI Logic Circuit

AOI Logic Circuit

Decoder for reg. no.

Decoder for reg. no.

Mux for reg. no.

Mux for reg. no.

Circuit Diagram Using 2:1 MUX NOR

Circuit Diagram Using 2:1 MUX NOR

4 BIT ADDER

4 BIT ADDER

Viva Q1

Viva Q1

Hot Question 2 dec (a)

Hot Question 2 dec (a)

CAT 2 B1 Q4

CAT 2 B1 Q4

da q8 a

da q8 a

q8 da b

q8 da b

7 Seg Decoder COMMON ANODE

7 Seg Decoder COMMON ANODE

DA 3_2_2

DA 3_2_2

Binary to 7 Segment COMMON ANODE

Binary to 7 Segment COMMON ANODE

7 Seg Decoder COMMON CATHODE

7 Seg Decoder COMMON CATHODE

DA 3_1_1

DA 3_1_1

random counter

random counter

Circuit Diagram Using 2:1 MUX NAND

Circuit Diagram Using 2:1 MUX NAND

Multiplexer based circuit implemented using 4:1 Multiplexer

Multiplexer based circuit implemented using 4:1 Multiplexer

Circuit vese code convertor circuit link using OAI logic

Circuit vese code convertor circuit link using OAI logic

AOI logic circuit

AOI logic circuit

Circuit Diagram Using 2:1 MUX AOI

Circuit Diagram Using 2:1 MUX AOI

Binary to 7 Segment

Binary to 7 Segment

Task I (POS) implemented using Decoder Active Low logic

Task I (POS) implemented using Decoder Active Low logic

cat 2 b1 q2

cat 2 b1 q2

7 segment display 1:16 demux using 1:8 demux

7 segment display 1:16 demux using 1:8 demux

Task I (SOP) implemented using Decoder Active High logic

Task I (SOP) implemented using Decoder Active High logic

DA Q6

DA Q6

7 segment display using 3:8 decoder

7 segment display using 3:8 decoder

AOI logic circuit of 4:2 encoder

AOI logic circuit of 4:2 encoder

Circuit verse link for code convertor circuit using AOI logic

Circuit verse link for code convertor circuit using AOI logic

Circuit vese code convertor circuit link using Decoder

Circuit vese code convertor circuit link using Decoder

7 segment display using 1:16 demux

7 segment display using 1:16 demux

16:1 USING 8:1

16:1 USING 8:1

7 segment display using 4:16 decoder

7 segment display using 4:16 decoder

Circuit Diagram Using POS equation OAI

Circuit Diagram Using POS equation OAI