Sachin Diwakar 22BKT0079

Member since: 1 year

Educational Institution: Not Entered

Country: Not Entered

CAT1. B1. Q4

CAT1. B1. Q4

CAT1. B1. Q5

CAT1. B1. Q5

CAT1. B2. Q1

CAT1. B2. Q1

CAT2. B2. Q4

CAT2. B2. Q4

CAT1. B1. Q1

CAT1. B1. Q1

CAT2. B1. Q4

CAT2. B1. Q4

NAND implementation of 4:2 decoder

NAND implementation of 4:2 decoder

AOI Implementation of 4:2 Encoder

AOI Implementation of 4:2 Encoder

Implementing AOI Circuit of 2:4 decoder

Implementing AOI Circuit of 2:4 decoder

Implementing SOP(F) using Decoder

Implementing SOP(F) using Decoder

Implementing POS(F) using Decoder

Implementing POS(F) using Decoder

Implementing Full Subtracter using Decoder

Implementing Full Subtracter using Decoder

Implementing Half Subtractor using Decoder

Implementing Half Subtractor using Decoder

Half Adder(POS)

Half Adder(POS)

Half Adder(NOR)

Half Adder(NOR)

Half Adder(NAND)

Half Adder(NAND)

Full Adder(SOP)

Full Adder(SOP)

Full Subtractor(SOP)

Full Subtractor(SOP)

Multiplier

Multiplier

Half Subtractor(POS)

Half Subtractor(POS)

Untitled

Untitled

4 - bit Adder

4 - bit Adder

Half Subtractor(NAND)

Half Subtractor(NAND)

SOP F(AOI) - 22BKT0079

SOP F(AOI) - 22BKT0079

SOP F'(AOI) - 22BKT0079

SOP F'(AOI) - 22BKT0079

POS F(AOI)

POS F(AOI)

POS F'(AOI)

POS F'(AOI)

POS F(OAI)

POS F(OAI)

ZZ

ZZ

POS F'(OAI)

POS F'(OAI)

SOP F(OAI)

SOP F(OAI)

SOP F'(OAI)

SOP F'(OAI)

SOP F(NAND)

SOP F(NAND)

SOP F'(NAND)

SOP F'(NAND)

POS F(NAND)

POS F(NAND)

SOP F'(NAND)

SOP F'(NAND)

Half Adder(NOR)

Half Adder(NOR)

CAT2. B2. Q1

CAT2. B2. Q1

Task-3-MUX-SOP(F)

Task-3-MUX-SOP(F)

Task-3-MUX-POS(f)

Task-3-MUX-POS(f)

AOI CIrcuit of 2X1 MUX using SOP

AOI CIrcuit of 2X1 MUX using SOP

NAND Circuit using of 2X1 MUX using SOP

NAND Circuit using of 2X1 MUX using SOP

NOR Circuit of 2X1 MUX using POS

NOR Circuit of 2X1 MUX using POS

3-bit Even Parity Checker

3-bit Even Parity Checker

Implementing Full Subtractor using 8:1 MUX

Implementing Full Subtractor using 8:1 MUX

1-bit ALU using Full Adder

1-bit ALU using Full Adder

4-BIT ALU

4-BIT ALU

Viva Task - 2

Viva Task - 2

Untitled

Untitled

Untitled

Untitled

Implementing bit-converter using decoder(16X1)

Implementing bit-converter using decoder(16X1)

Implementing bit-converter using demultiplexor

Implementing bit-converter using demultiplexor

Implementing Synchronous Mod-9 Counter using T-flip-flop

Implementing Synchronous Mod-9 Counter using T-flip-flop

4-bit Shift Register(SISO)

4-bit Shift Register(SISO)

Untitled

Untitled

decoder

decoder

Mux-based(Mine)

Mux-based(Mine)

MUX-based

MUX-based

OAI Circuit of 2X1 MUX using POS

OAI Circuit of 2X1 MUX using POS

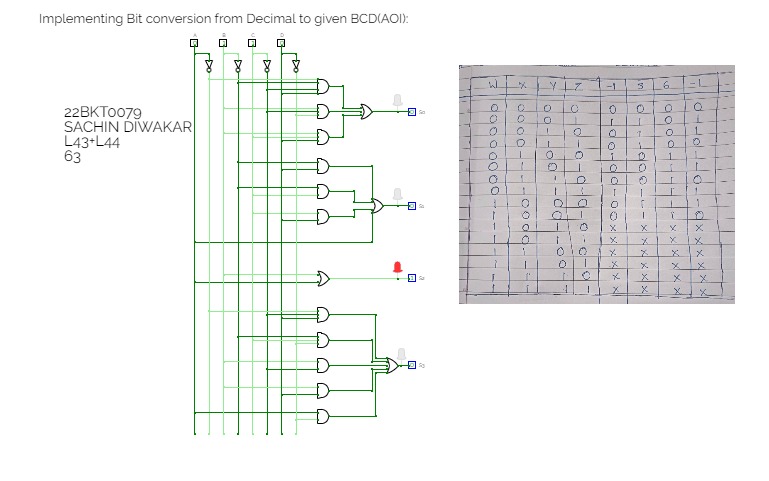

Implementing Bit conversion from Decimal to given BCD(AOI)

Implementing Bit conversion from Decimal to given BCD(AOI)

Implementing Bit conversion from Decimal to given BCD(OAI)

Implementing Bit conversion from Decimal to given BCD(OAI)

Implementing Bit conversion from Decimal to given BCD(NAND)

Implementing Bit conversion from Decimal to given BCD(NAND)

Implementing Bit conversion from Decimal to given BCD(NOR)

Implementing Bit conversion from Decimal to given BCD(NOR)

CAT2. B2. Q2. Implement given sequential circuit

CAT2. B2. Q2. Implement given sequential circuit

CAT1. B1. Q2

CAT1. B1. Q2

CAT2. B2. Q5

CAT2. B2. Q5

CAT2. B2. Q2

CAT2. B2. Q2

CAT2. B2. Q3

CAT2. B2. Q3

Implementing Full Adder using Decoder

Implementing Full Adder using Decoder

Implementing bit-conversion using Multiplexor(8X1)

Implementing bit-conversion using Multiplexor(8X1)

CAT2. B2. Q4

CAT2. B2. Q4

CAT1. B2. Q5

CAT1. B2. Q5

Implementing Half-Adder using Decoder

Implementing Half-Adder using Decoder