Patel Anujkumar Amitbhai 22BCE2157

Member since: 1 year

Educational Institution: Not Entered

Country: Not Entered

Untitled

Untitled

code_converter_1324_mux

code_converter_1324_mux

code_converter_1324_decoder

code_converter_1324_decoder

code_convertor_decoder

code_convertor_decoder

full_subtractor

full_subtractor

Untitled

Untitled

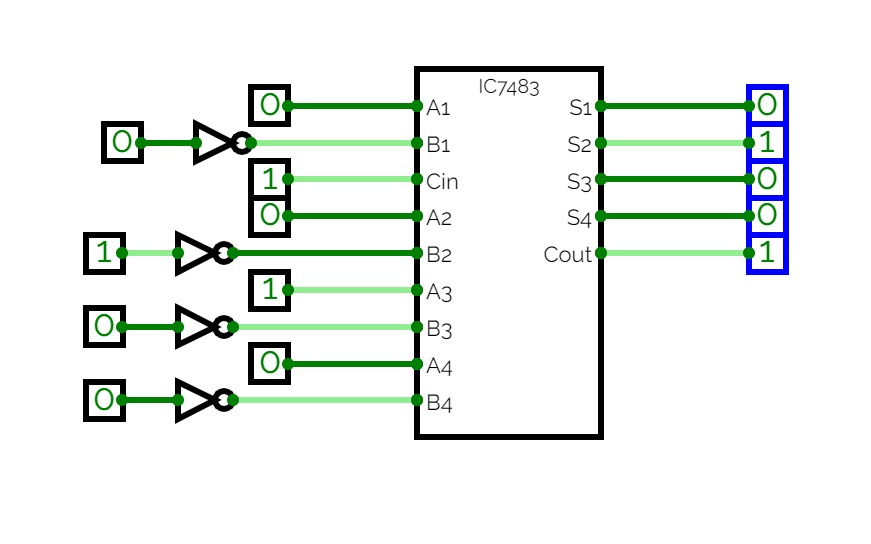

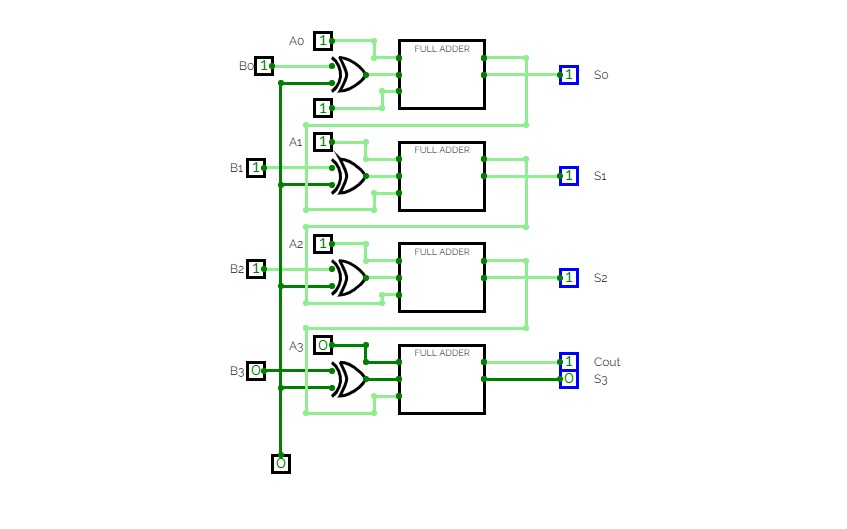

4-Bit Adder

4-Bit Adder

4-Bit Adder

4-Bit Adder

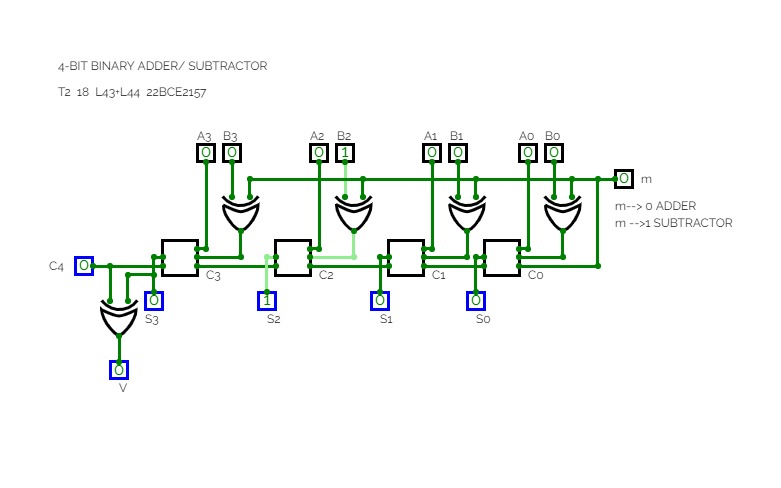

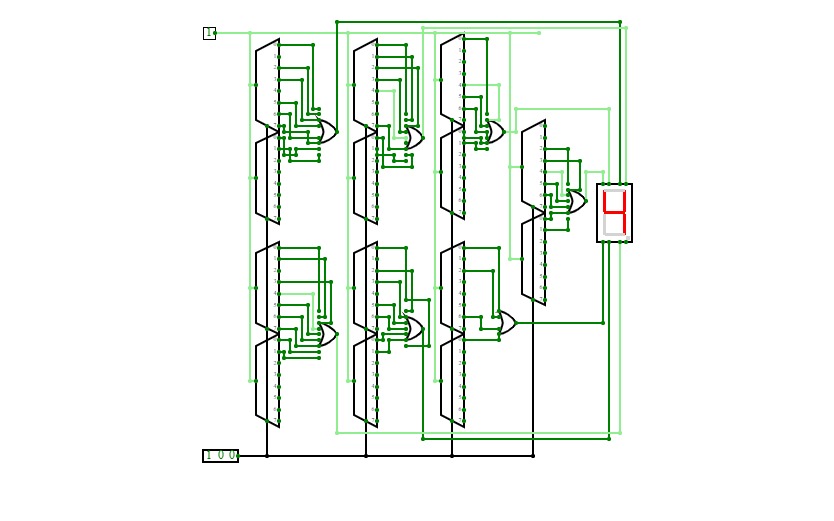

4-bit parallel adder/subtractor

4-bit parallel adder/subtractor

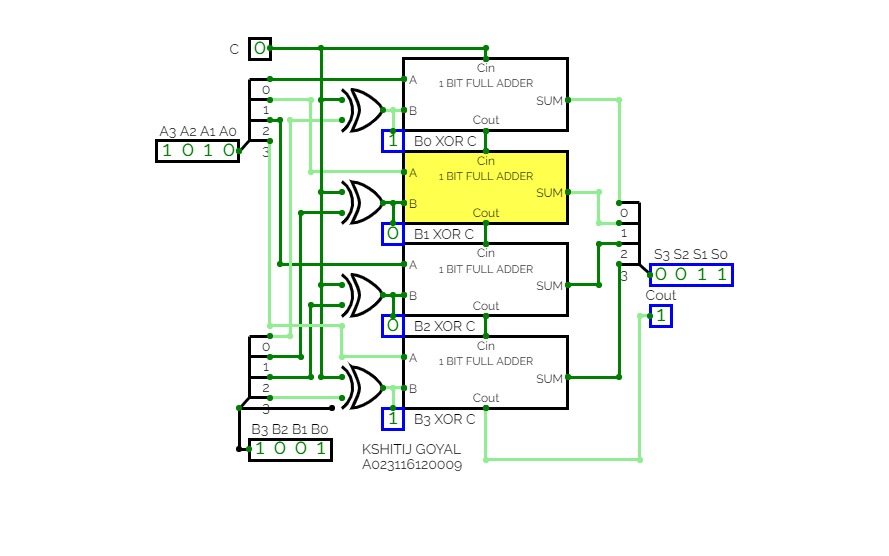

4 BIT FULL ADDER

4 BIT FULL ADDER

Untitled

Untitled

4*4 Array Multiplier

4*4 Array Multiplier

3X3 Multiplier

3X3 Multiplier

Untitled

Untitled

half_adder

half_adder

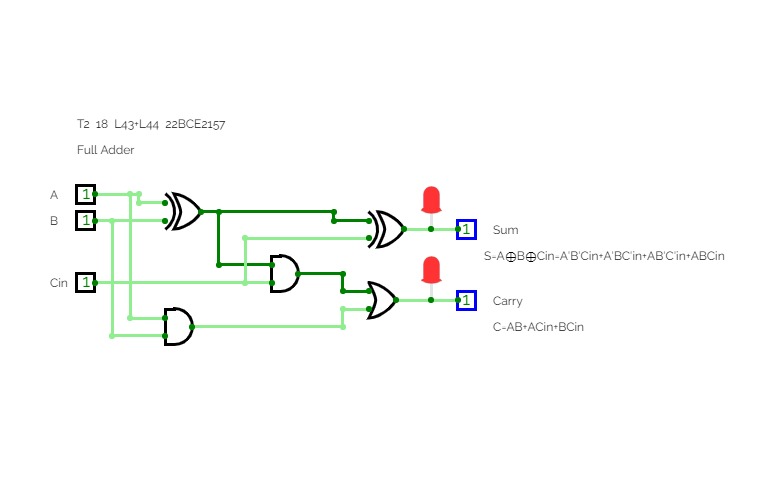

Full_adder

Full_adder

Untitled

Untitled

Untitled

Untitled

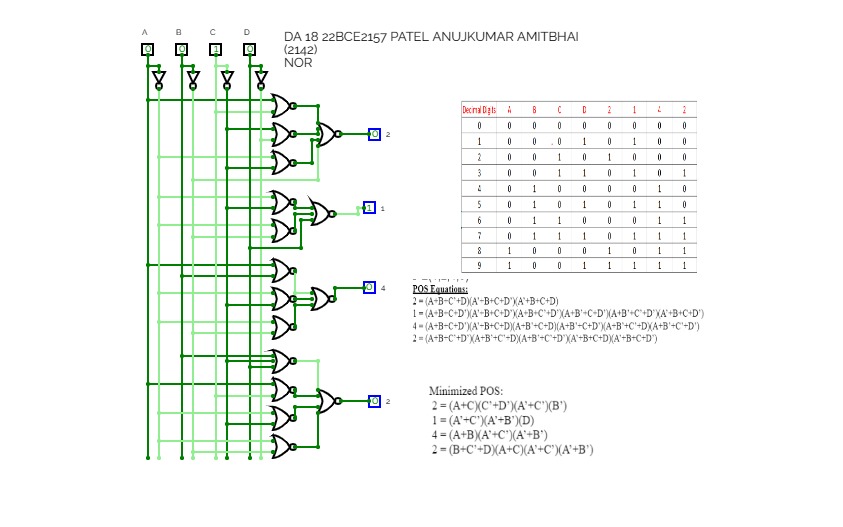

POS_NOR

POS_NOR

sop_nand

sop_nand

UntitledCAT2B1Q3

UntitledCAT2B1Q3

DSD_TASK2

DSD_TASK2

Untitled

Untitled

16:1 MUX using 8:1 MUX

16:1 MUX using 8:1 MUX

Untitled

Untitled

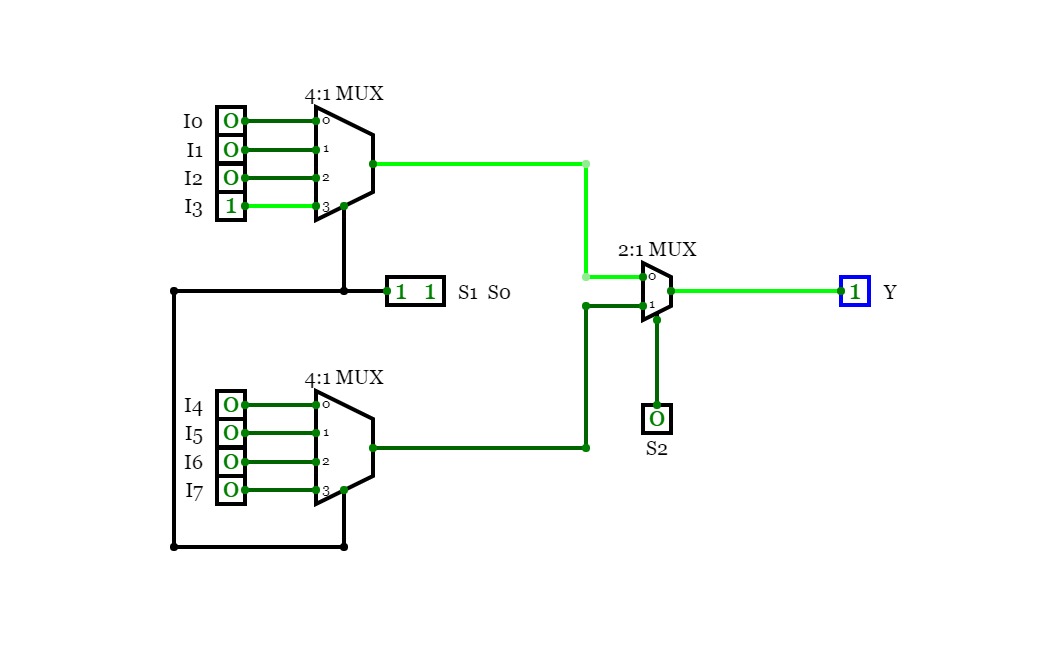

8:1 MUX using 4:1 MUX & 2:1 MUX

8:1 MUX using 4:1 MUX & 2:1 MUX

2:1 MUX Circuit using SOP Equation

2:1 MUX Circuit using SOP Equation

AOI logic circuit of 4:2 encoder

AOI logic circuit of 4:2 encoder

1x16 decoder

1x16 decoder

NAND logic circuit of 2:4 Decoder

NAND logic circuit of 2:4 Decoder

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

CAT1 B1

CAT1 B1

q1

q1

Untitled

Untitled

q5

q5

CAT1 B2

CAT1 B2

4 Bit Binary Adder/Subtractor

4 Bit Binary Adder/Subtractor

Untitled

Untitled

ALU

ALU

AOI logic circuit of 2:4 Decoder

AOI logic circuit of 2:4 Decoder

UntitledCAT2B1Q5

UntitledCAT2B1Q5

3 BIT MAGNITUDE COMPARATOR

3 BIT MAGNITUDE COMPARATOR

Untitledcat2b2q1

Untitledcat2b2q1

Untitledcat2b2q3

Untitledcat2b2q3

Untitledcat2b2q4

Untitledcat2b2q4

UntitledCAT2B2Q5

UntitledCAT2B2Q5

SISO and SIPO

SISO and SIPO

siso_sipo_shiftreg

siso_sipo_shiftreg

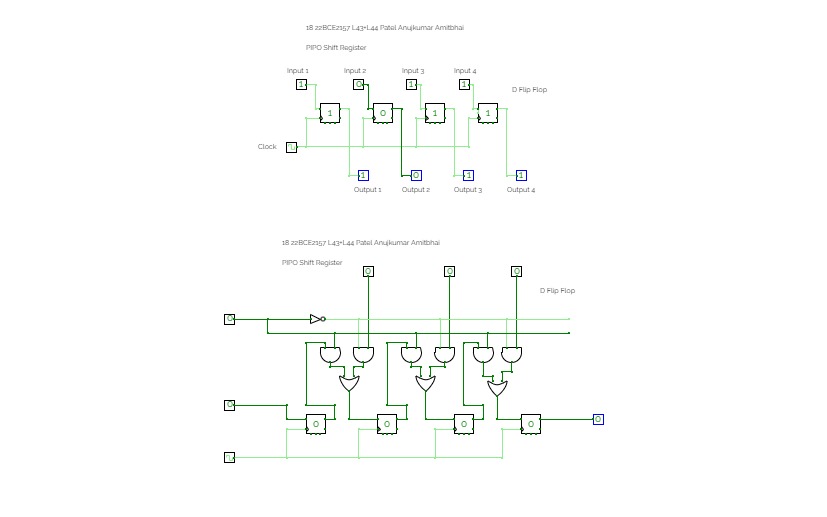

PISO SHIFT REGISTER

PISO SHIFT REGISTER

Untitled

Untitled

pipo_piso_shiftreg

pipo_piso_shiftreg

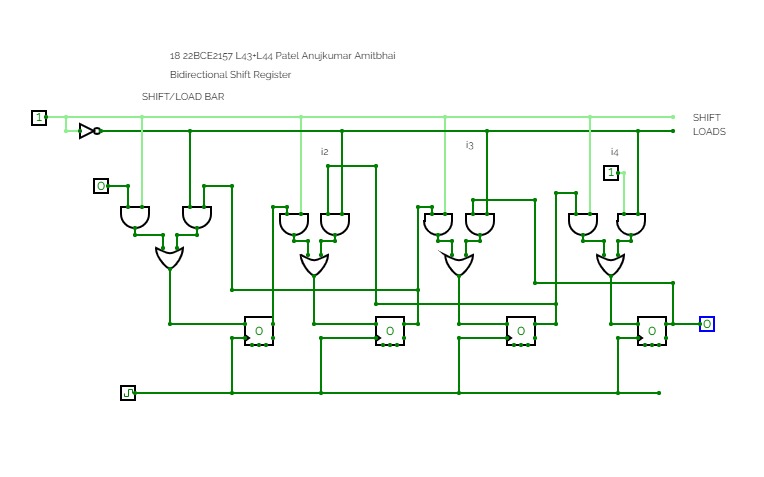

bidirectional shift register

bidirectional shift register

Untitled

Untitled

bidirectional_shiftreg

bidirectional_shiftreg

Untitled

Untitled

b1q1_1

b1q1_1

q1b1_1

q1b1_1

Untitled

Untitled

q4b1_1

q4b1_1

q5b2_1

q5b2_1

Untitled

Untitled

q2b2_1

q2b2_1

q4b2_1

q4b2_1

q2b2_1

q2b2_1

q2b2_1

q2b2_1

q5b2_1

q5b2_1

Untitled

Untitled

Full adder using 2 pcs 8x1 multiplexer

Full adder using 2 pcs 8x1 multiplexer

4x1 MUltiplexer Using 2x1 MUX

4x1 MUltiplexer Using 2x1 MUX

Untitled

Untitled

HALF ADDER USING MUX

HALF ADDER USING MUX

Untitled

Untitled

Untitled

Untitled

half subtractor using mux

half subtractor using mux

full adder using decoder

full adder using decoder

decoder

decoder

SOP canonical expression of MUX and circuit implemented in MUX

SOP canonical expression of MUX and circuit implemented in MUX

Untitled

Untitled

Untitled

Untitled

8x1 multiplexer using two 4x1 and one 2x1

8x1 multiplexer using two 4x1 and one 2x1

da q8 a

da q8 a

INTERNALCIRCUITUSING2:1MUX

INTERNALCIRCUITUSING2:1MUX

DAQ3SOP

DAQ3SOP

Untitled

Untitled

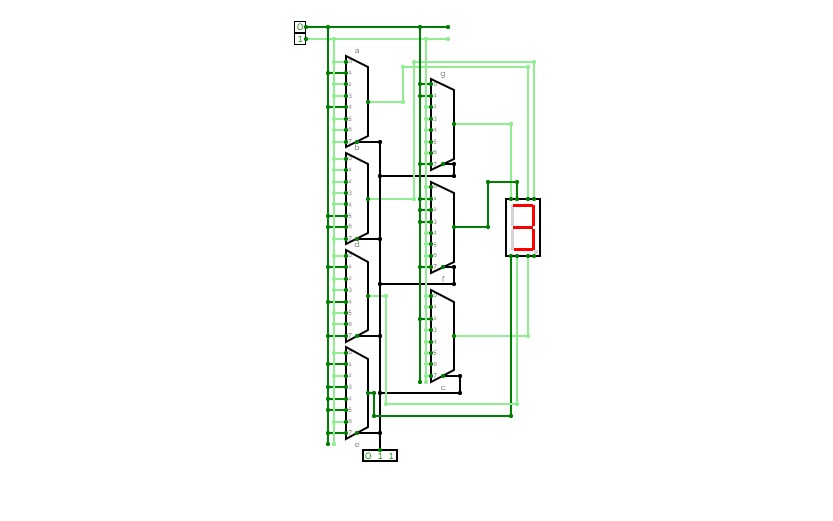

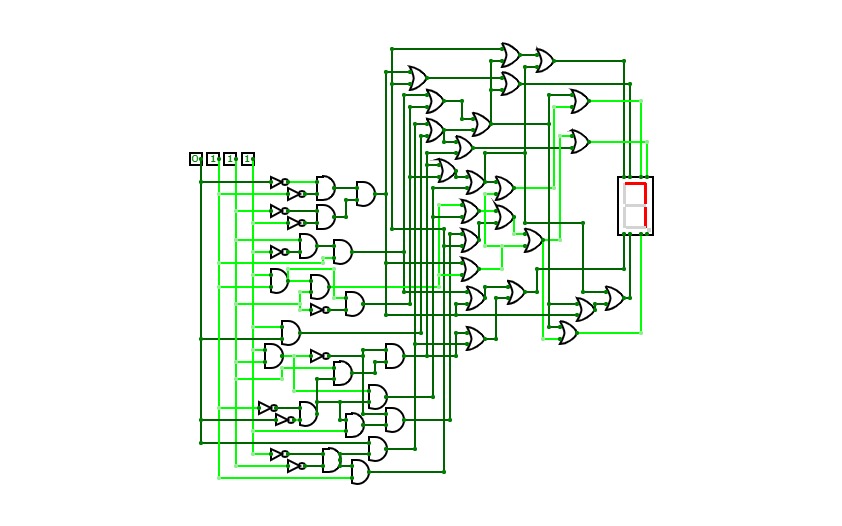

seven segment dissplay using 16x1 mux

seven segment dissplay using 16x1 mux

7 segment display using 8x1 mux

7 segment display using 8x1 mux

q14_from_20que

q14_from_20que

cat2q4b1

cat2q4b1

2:1 MUX Circuit using POS Equation

2:1 MUX Circuit using POS Equation

Untitled

Untitled

4-BIT BINARY SUBTRACTOR

4-BIT BINARY SUBTRACTOR

4 bit binary subtractor

4 bit binary subtractor

2:1 MUX Circuit using SOP Equation

2:1 MUX Circuit using SOP Equation

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

INTERNALCIRCUITUSING4:1MUX

INTERNALCIRCUITUSING4:1MUX

DAPOS

DAPOS

Untitled

Untitled

7 segment display using 4:16 decoder

7 segment display using 4:16 decoder

7 segment display using 1:16 demux

7 segment display using 1:16 demux

seven segment

seven segment

1:16sevensegment

1:16sevensegment

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

Untitled

q10dacathode

q10dacathode

seven

seven

q8 da b

q8 da b

Binary to 7 Segment

Binary to 7 Segment

Untitled

Untitled

4-BIT BINARY ADDER/SUBTRACTER

4-BIT BINARY ADDER/SUBTRACTER

Untitled

Untitled

code_convertor_nor

code_convertor_nor

Full Subtractor using 3 to 8 Decoder

Full Subtractor using 3 to 8 Decoder

code convertor_mux

code convertor_mux

DE MTE

DE MTE

booth multiplier

booth multiplier

NAND logic circuit of 2:4 Decoder

NAND logic circuit of 2:4 Decoder

NAND logic circuit of 4:2 encoder

NAND logic circuit of 4:2 encoder

code_converter_1324_demux

code_converter_1324_demux

POS canonical expression of MUX and circuit implemented in MUX

POS canonical expression of MUX and circuit implemented in MUX

Half Adder Using 2x4 Decoder

Half Adder Using 2x4 Decoder

full subtractor using mux

full subtractor using mux

Untitled

Untitled

4 BIT BINARY SUBTRACTOR,4 BIT BINARY ADDER,4 BIT BINARY ADDER/SUBTRACTOR

4 BIT BINARY SUBTRACTOR,4 BIT BINARY ADDER,4 BIT BINARY ADDER/SUBTRACTOR

BCD To Seven Segment Decoder Using Basic Logic Gates

BCD To Seven Segment Decoder Using Basic Logic Gates

Untitled

Untitled

7 segment display 1:16 demux using 1:8 demux

7 segment display 1:16 demux using 1:8 demux

2:1 MUX Circuit using POS Equation

2:1 MUX Circuit using POS Equation

4 BIT ALU

4 BIT ALU

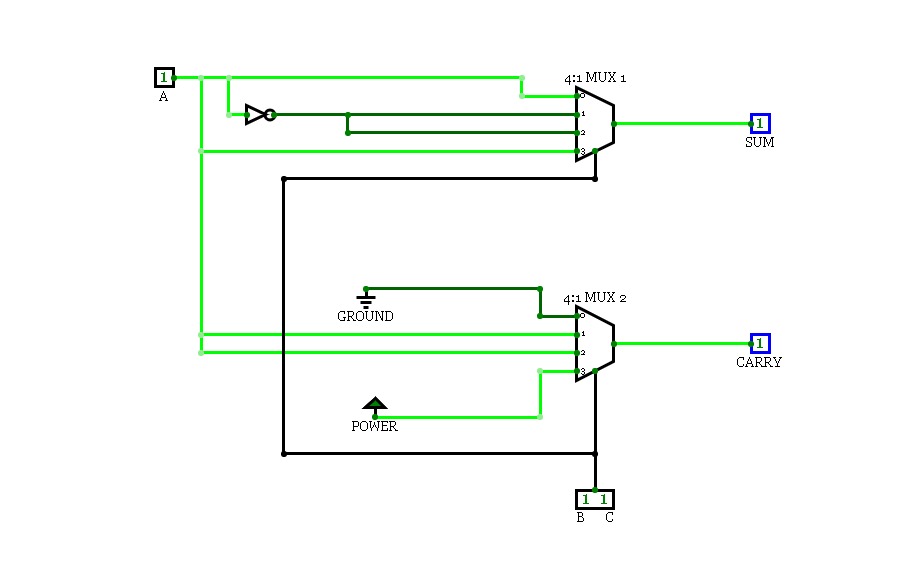

Full Adder using 2, 4*1 MUX

Full Adder using 2, 4*1 MUX

4 BIT ADDER and SUBTRACTOR

4 BIT ADDER and SUBTRACTOR

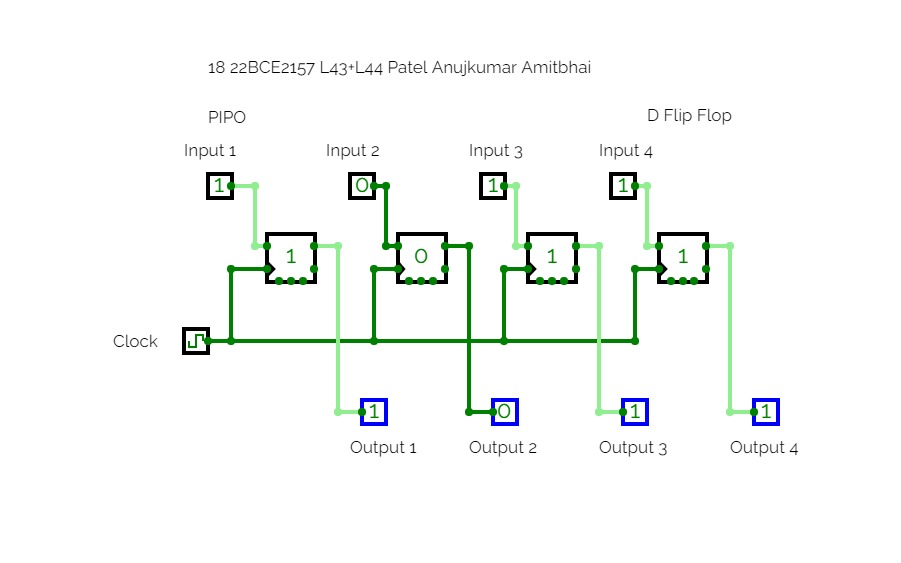

PIPO

PIPO

4-bit binary Adder-Subtractor

4-bit binary Adder-Subtractor