Alex Bracamonte

Member since: 1 year

Educational Institution: Not Entered

Country: Not Entered

FSM_Moore_Counter 0 to 4

FSM_Moore_Counter 0 to 4

Public

FF SR

FF SR

Public

FF_JK_With_Scope

FF_JK_With_Scope

Public

FF type D with Scope

FF type D with Scope

Public

Untitled

Untitled

Public

CircuitClase1

CircuitClase1

Public

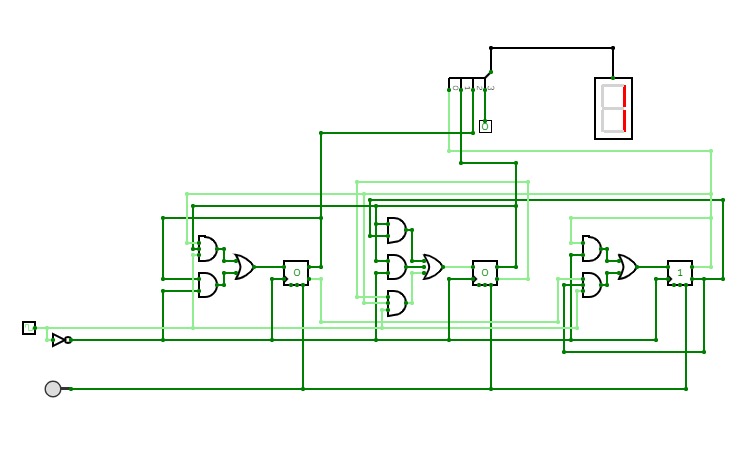

Asynchronous Counter

Asynchronous Counter

Public

Untitled

Untitled

Public

JK_Base

JK_Base

Public

Untitled

Untitled

Public

Circuit2

Circuit2

Public

MiniTerm to ROM

MiniTerm to ROM

Public

Untitled

Untitled

Public

Untitled

Untitled

Public

FSM_MooreExample

FSM_MooreExample

Public

Latch SR

Latch SR

Public

FSM_Moore_Example

FSM_Moore_Example

Public

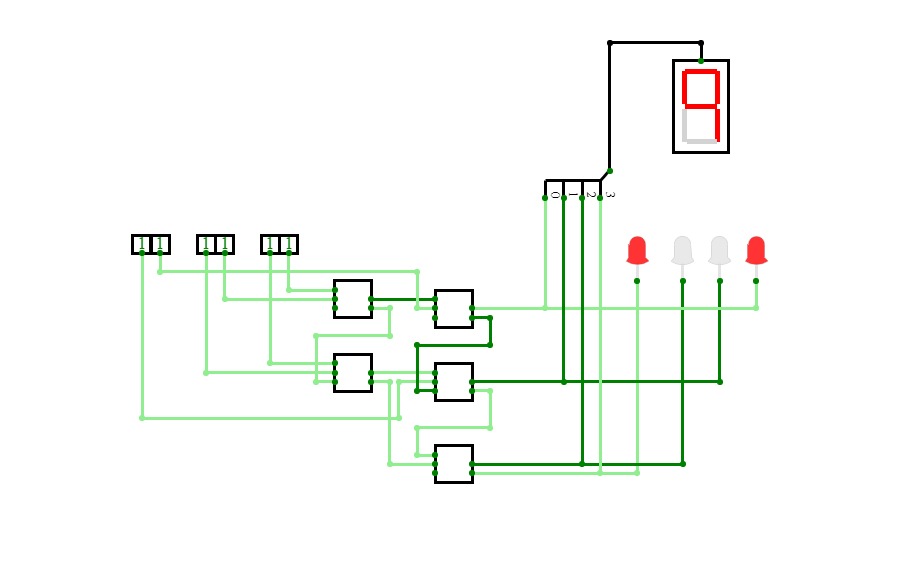

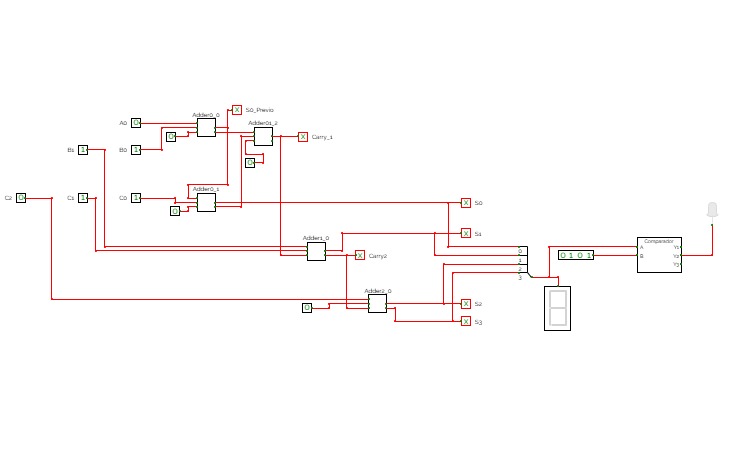

3 variable adder

3 variable adder

Public

Latch SR

Latch SR

Public

Untitled

Untitled

Public

Inversor

Inversor

Public

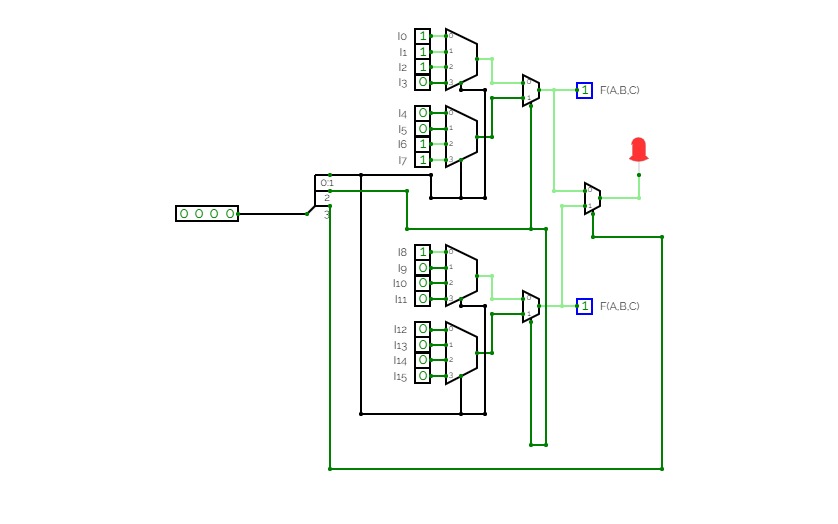

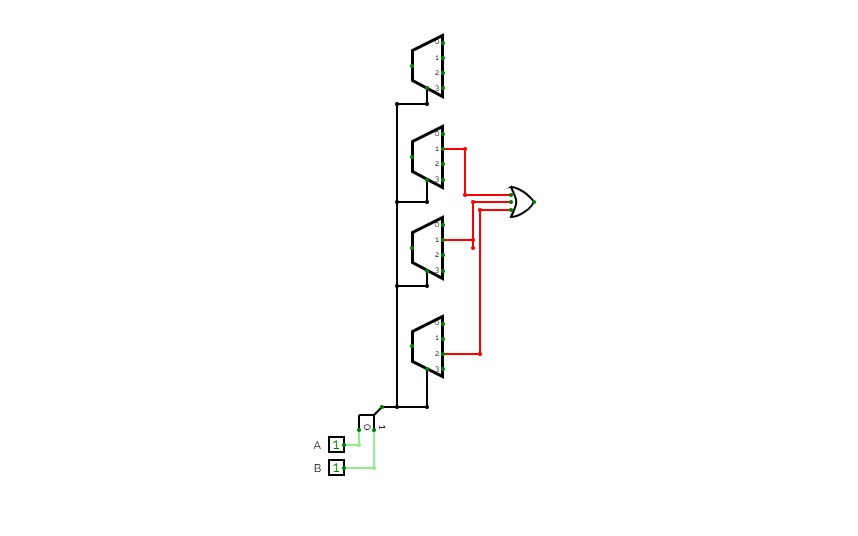

Example Mux 16:1 using 4:1

Example Mux 16:1 using 4:1

Public

Divisor3bits

Divisor3bits

Public

Logic Gates with Verilog

Logic Gates with Verilog

Public

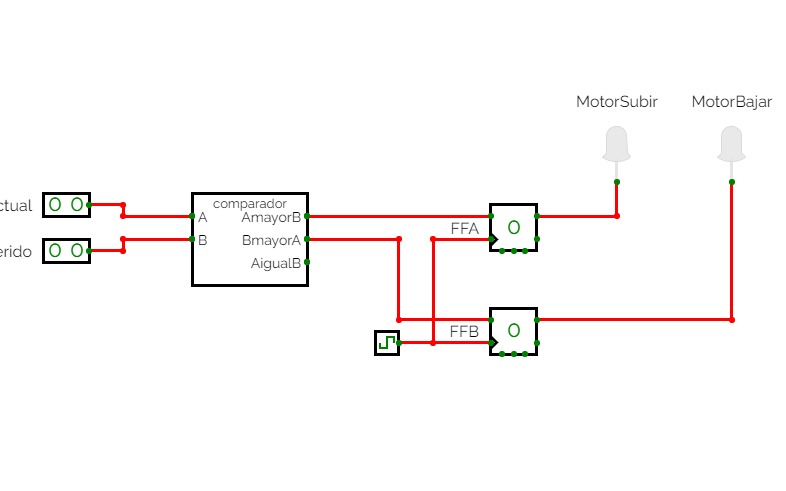

FSM_Elevador

FSM_Elevador

Public

Untitled

Untitled

Public

Dario4

Dario4

Public

JK_Base

JK_Base

Public

FSM_MealyExample_Class

FSM_MealyExample_Class

Public

ParaleloASerie

ParaleloASerie

Public

DemuxCar_Example

DemuxCar_Example

Public

Splitter

Splitter

Public

SAP - 1

SAP - 1

Public

Untitled

Untitled

Public

FF_JK_With_Scope

FF_JK_With_Scope

Public

ExampleOrAdderWIthVerilog

ExampleOrAdderWIthVerilog

Public

Led2_FSM_Mealy

Led2_FSM_Mealy

Public

Mux with SystemVerilog

Mux with SystemVerilog

Public

Example2

Example2

Public

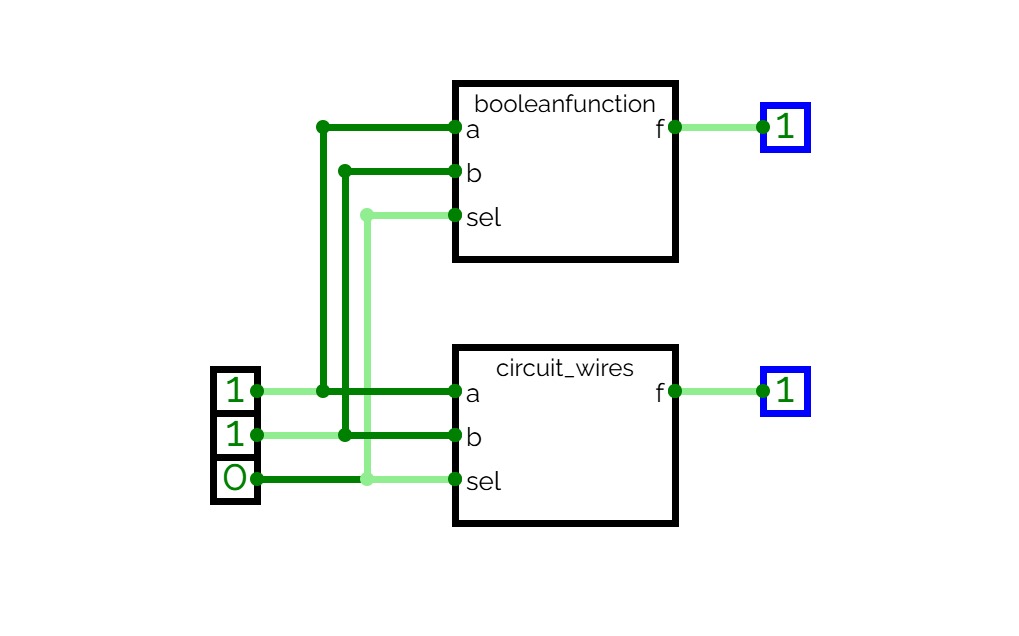

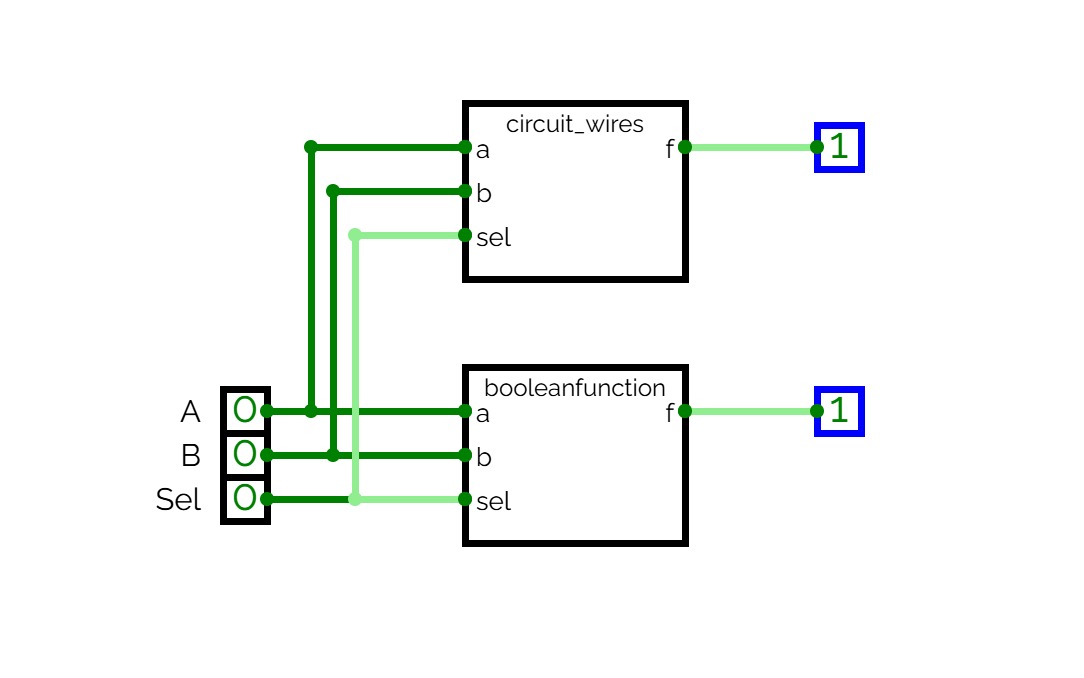

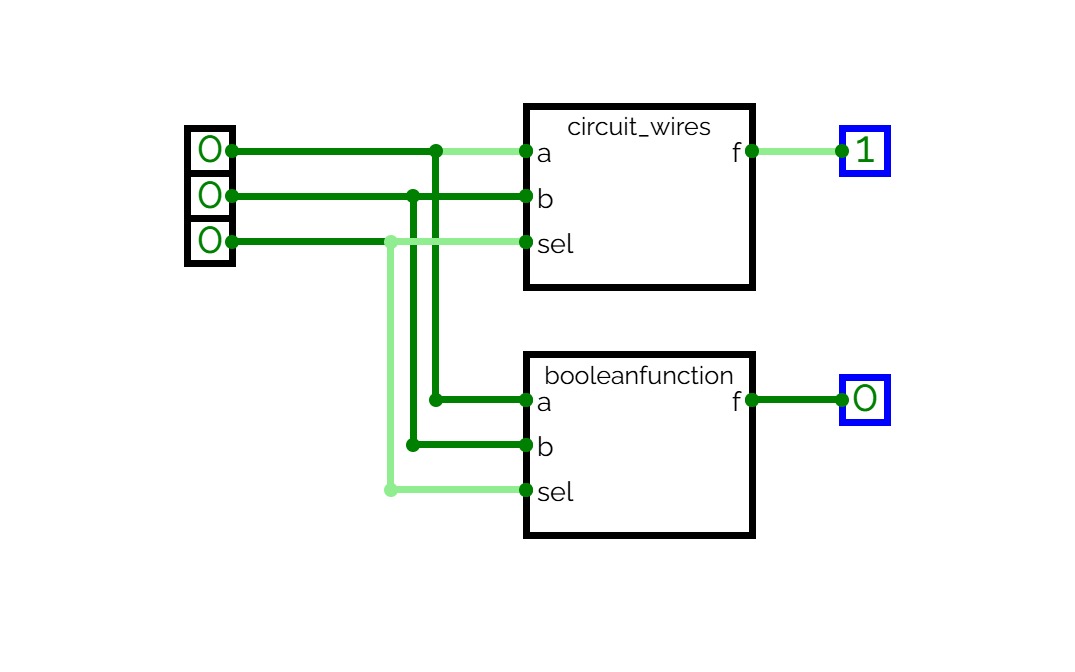

MuxWithWireAndBoolean

MuxWithWireAndBoolean

Public