Snigdha Mullick

Member since: 1 year

Educational Institution: Not Entered

Country: Not Entered

Untitled 1

Untitled 1

snigdha mullick circuits

snigdha mullick circuits

experiment number 1

experiment number 1

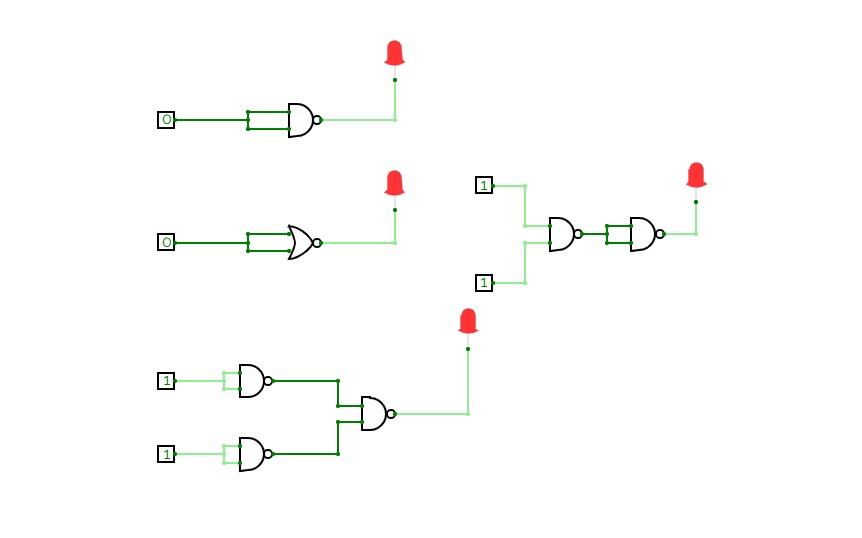

HALF SUBTRACTOR USING BASIC GATES

HALF SUBTRACTOR USING BASIC GATES

UNTITLED 3

UNTITLED 3

HALF SUBTRACTOR USING NAND GATES

HALF SUBTRACTOR USING NAND GATES

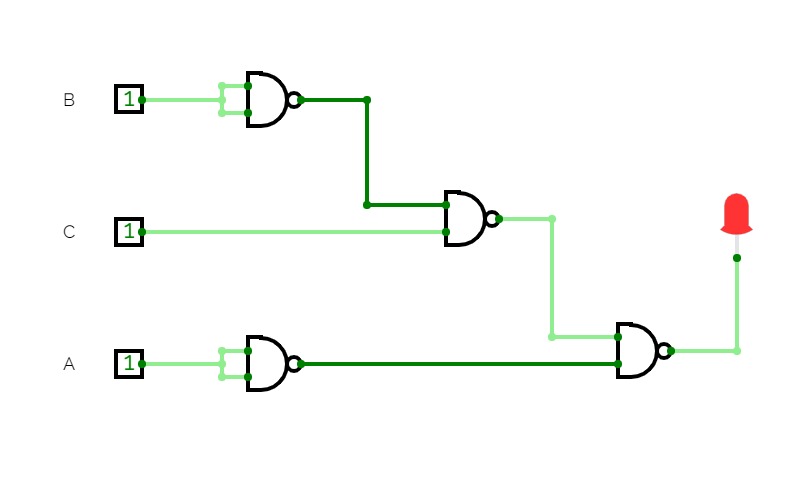

FULL SUBTRACTOR USING EX-OR AND BASIC AGTES

FULL SUBTRACTOR USING EX-OR AND BASIC AGTES

FULL SUBTRACTOR USING NAND GATES ONLY

FULL SUBTRACTOR USING NAND GATES ONLY

EXPERIMENT NUMBER 2

EXPERIMENT NUMBER 2

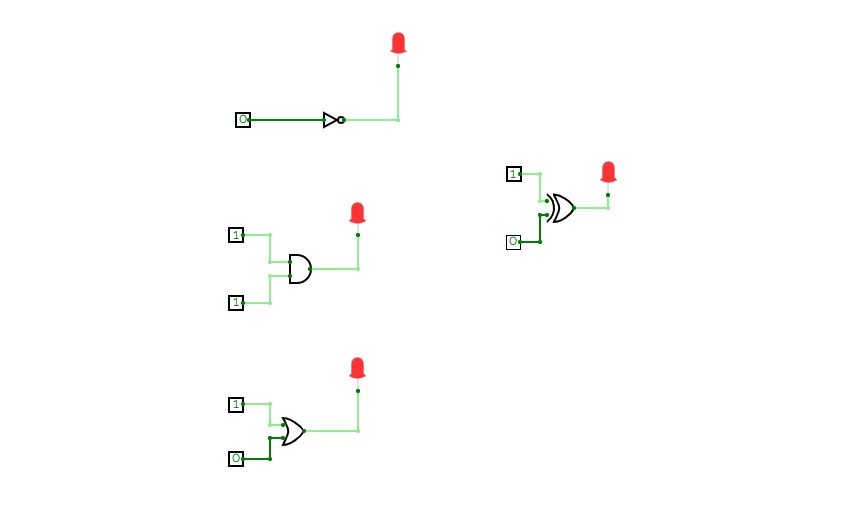

HALF ADDER USING EX-OR AND GATES

HALF ADDER USING EX-OR AND GATES

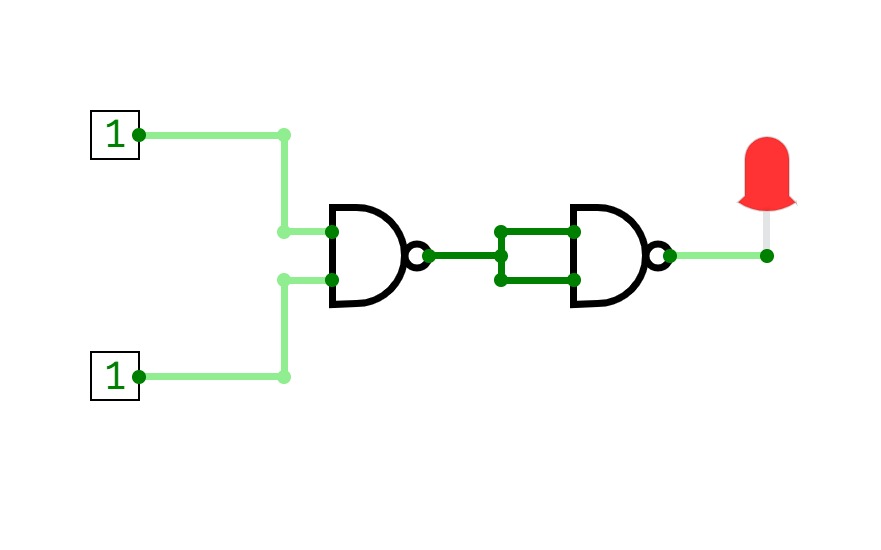

HALF ADDER USING NAND GATES

HALF ADDER USING NAND GATES

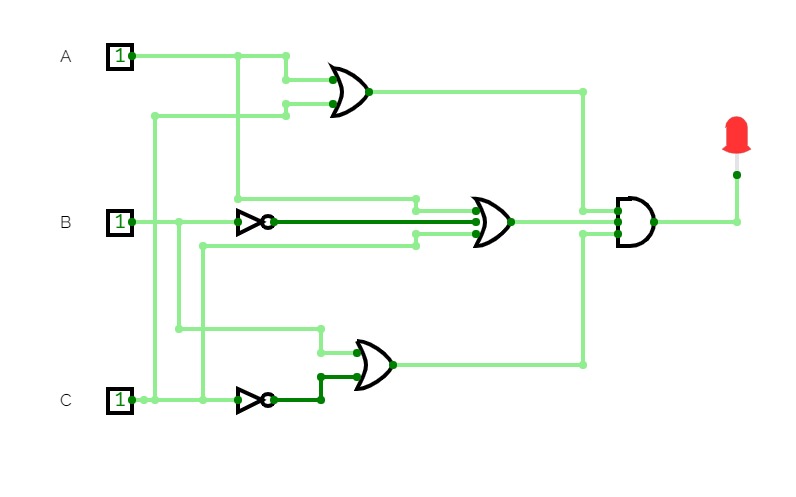

Full Adder using EXOR

Full Adder using EXOR

experiment 3-diagrams

experiment 3-diagrams

2:1 MUX using basic gates

2:1 MUX using basic gates

12-10-2023

12-10-2023

4:1 MUX

4:1 MUX

2:1 MUX

2:1 MUX

question 1

question 1

question 2

question 2

question 3

question 3

question 4

question 4

4:2 encoder

4:2 encoder

8:3 encoder

8:3 encoder

question 5

question 5

T flip flop

T flip flop

D flip flop

D flip flop

JK flip flop

JK flip flop

Untitled 2

Untitled 2

experiment number 1

experiment number 1

EXPERIMENT NUMBER2

EXPERIMENT NUMBER2

EXPERIMENT NUMBER 2

EXPERIMENT NUMBER 2

24AUG

24AUG

24AUG classwork

24AUG classwork

NOT,AND,OR,EX-OR

NOT,AND,OR,EX-OR

classwork

classwork

Classwork 17th AUG

Classwork 17th AUG

21SEPT

21SEPT

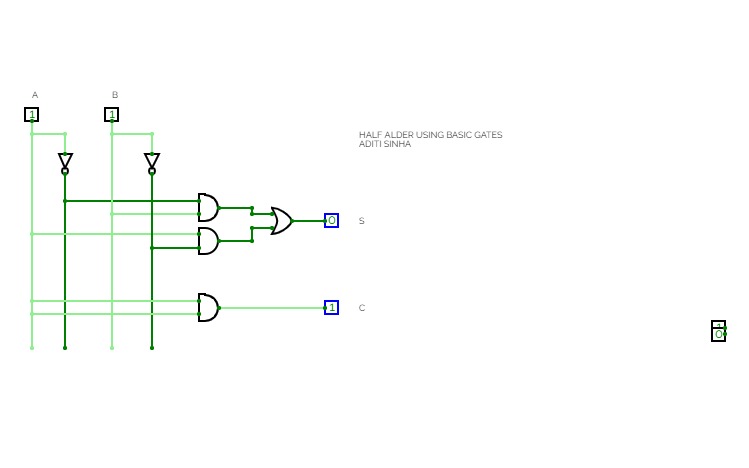

HALF ADDER USING NAND GATES

HALF ADDER USING NAND GATES