Ankit Anand

Member since: 1 year

Educational Institution: Presidency University, Bangalore

Country: India

4:2 ENCODER

4:2 ENCODER

Serial In Serial Out Shift Register

Serial In Serial Out Shift Register

Untitled

Untitled

24AUG

24AUG

LAB01 3AUG Comp. Fundamental

LAB01 3AUG Comp. Fundamental

Verification of logic gates

Verification of logic gates

Class Work (Experiment No. 1) 17th AUG

Class Work (Experiment No. 1) 17th AUG

17 Aug Ques self try

17 Aug Ques self try

Full subtractor using only NAND Gates

Full subtractor using only NAND Gates

Parallel In Parallel Out Shift Register

Parallel In Parallel Out Shift Register

Difference and B_out using XOR and basic gates

Difference and B_out using XOR and basic gates

Difference Using XOR and Basic Gates seperately

Difference Using XOR and Basic Gates seperately

Difference using only basic gates

Difference using only basic gates

DIFFERENCE AND BORROW USING ONLY NAND GATES

DIFFERENCE AND BORROW USING ONLY NAND GATES

Sum and carry

Sum and carry

up

up

8:1 MULTIPLEX

8:1 MULTIPLEX

1:2 DE MUX

1:2 DE MUX

Untitled

Untitled

1:4 DE MUX BLOCK DIAGRAM

1:4 DE MUX BLOCK DIAGRAM

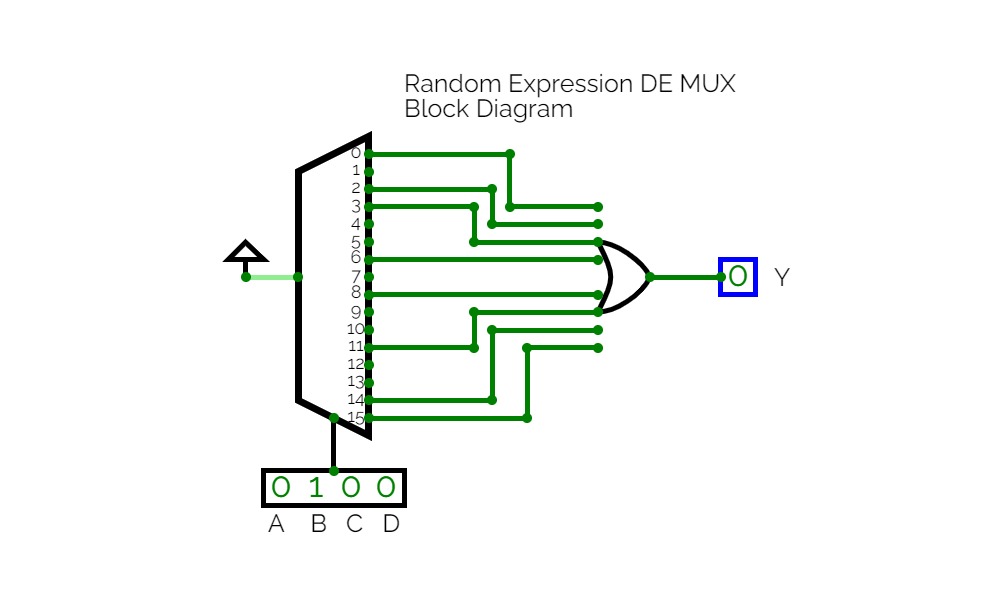

Random Expression DE MUX Block Diagram

Random Expression DE MUX Block Diagram

Random Expression DE MUX Block Diagram

Random Expression DE MUX Block Diagram

Random Expression DE MUX Block Diagram

Random Expression DE MUX Block Diagram

Half Subtractor using NAND Gates

Half Subtractor using NAND Gates

Half Adder using Basic Gates (2)

Half Adder using Basic Gates (2)

Full adder using only NAND Gates

Full adder using only NAND Gates

Half Substractor Using XOR and Basic Gates

Half Substractor Using XOR and Basic Gates

Half Substractor Using Basic Gates

Half Substractor Using Basic Gates

Full Adder using EXOR and basic gates

Full Adder using EXOR and basic gates

Half Adder using only NAND gates

Half Adder using only NAND gates

Untitled

Untitled

Full subtractor using EXOR and basic gates

Full subtractor using EXOR and basic gates

name

name

4:1 MUX

4:1 MUX

8:1 MUX

8:1 MUX

4:1 MUX

4:1 MUX

4:1 MUX SELF TRY

4:1 MUX SELF TRY

8:1 MUX SELF TRY

8:1 MUX SELF TRY

Class work 5 October

Class work 5 October

Class work 5 October

Class work 5 October

2:1 MUX using basic gates

2:1 MUX using basic gates

4:1 MUX USING BASIC GATES

4:1 MUX USING BASIC GATES

3bit DOWN counter using JK Flip Flop

3bit DOWN counter using JK Flip Flop

3bit UP counter Flip Flop

3bit UP counter Flip Flop

4-bit Asynchronous UP Counter Using JK flip flop

4-bit Asynchronous UP Counter Using JK flip flop

Serial In Parallel Out Shift Register

Serial In Parallel Out Shift Register

4-bit Asynchronous DOWN counter using JK Flip Flop

4-bit Asynchronous DOWN counter using JK Flip Flop

Class Question

Class Question

4-bit Asynchronous UP Counter Using JK flip flop

4-bit Asynchronous UP Counter Using JK flip flop

4-bit Asynchronous DOWN counter using JK Flip Flop

4-bit Asynchronous DOWN counter using JK Flip Flop