Harsh Vardhan Pandey

Member since: 1 year

Educational Institution: Jain University

Country: India

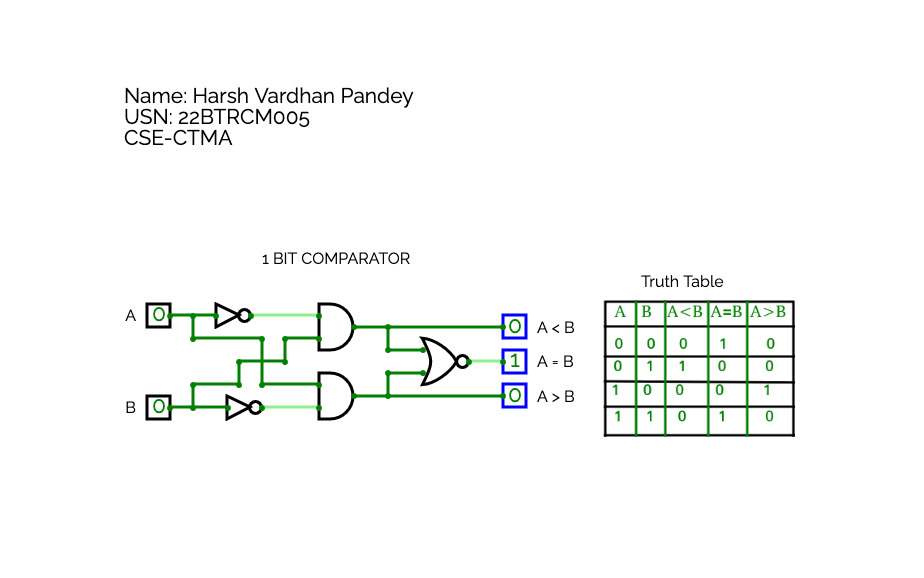

1 bit comparator

1 bit comparator

Public

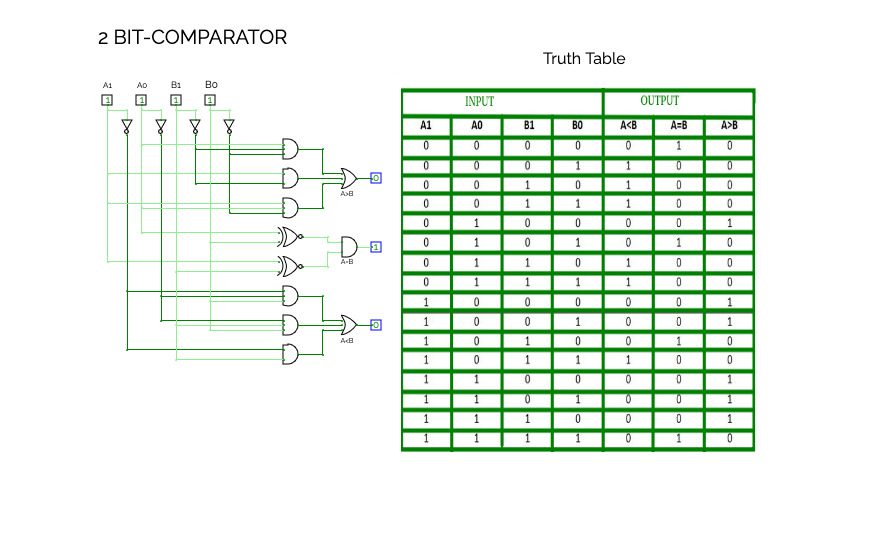

2 bit comparator using basic gates

2 bit comparator using basic gates

Public

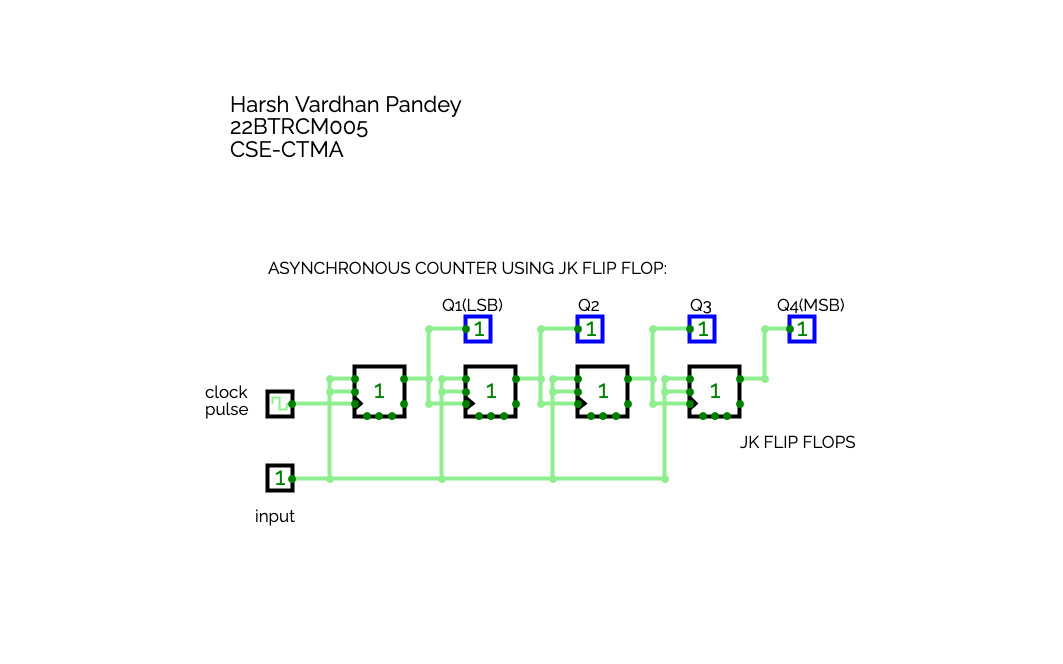

ASYNCHRONOUS COUNTER USING JK FLIP FLOP

ASYNCHRONOUS COUNTER USING JK FLIP FLOP

Public

SR,JK,T,F FLIP FLOP Using NAND and NOR Gate

SR,JK,T,F FLIP FLOP Using NAND and NOR Gate

Public

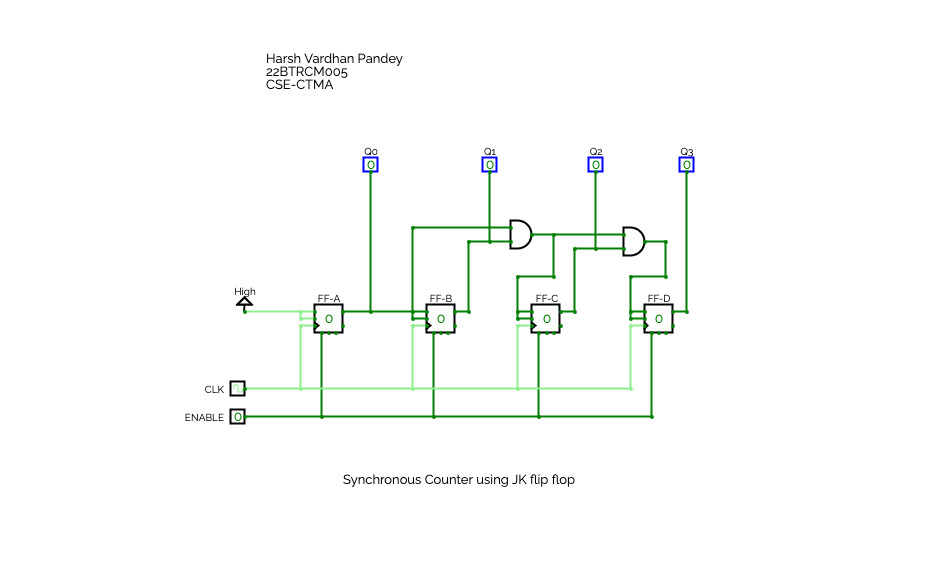

SYNCHRONOUS COUNTER

SYNCHRONOUS COUNTER

Public

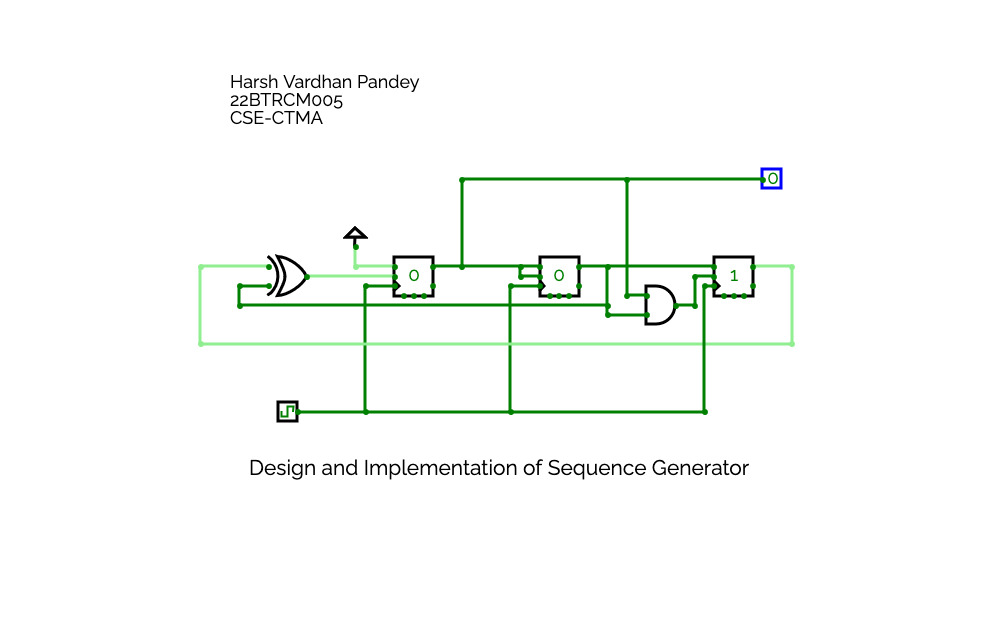

Sequence generator

Sequence generator

Public

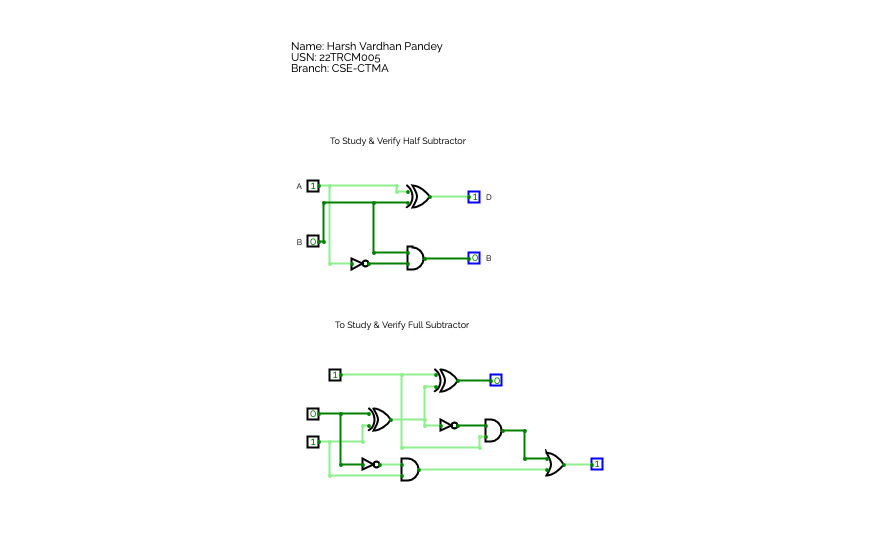

Half Subtractor

Half Subtractor

Public

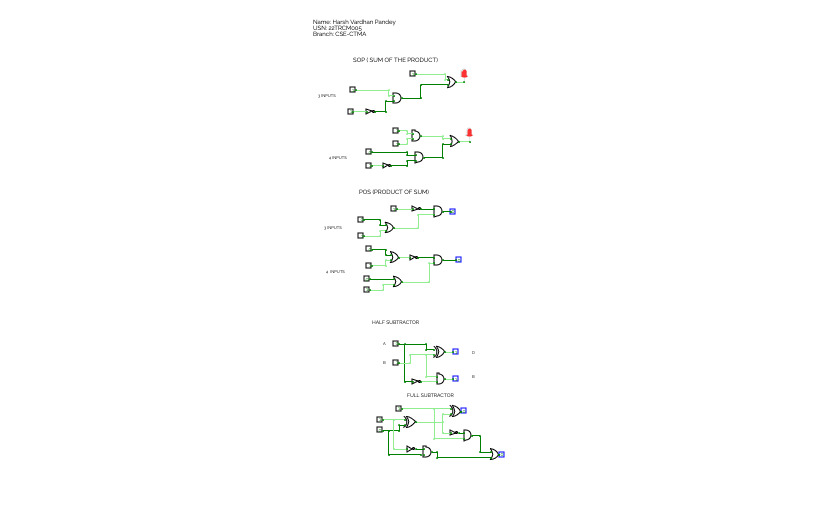

SOP,POS, HALF & FULL SUBTRACTOR

SOP,POS, HALF & FULL SUBTRACTOR

Public

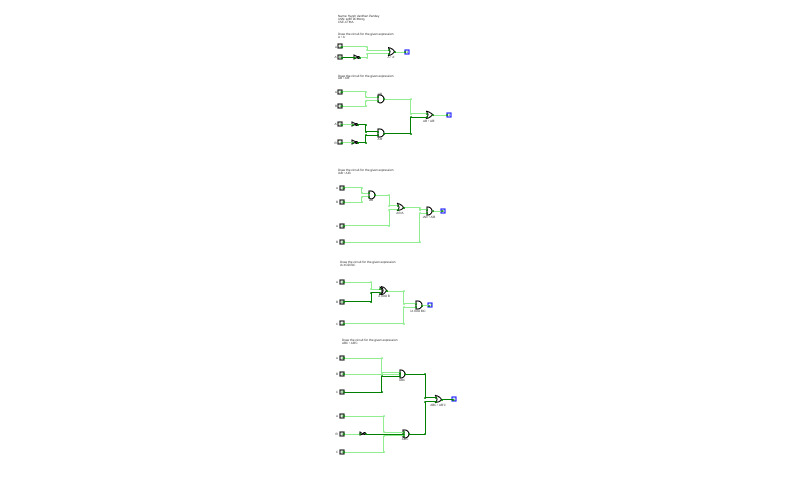

Module 2 Assignment For Day 1

Module 2 Assignment For Day 1

Public

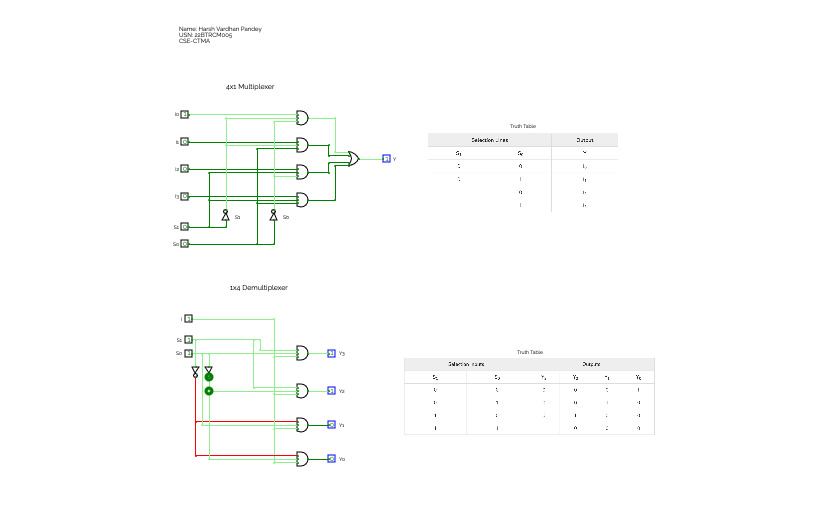

4x1 Multiplexer & 1x4 Demultiplexer

4x1 Multiplexer & 1x4 Demultiplexer

Public

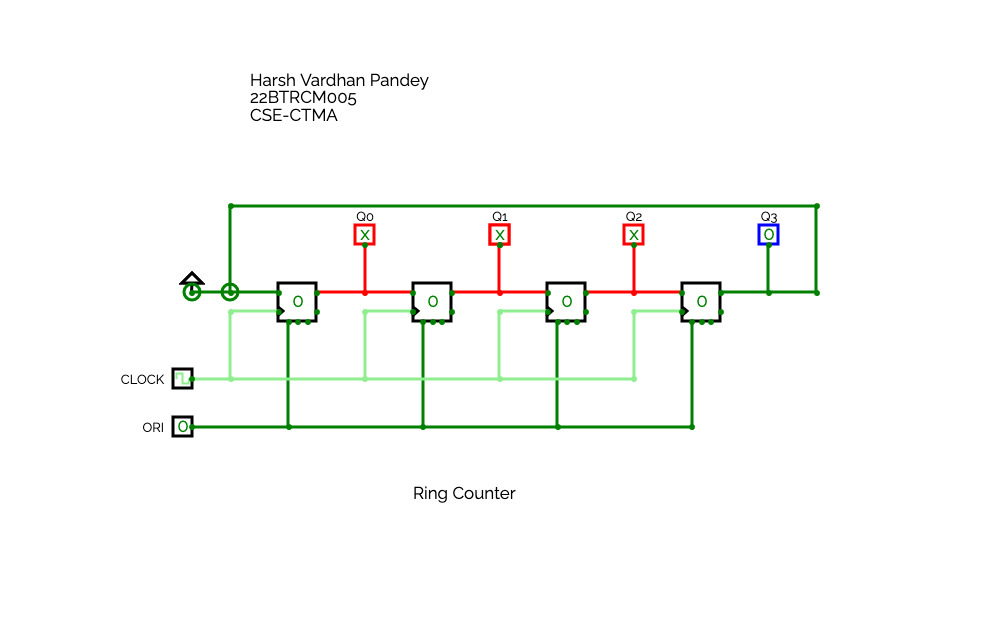

Ring and Johnson Counter

Ring and Johnson Counter

Public

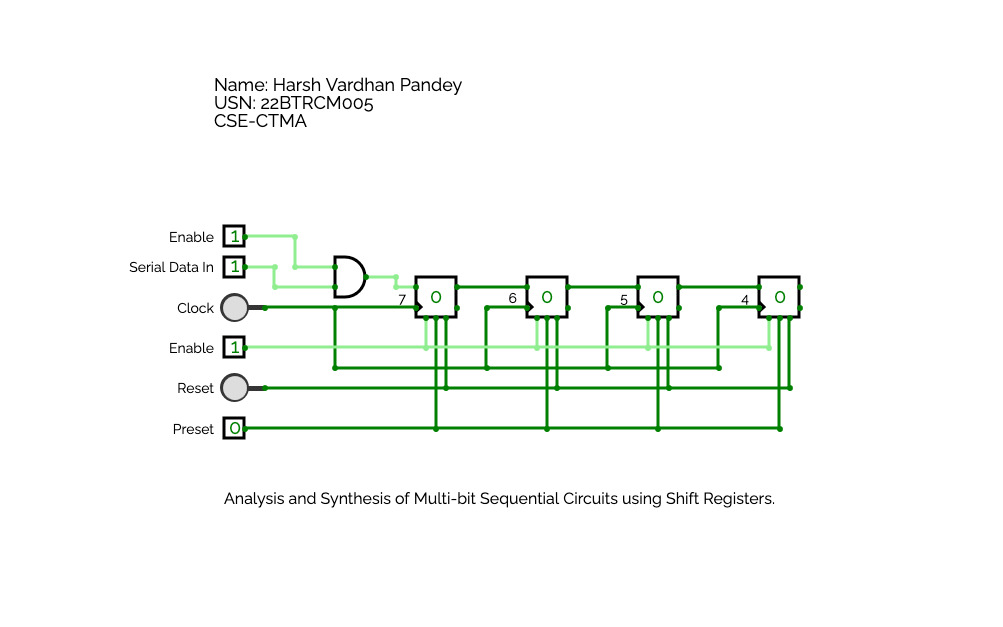

Analysis and Synthesis of Multi-bit Sequential Circuits using Shift Registers.

Analysis and Synthesis of Multi-bit Sequential Circuits using Shift Registers.

Public

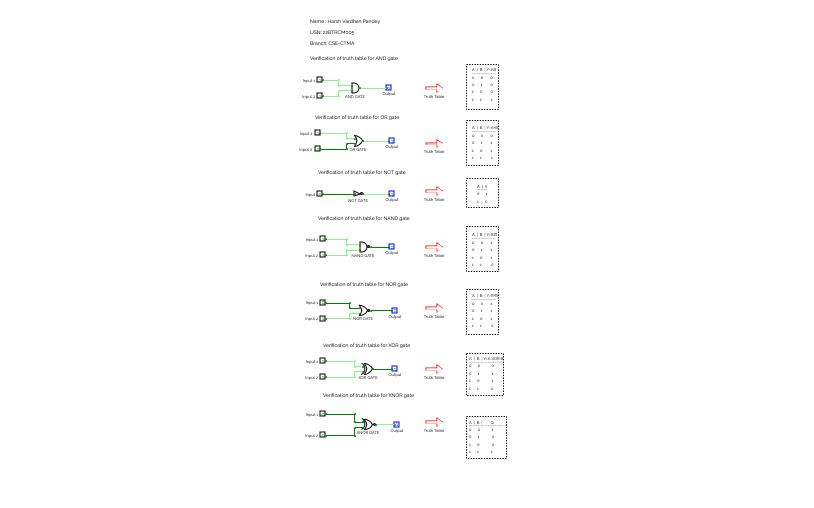

Verfication of Truth Table for AND, OR, NOR, NAND, NOR, X-OR, X-NOR

Verfication of Truth Table for AND, OR, NOR, NAND, NOR, X-OR, X-NOR

Public

Verfication of Truth Table for AND, OR, NOR, NAND, NOR, X-OR, X-NOR

Verfication of Truth Table for AND, OR, NOR, NAND, NOR, X-OR, X-NOR

Public