You must login before you can post a comment.

Author: CHRISTIAN JOEL QUISPE HERRERA

Forked from: SRITHILAK R CSE/FULL ADDERS

Project access type: Public

Description:

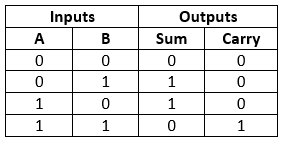

Full Adder is the adder that adds three inputs and produces two outputs. The first two inputs are A and B and the third input is an input carry as C-IN. The output carry is designated as C-OUT and the normal output is designated as S which is SUM. A full adder logic is designed in such a manner that can take eight inputs together to create a byte-wide adder and cascade the carry bit from one adder to another. we use a full adder because when a carry-in bit is available, another 1-bit adder must be used since a 1-bit half-adder does not take a carry-in bit. A 1-bit full adder adds three operands and generates 2-bit results.

Here we need to make a full adder on simulator by using gate ie. XOR gate and NAND gate after that we need to check whether it is right or not by giving input 0 or 1 . As we have already make a truth table for it in order to check and match whether the circuit is connected or working properly well or not.

TRUTH TABLE

Created: Mar 20, 2024

Updated: Mar 20, 2024

Comments