Srilakshmi Kh

Member since: 2 years

Educational Institution: Not Entered

Country: Not Entered

EXPT-1 L1 LOGICGATES

EXPT-1 L1 LOGICGATES

LOGIC GATES

LOGIC GATES

EXPT-1 LOGIC GATES

EXPT-1 LOGIC GATES

EXPT-1 LEVEL2 BASIC GATES USING UNIVERSAL GATES

EXPT-1 LEVEL2 BASIC GATES USING UNIVERSAL GATES

EXPT-1 LEVEL2 BASIC GATES USING UNIVERSAL GATES

EXPT-1 LEVEL2 BASIC GATES USING UNIVERSAL GATES

4 BIT SYNCHRONOUS

4 BIT SYNCHRONOUS

EXPT1

EXPT1

HALF ADDER AND SUBTRACTOR USING NAND GATES

HALF ADDER AND SUBTRACTOR USING NAND GATES

EXPT-2 6

EXPT-2 6

expt-2 :5,6

expt-2 :5,6

DISTRIBUTIVE

DISTRIBUTIVE

ABORPTION LAW

ABORPTION LAW

EXPT-2:1,2,3,4

EXPT-2:1,2,3,4

FF CONVERSION

FF CONVERSION

EXPT-3 MUX DEMUX

EXPT-3 MUX DEMUX

ASYNCHRONOUS UP DOWN COUNTER-3BIT

ASYNCHRONOUS UP DOWN COUNTER-3BIT

EXPT-6 LEVEL-1

EXPT-6 LEVEL-1

expt-8 Asynchronous up/down counter

expt-8 Asynchronous up/down counter

EXPT-5

EXPT-5

EXPT-5

EXPT-5

EXPT-1L1

EXPT-1L1

EXPT-2 HALF ADDER/SUBTRACTOR

EXPT-2 HALF ADDER/SUBTRACTOR

HALF ADDER AND FULL ADDER

HALF ADDER AND FULL ADDER

MUX IMPLEMENTATION

MUX IMPLEMENTATION

STUDY OF FLIP FLOPS

STUDY OF FLIP FLOPS

EXPT-7-LEVEL1

EXPT-7-LEVEL1

EXPT-7 NAND BASED JKFF AND DFF

EXPT-7 NAND BASED JKFF AND DFF

STUDY OF FLIP FLOPS

STUDY OF FLIP FLOPS

EXPT7-LEVEL2 FF CONVERSIONS

EXPT7-LEVEL2 FF CONVERSIONS

LOGICAL IMPLEMENTATION

LOGICAL IMPLEMENTATION

EXPT-7 NAND BASED JKFF AND DFF

EXPT-7 NAND BASED JKFF AND DFF

4 BIT SYNCHRONOUS CIRCUIT

4 BIT SYNCHRONOUS CIRCUIT

QUESNO12

QUESNO12

EXPT-1 LEVEL2

EXPT-1 LEVEL2

EXPT-1 LEVEL2

EXPT-1 LEVEL2

EXPT-5 PART-1

EXPT-5 PART-1

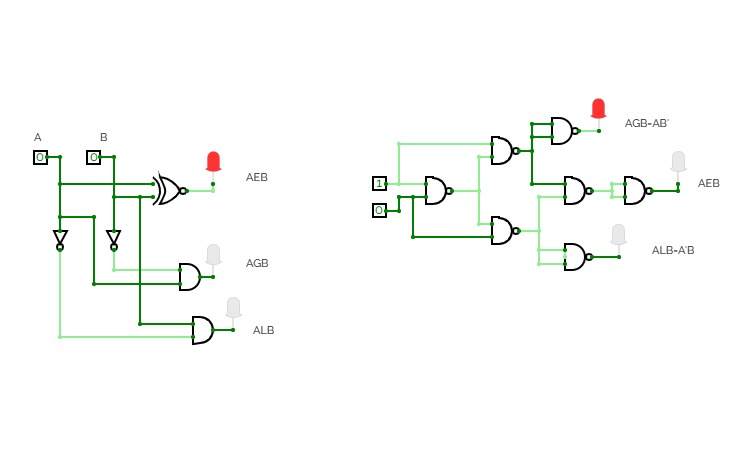

1BIT COMPARATOR

1BIT COMPARATOR

EXPT-7 SYNCHRONOUS COUNTER

EXPT-7 SYNCHRONOUS COUNTER

EXPT-4 ADDER

EXPT-4 ADDER

3BIT ADDER / FULL ADDER

3BIT ADDER / FULL ADDER

2 BIT COMPARATOR

2 BIT COMPARATOR

LEVEL-2 BIT COMPARATOR

LEVEL-2 BIT COMPARATOR

EXPT1-L2

EXPT1-L2

EXPT-1 LEVEL1

EXPT-1 LEVEL1

EXPT-1 LOGIC GATES

EXPT-1 LOGIC GATES

EXPT-1 LEVEL2

EXPT-1 LEVEL2