ravichandana

Member since: 1 year

Educational Institution: Not Entered

Country: Not Entered

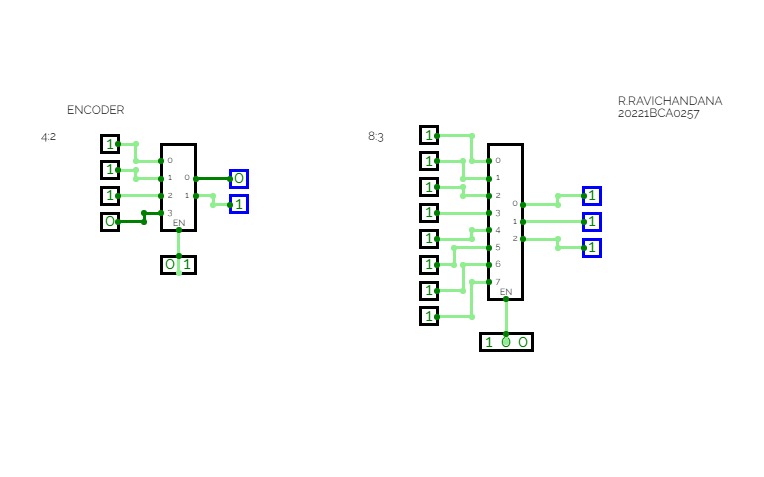

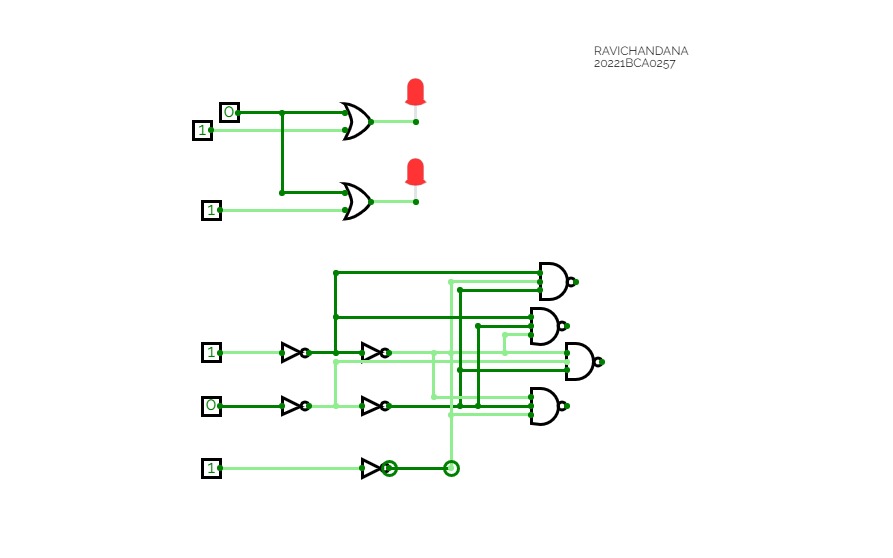

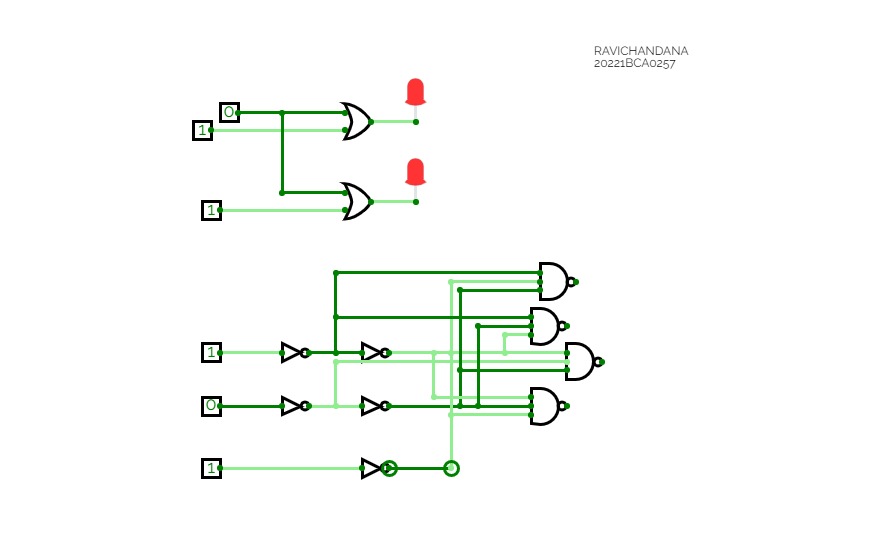

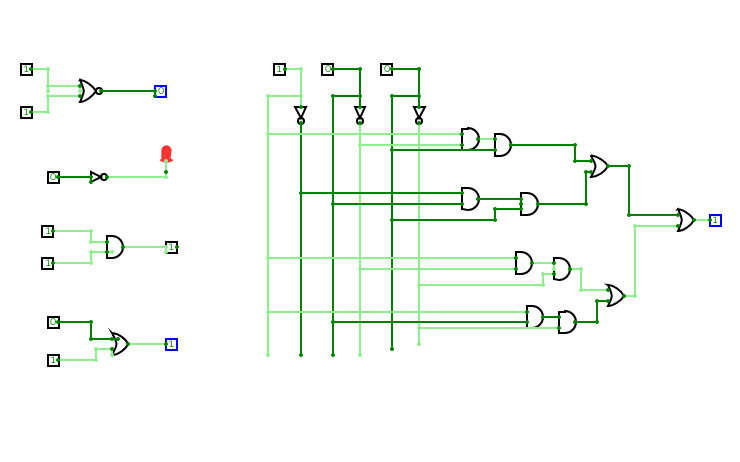

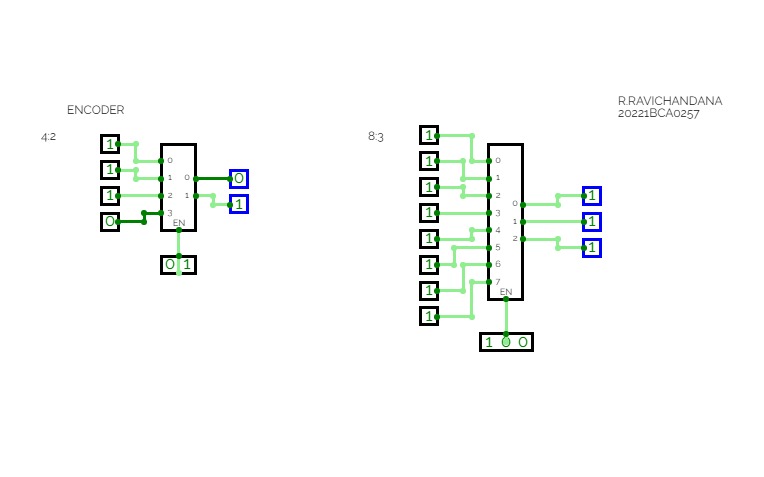

ENCODER BLOCK REPRESENTATION

ENCODER BLOCK REPRESENTATION

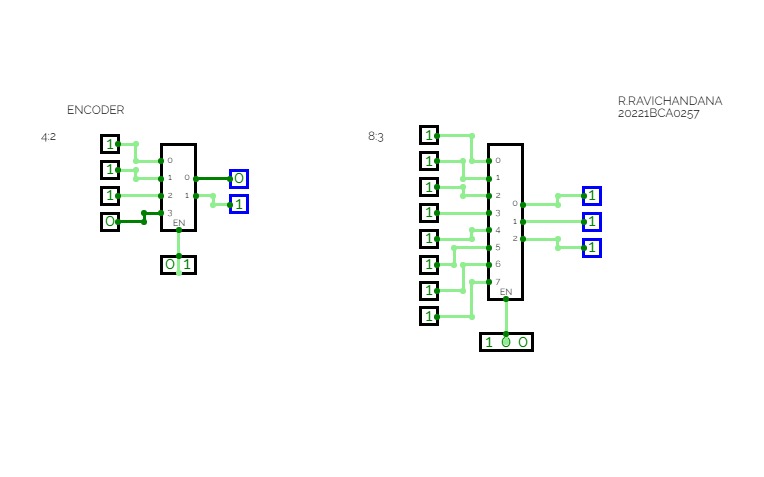

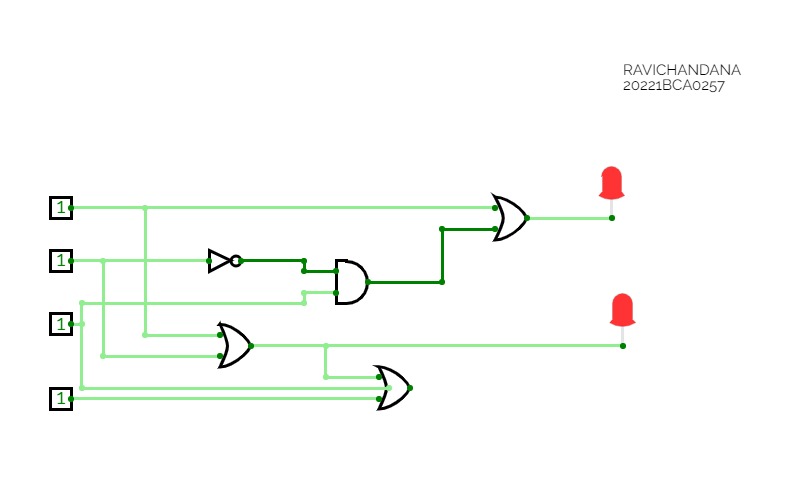

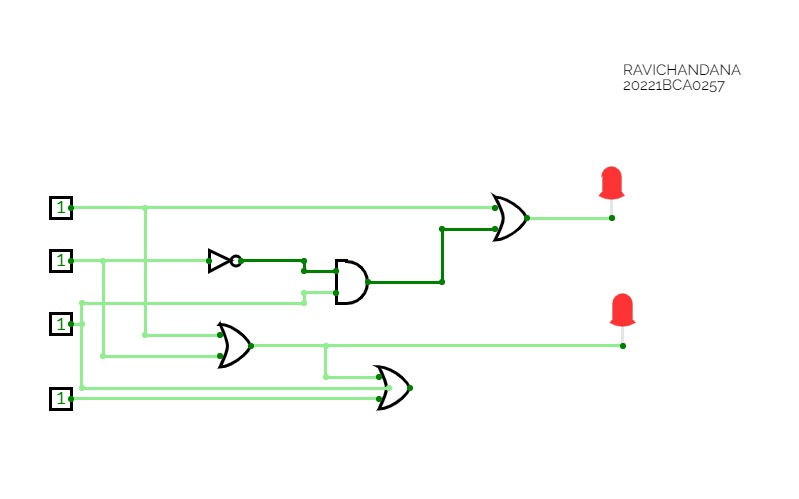

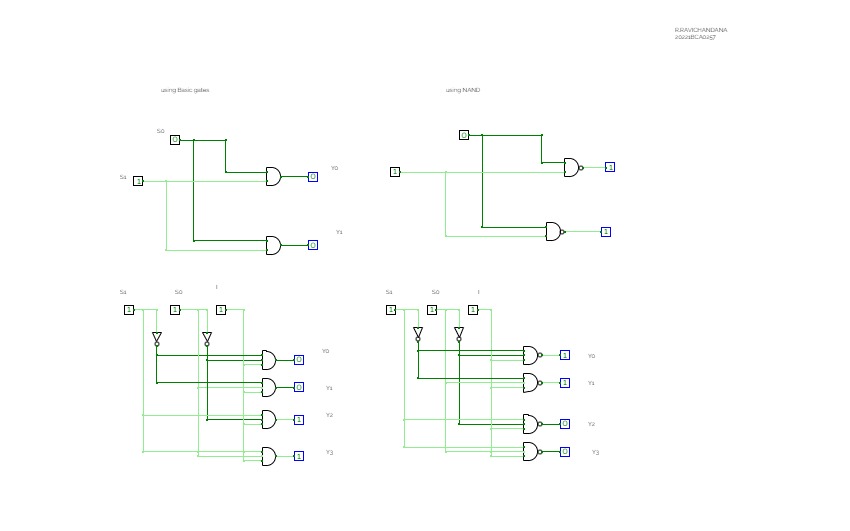

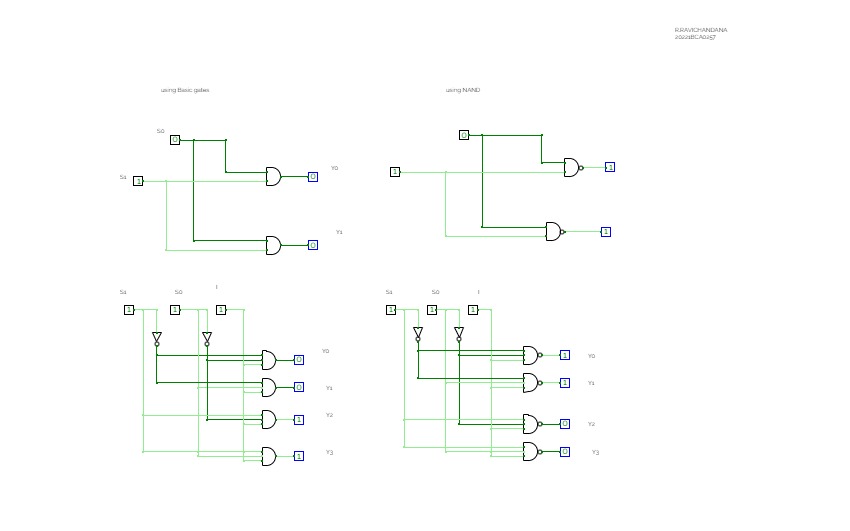

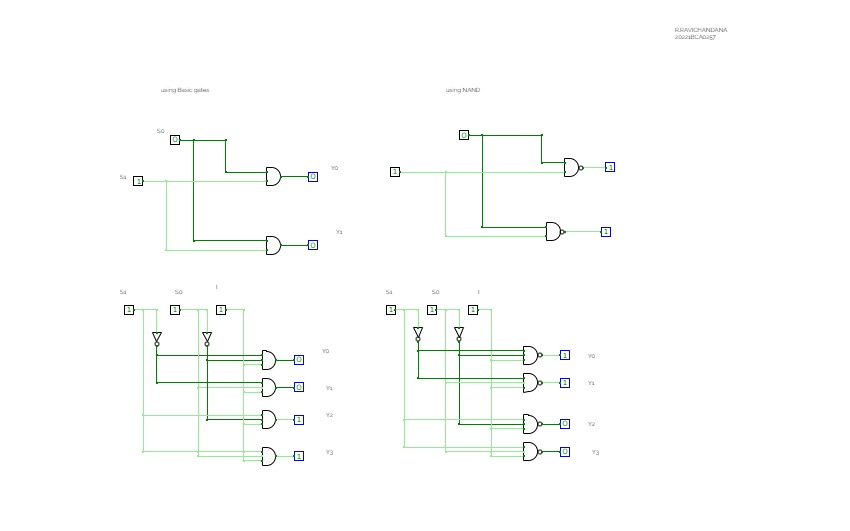

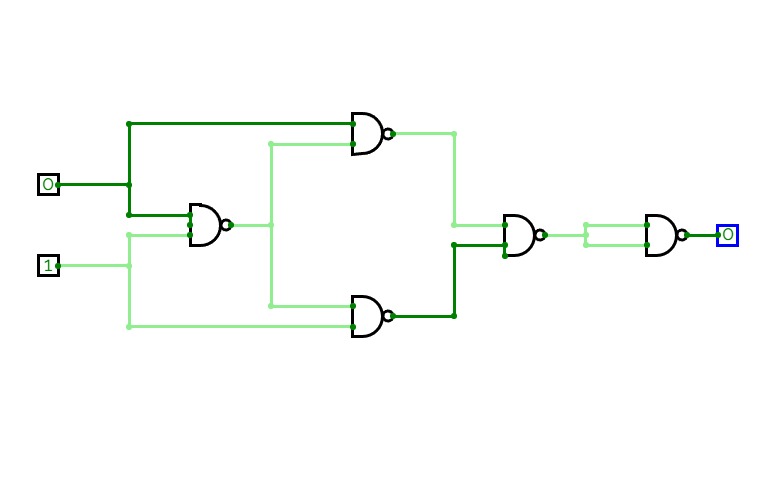

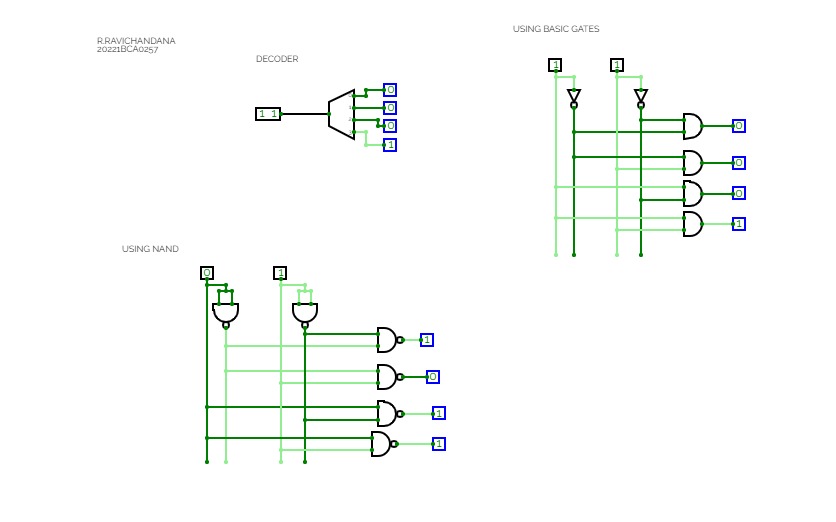

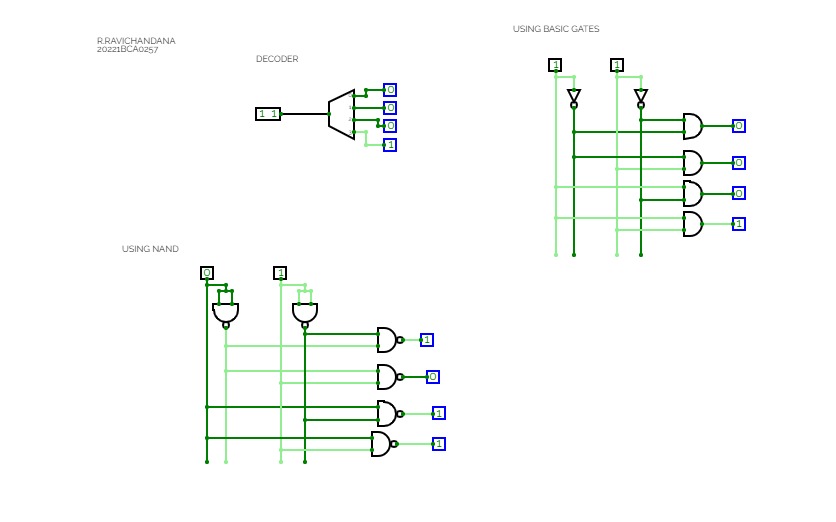

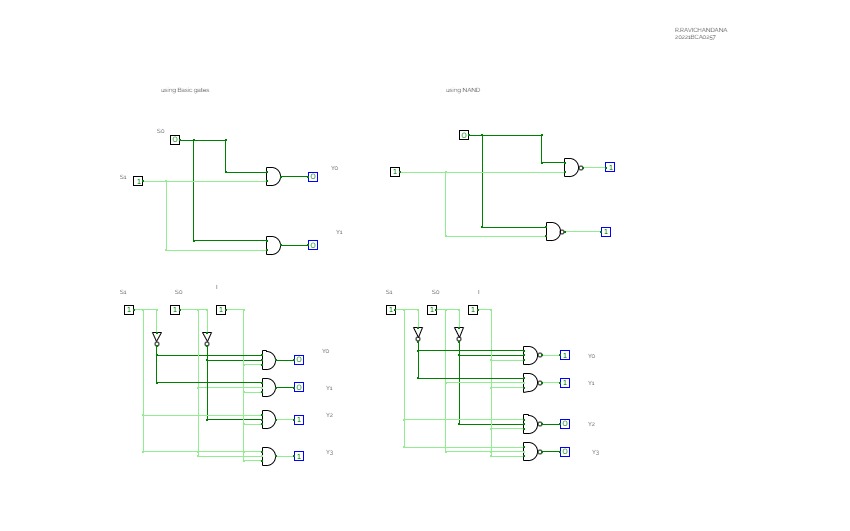

2:4 DECODER

2:4 DECODER

Untitled

Untitled

ENC DEC

ENC DEC

ENC DEC

ENC DEC

EXP 5

EXP 5

EXP 5

EXP 5

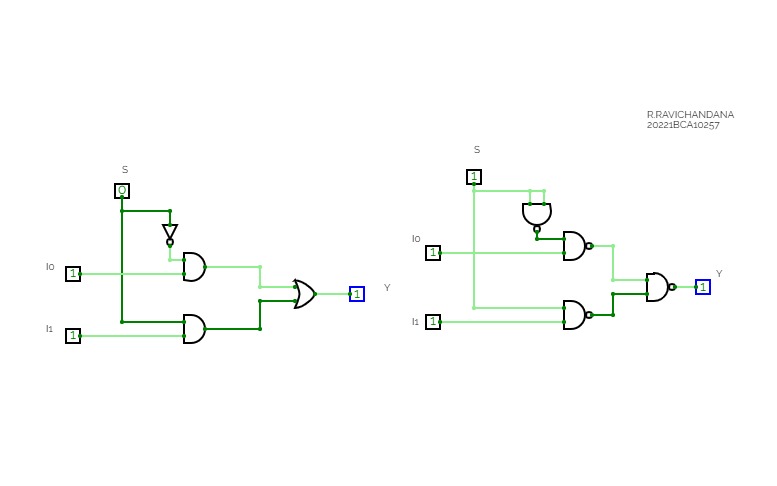

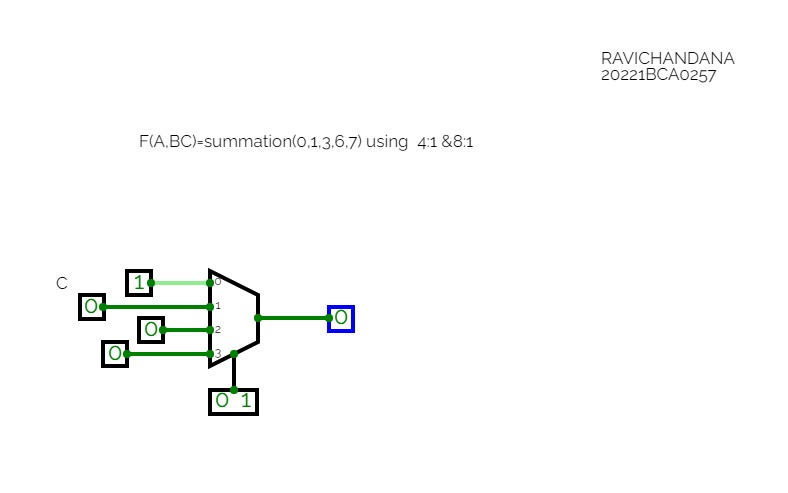

MUX 2

MUX 2

MUX 1

MUX 1

MUX 1

MUX 1

MUX 1

MUX 1

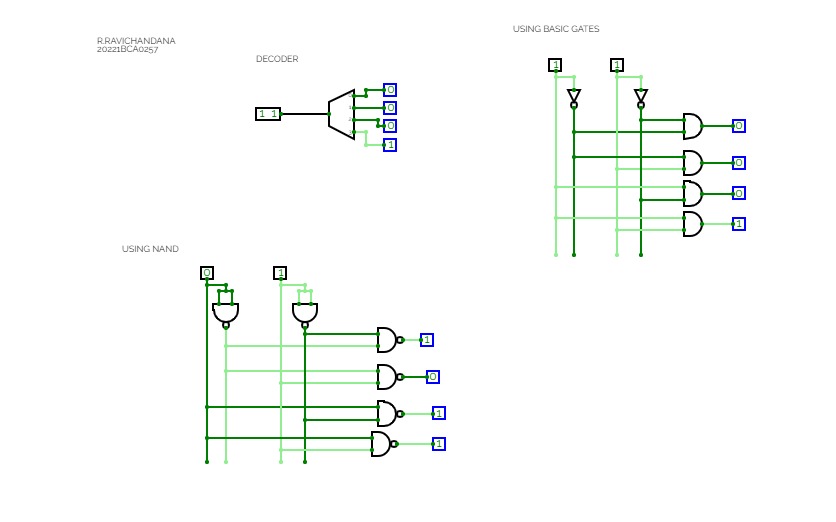

experiment 1

experiment 1

lab 2 AND

lab 2 AND

lab 2 AND

lab 2 AND

lab 2 AND

lab 2 AND

Untitled

Untitled

2:4 DECODER

2:4 DECODER

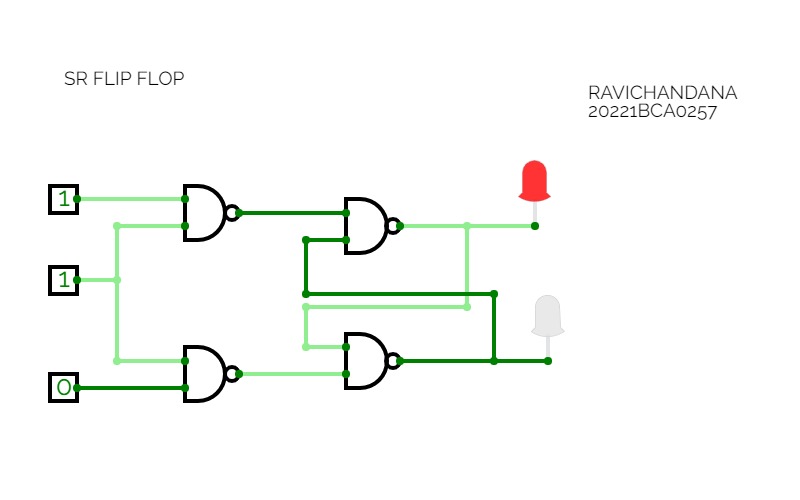

SR FLIP FLOP

SR FLIP FLOP

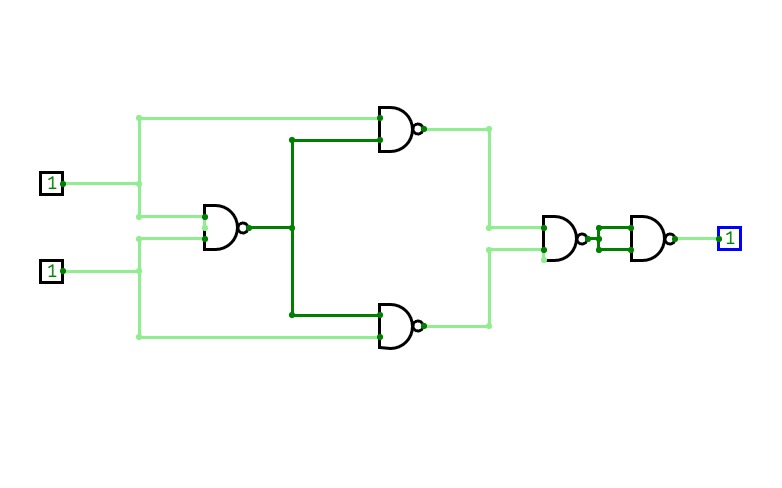

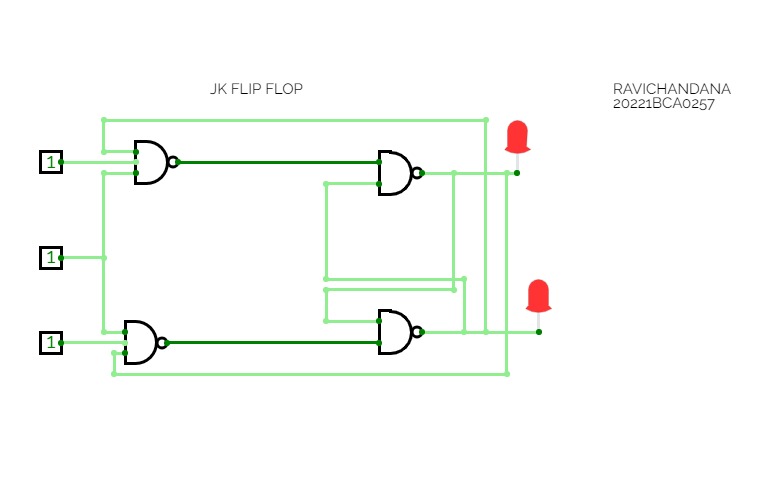

JK FLIP FLOP

JK FLIP FLOP

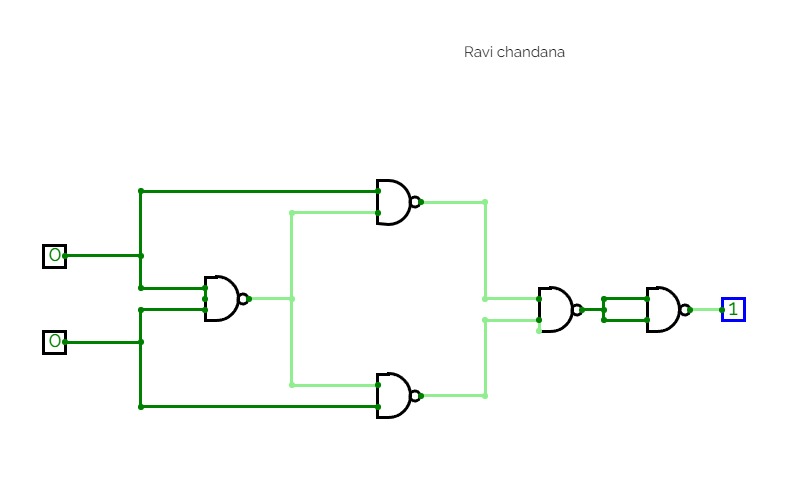

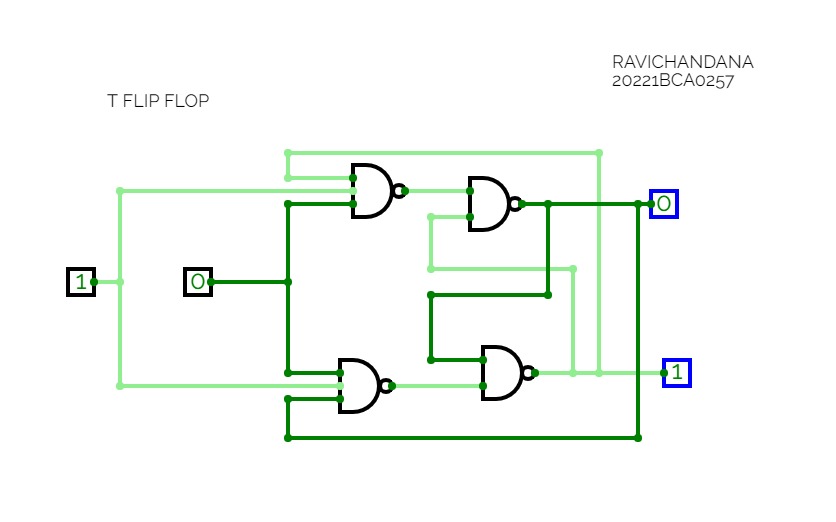

T FLIP FLOP

T FLIP FLOP

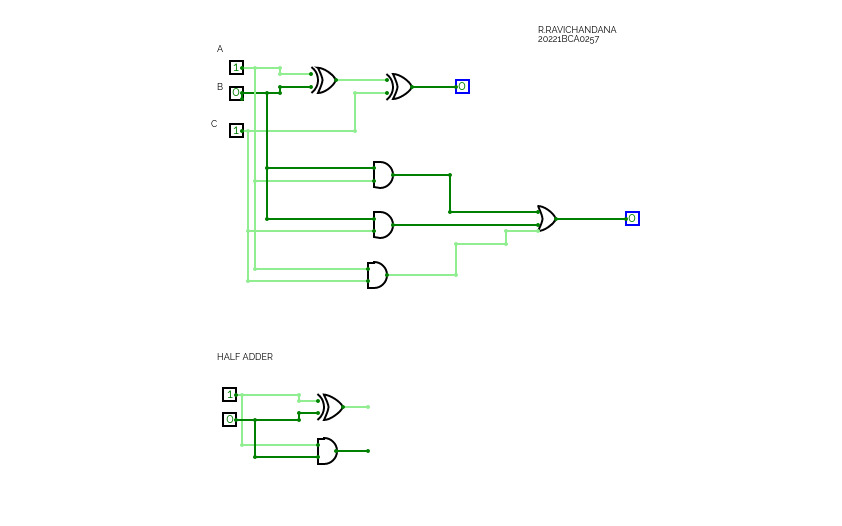

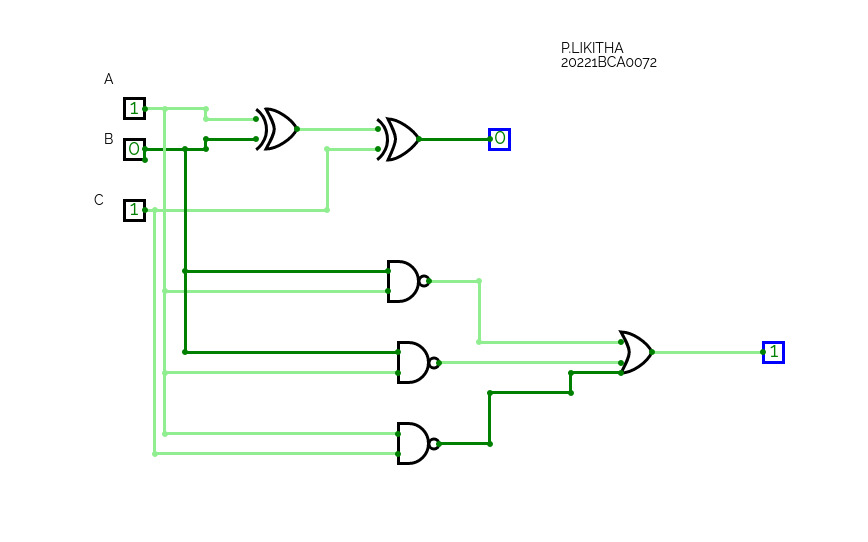

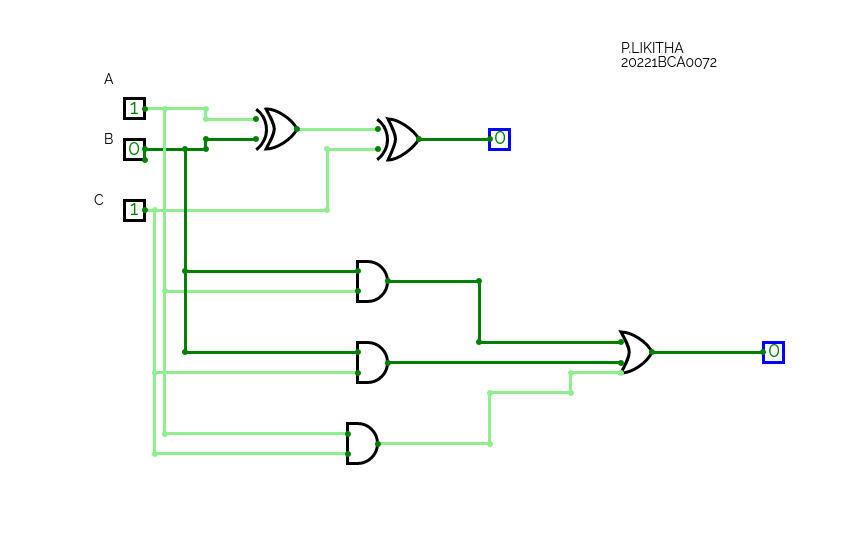

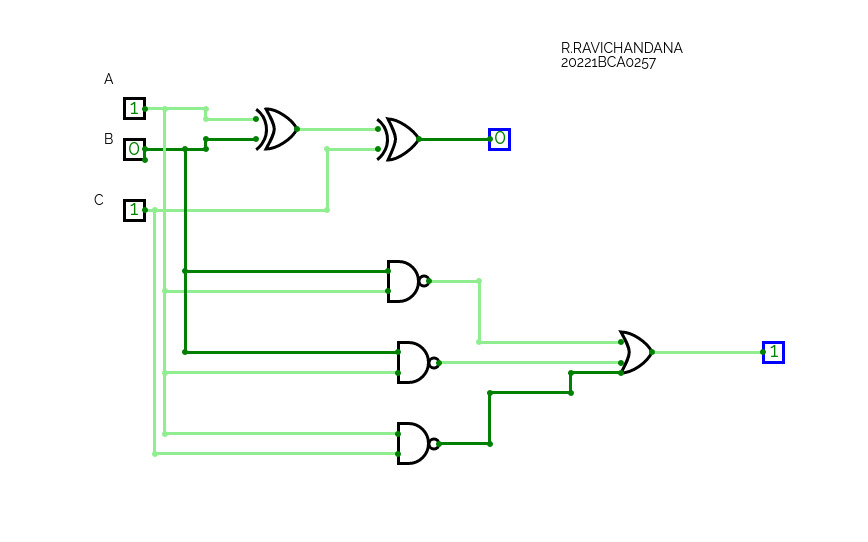

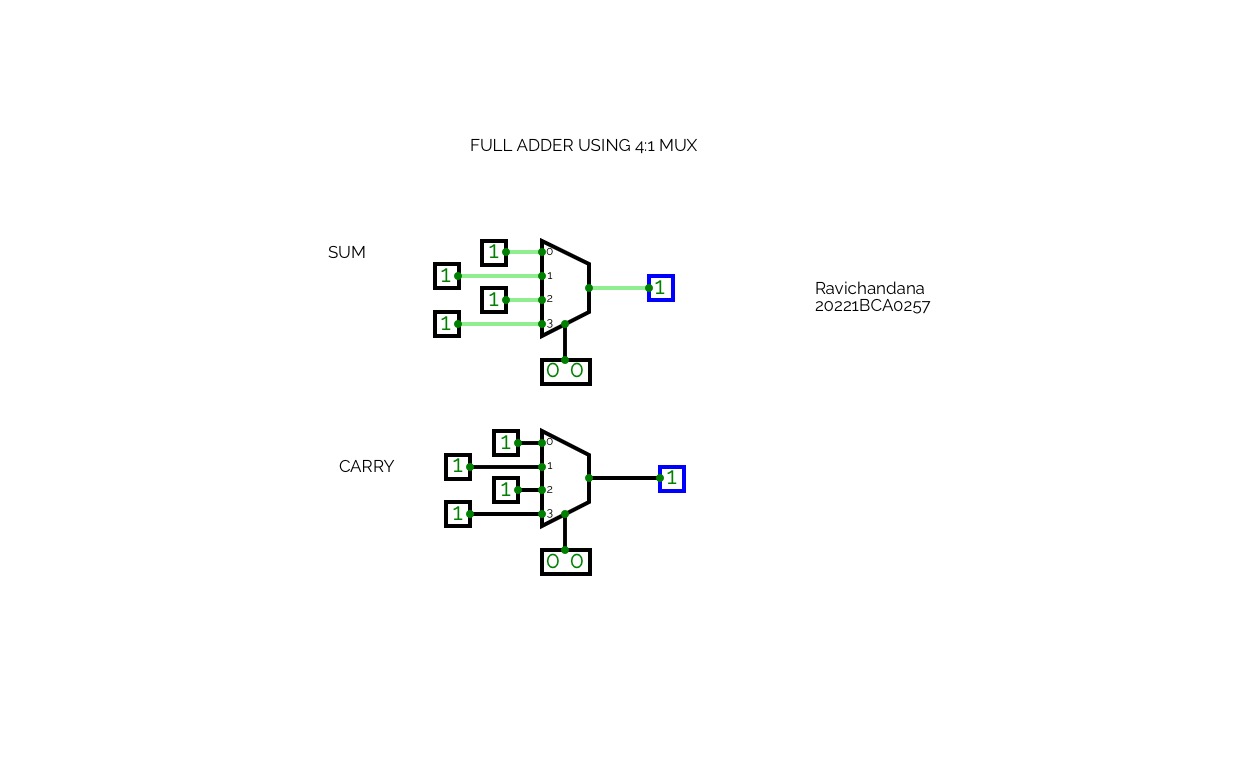

FULL ADDER

FULL ADDER

FULL ADDER

FULL ADDER

FULL ADDER

FULL ADDER

FULL ADDER

FULL ADDER

ENCODER BLOCK REPRESENTATION

ENCODER BLOCK REPRESENTATION

2:4 DECODER

2:4 DECODER

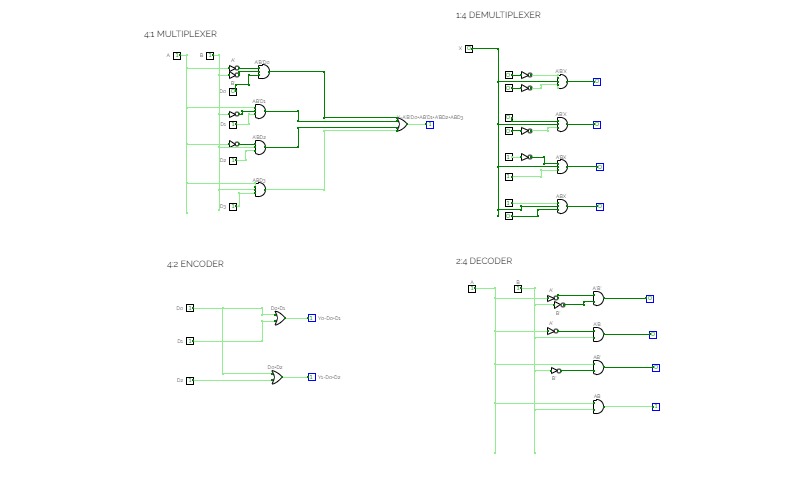

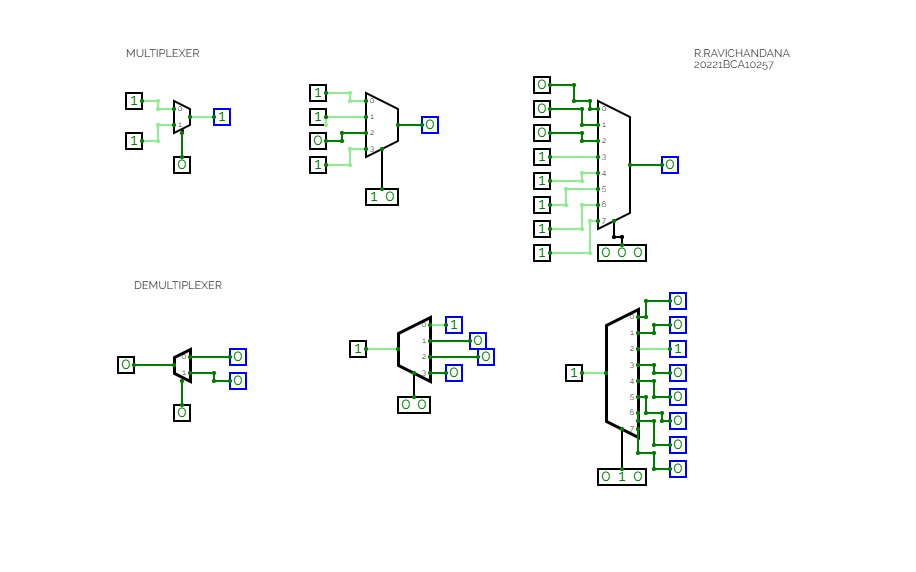

EXPERIMENT 2 - MULTIPLEXER AND DEMULTIPLEXER

EXPERIMENT 2 - MULTIPLEXER AND DEMULTIPLEXER

MUX DEMUX

MUX DEMUX

MUX 2

MUX 2

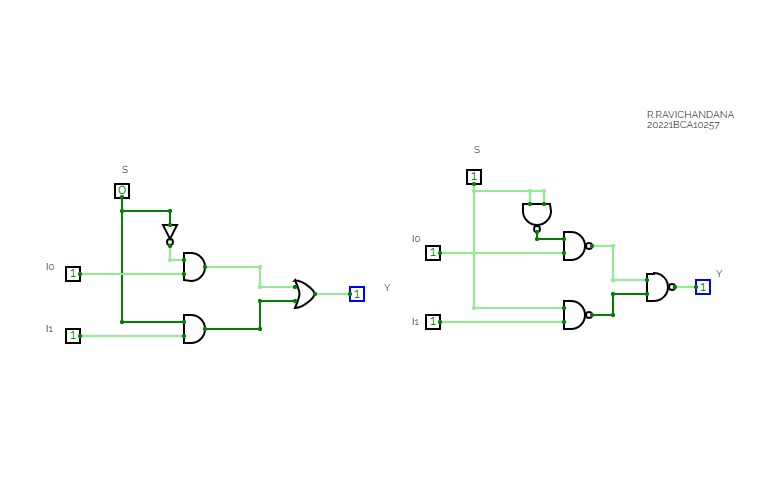

MUX 1

MUX 1

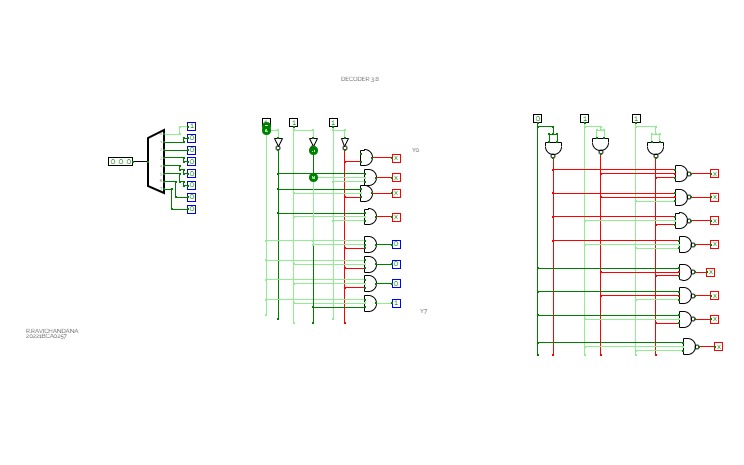

DECODER 3:8

DECODER 3:8

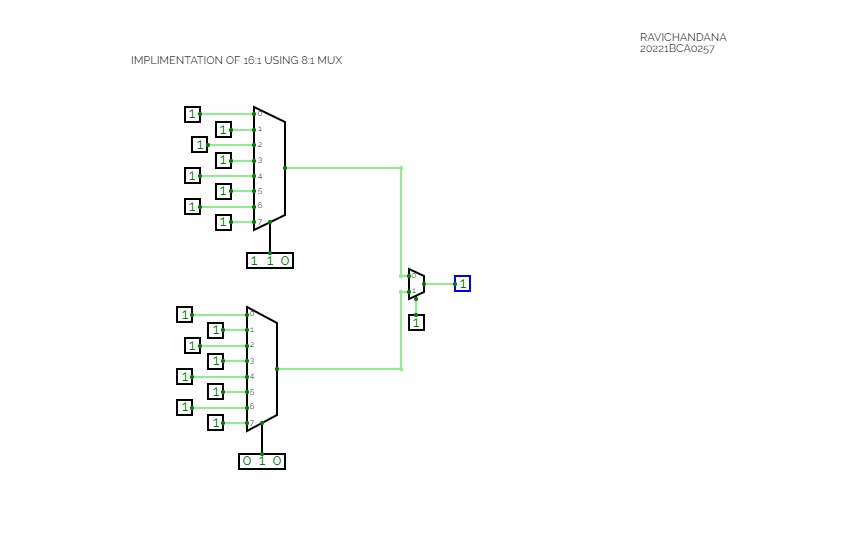

IMPLIMENT 16:1 USING 8:1

IMPLIMENT 16:1 USING 8:1

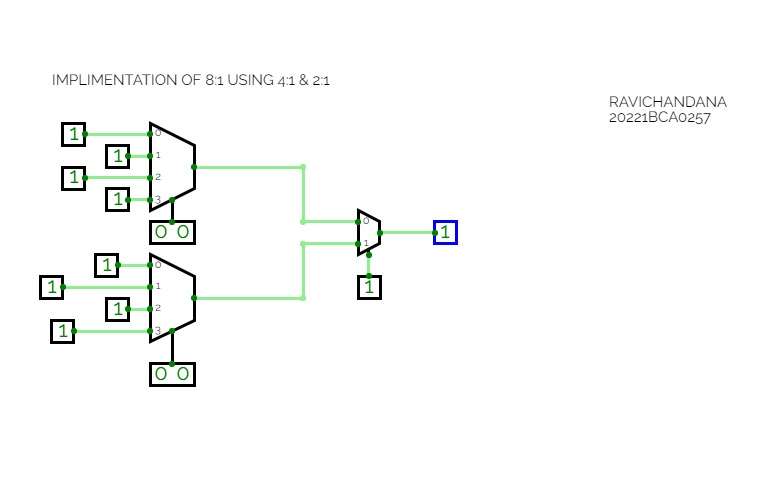

IMPLIMENTATION OF 8:1 USING 4:1 & 2:1

IMPLIMENTATION OF 8:1 USING 4:1 & 2:1

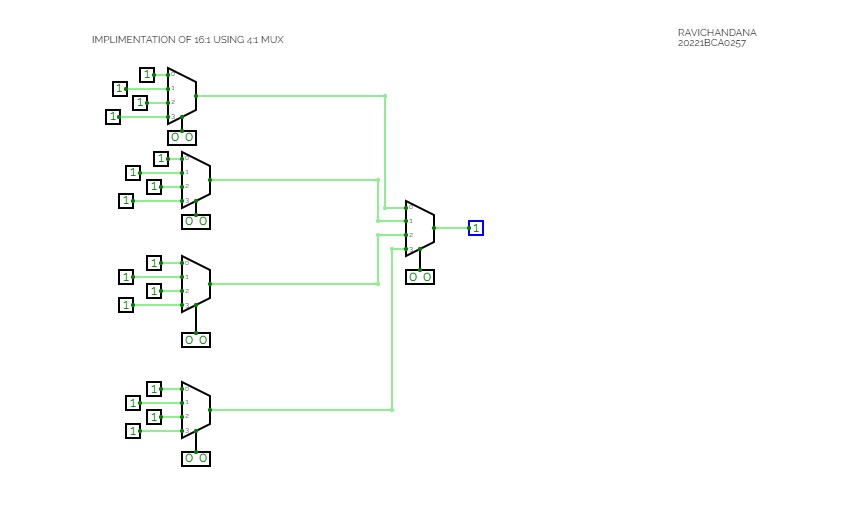

16:1 USING 4:1

16:1 USING 4:1

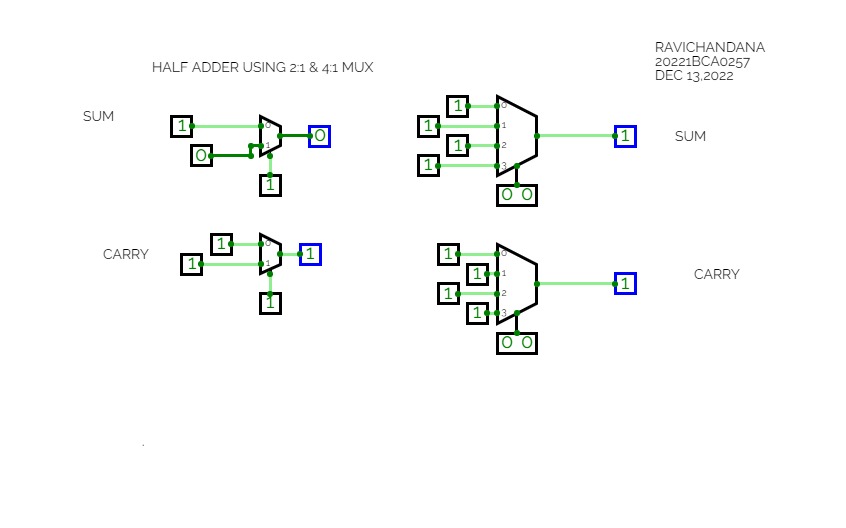

HALF ADDER USING 2:1 & 4:1 MUX

HALF ADDER USING 2:1 & 4:1 MUX

8:1 FA USING 4:1

8:1 FA USING 4:1

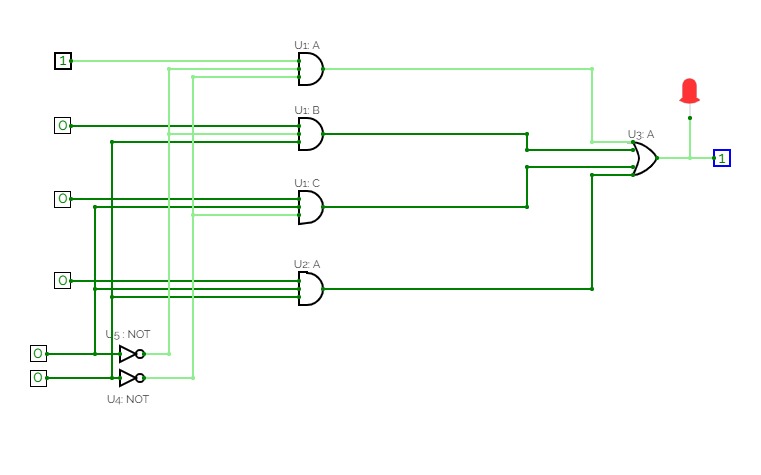

4:1 Mux using Logic Gates

4:1 Mux using Logic Gates

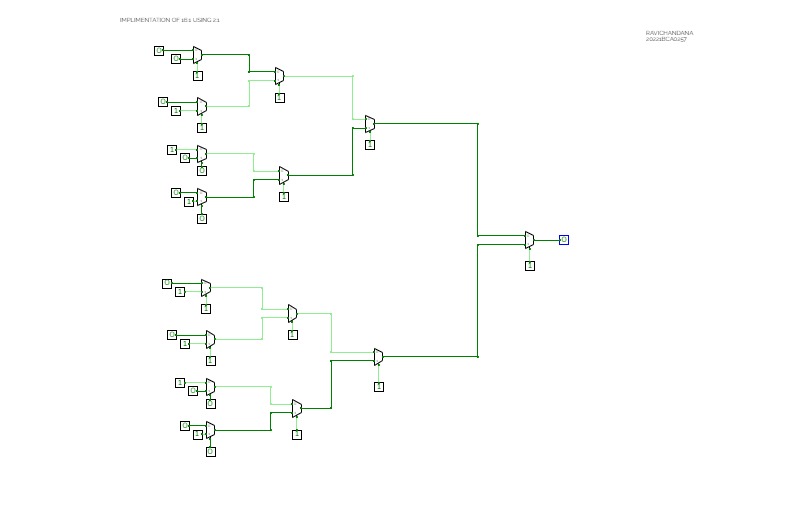

IMPLIMENTATION OF 16:1 USING 2:1

IMPLIMENTATION OF 16:1 USING 2:1

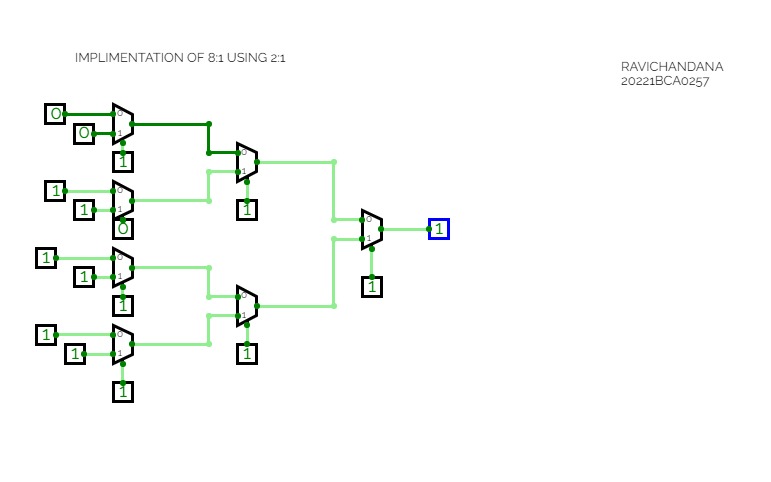

IMPLIMENTATION OF 8:1 USING 2:1

IMPLIMENTATION OF 8:1 USING 2:1

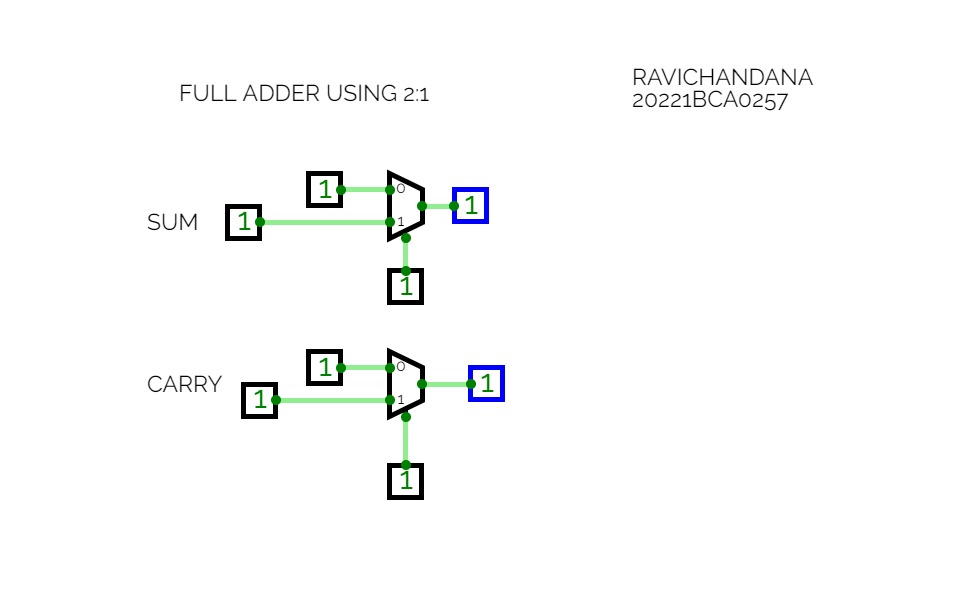

FA USING 2:1

FA USING 2:1

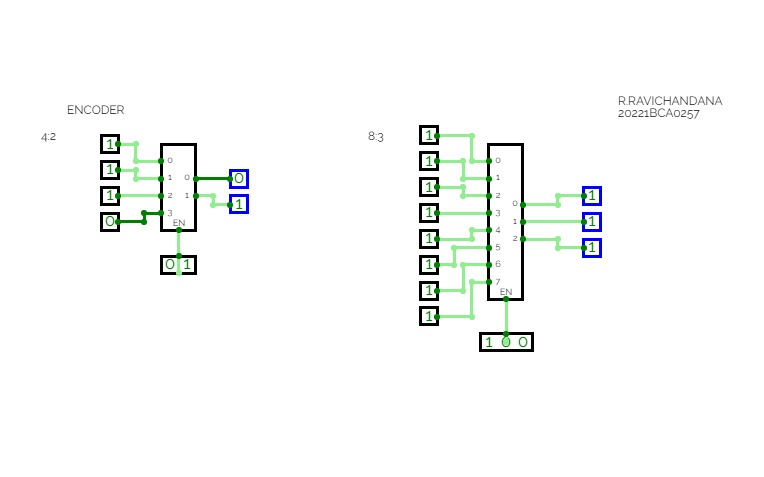

ENCODER BLOCK REPRESENTATION

ENCODER BLOCK REPRESENTATION

ENCODER BLOCK REPRESENTATION

ENCODER BLOCK REPRESENTATION