Utkarsh Gupta 21BCE0734

Member since: 2 years

Educational Institution: Not Entered

Country: Not Entered

MUX

MUX

4*1 MUX USING 2*1 MUX\

4*1 MUX USING 2*1 MUX\

4 :1 multiplexer using 2:1 Multiplexers

4 :1 multiplexer using 2:1 Multiplexers

IMPLEMENTATION OF 4*1 USING 2*1

IMPLEMENTATION OF 4*1 USING 2*1

2x1 mux using nand

2x1 mux using nand

2*1 USING SOP

2*1 USING SOP

2*1 MUX USING POS OAI

2*1 MUX USING POS OAI

2x1 mux using nor

2x1 mux using nor

2*1 USING NOR 21BCE0734

2*1 USING NOR 21BCE0734

16X1 MUX 21BCE3547

16X1 MUX 21BCE3547

16 X1 MUX 21BCE0734

16 X1 MUX 21BCE0734

half adder using mux

half adder using mux

Full Adder using Half Adder using mux Using Mux

Full Adder using Half Adder using mux Using Mux

FULL ADDER USING HALF ADDER IN MUX 21BCE0734

FULL ADDER USING HALF ADDER IN MUX 21BCE0734

8x1 mux 21BCE3547

8x1 mux 21BCE3547

8X 1 MUX 21BCE0734

8X 1 MUX 21BCE0734

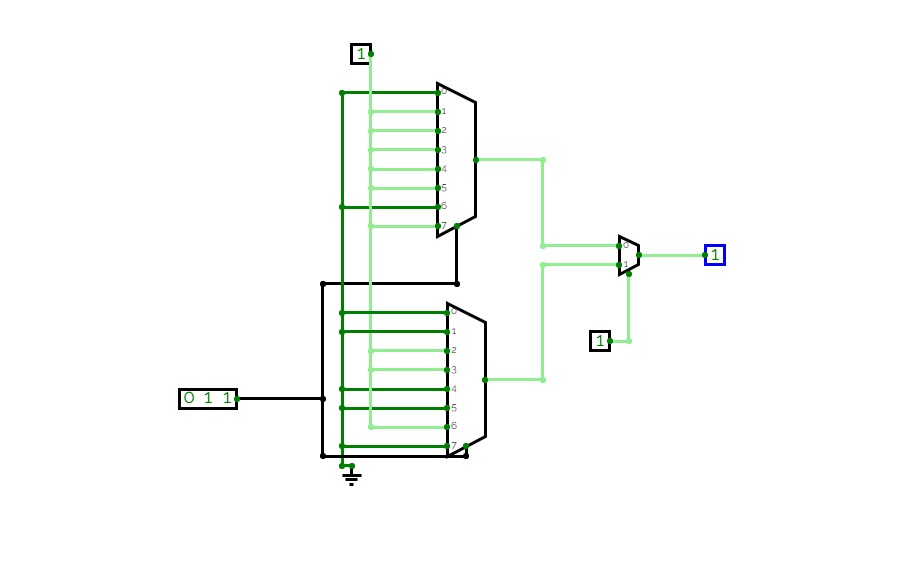

3*8 decoder using 2*4 decoder

3*8 decoder using 2*4 decoder

3X8 DECODER USING 2X4 DECODER

3X8 DECODER USING 2X4 DECODER

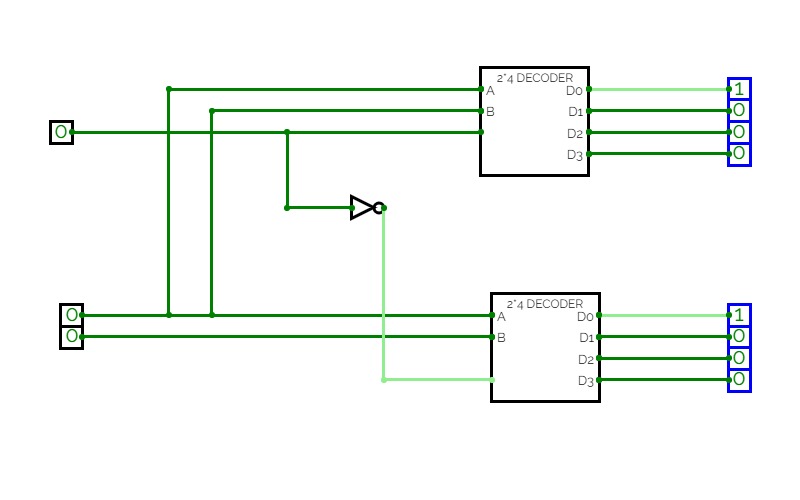

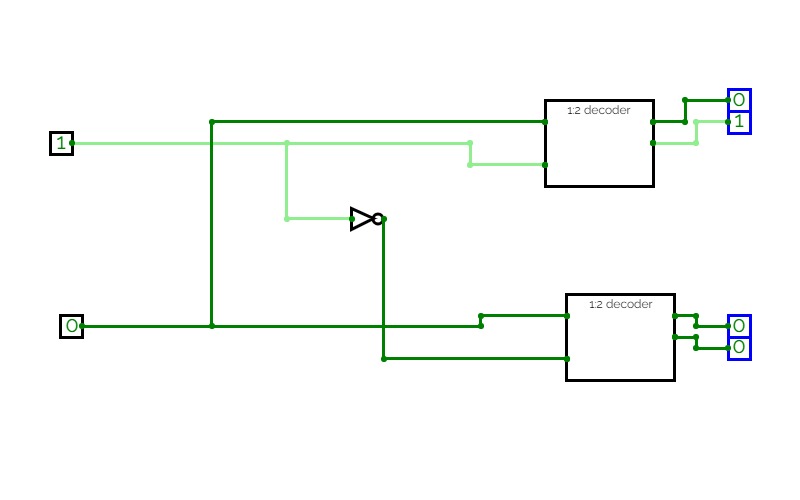

2:4 decoder using 1:2 decoder

2:4 decoder using 1:2 decoder

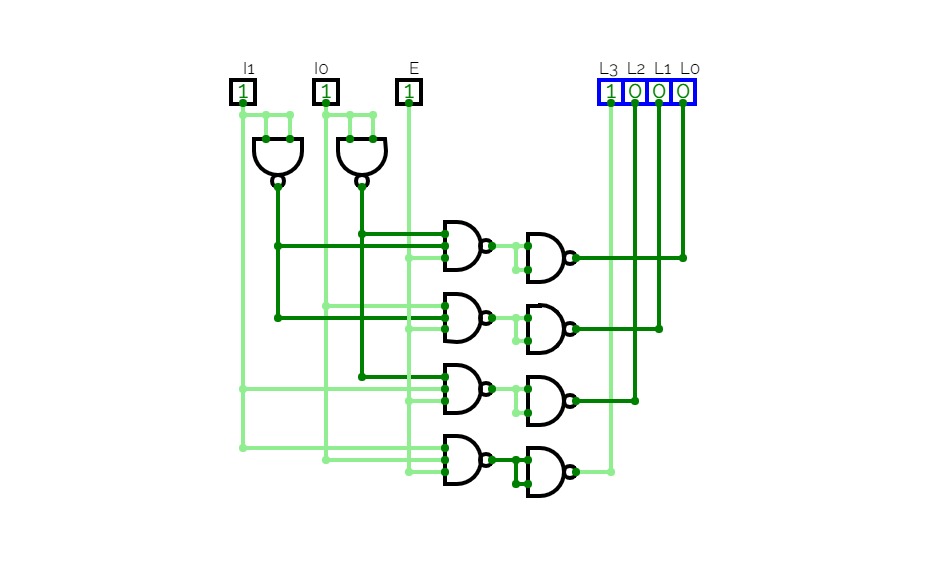

AOI logic circuit of 2:4 Decoder

AOI logic circuit of 2:4 Decoder

UntitledAOI LOGIC USING 2:4 DECODER 21BCE0734

UntitledAOI LOGIC USING 2:4 DECODER 21BCE0734

NAND logic circuit of 2:4 Decoder

NAND logic circuit of 2:4 Decoder

NAND LOGIC USING 2:4 DECODER 21BCE0734

NAND LOGIC USING 2:4 DECODER 21BCE0734

AOI logic circuit of 4:2 encoder

AOI logic circuit of 4:2 encoder

NAND logic circuit of 4:2 encoder

NAND logic circuit of 4:2 encoder

1X8 IN DEMUX

1X8 IN DEMUX

AOI LOGIC CIRCUIT USING 4:2 DECODER

AOI LOGIC CIRCUIT USING 4:2 DECODER

NAND LOGIC CIRCUIT USING 4:2 DECODER

NAND LOGIC CIRCUIT USING 4:2 DECODER

1x16 decoder 21bce3547

1x16 decoder 21bce3547

HALF ADDER USING MUX 21BCE0734

HALF ADDER USING MUX 21BCE0734

FULL SUBTRACTOR USING MUX 21BCE0734

FULL SUBTRACTOR USING MUX 21BCE0734

2 input OR Logic gate using a 2:1 Multiplexer

2 input OR Logic gate using a 2:1 Multiplexer

Untitled

Untitled

2 input OR Logic gate using a 2:1 Multiplexer

2 input OR Logic gate using a 2:1 Multiplexer

Untitled

Untitled

4 BIT ALU _21BCE0734

4 BIT ALU _21BCE0734

Untitled

Untitled

21BCE0734 SET B

21BCE0734 SET B

JK flipflop and T flipflop using D flipflop

JK flipflop and T flipflop using D flipflop

16:1 MUX using 8:1 MUX

16:1 MUX using 8:1 MUX

16*1 mux using 8*1

16*1 mux using 8*1

2:1 multiplexer IOA

2:1 multiplexer IOA

Untitled

Untitled

2*1 MUX USING SOP -AOI

2*1 MUX USING SOP -AOI

full subtractor using mux

full subtractor using mux

1X16 DECODER 21BCE0734

1X16 DECODER 21BCE0734

3x8 decoder 21bce3547

3x8 decoder 21bce3547

2X4 DECODER USING 1X2 DECODER

2X4 DECODER USING 1X2 DECODER

half subtractor using mux

half subtractor using mux

4 BIT ALU

4 BIT ALU

HALF SUBTRACTOR USING MUX

HALF SUBTRACTOR USING MUX

1 BIT ALU

1 BIT ALU