Chakrabarti Shailee Chandan 21BCE2911

Member since: 2 years

Educational Institution: Not Entered

Country: Not Entered

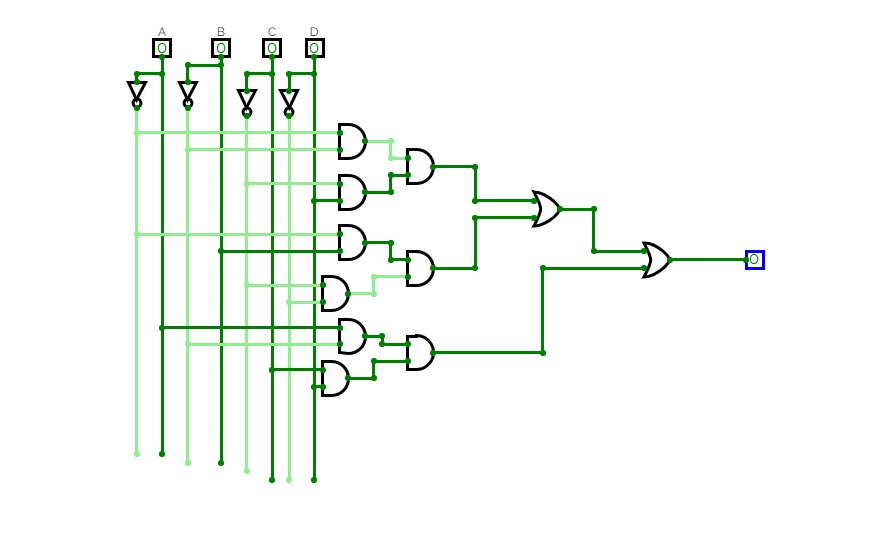

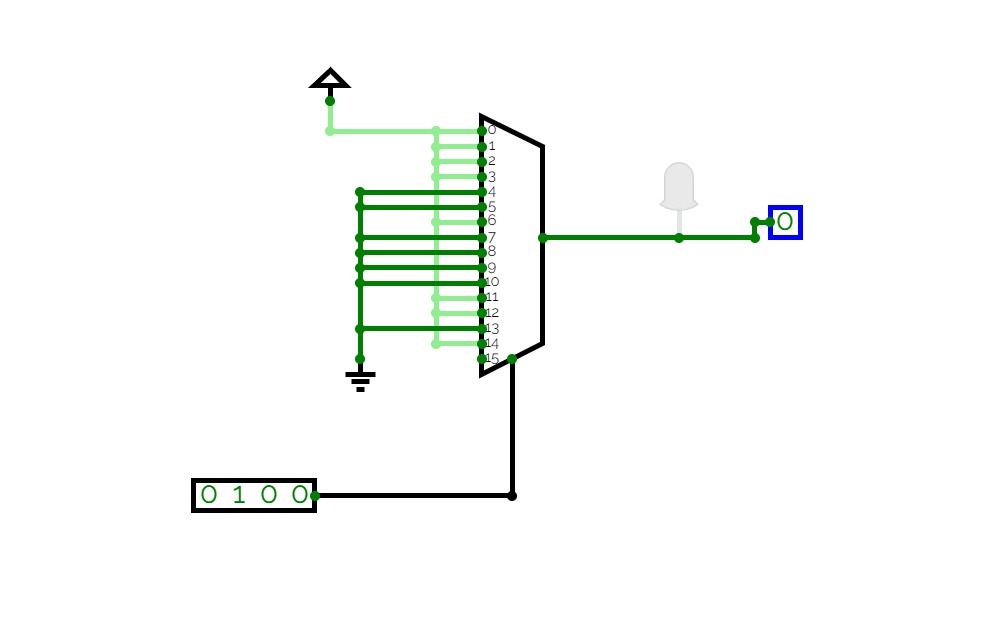

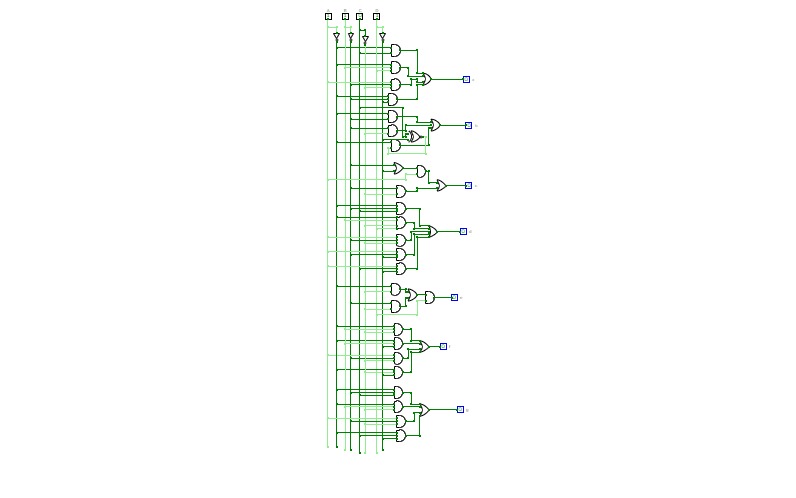

4:16_decoder

4:16_decoder

coomon_anode_dc

coomon_anode_dc

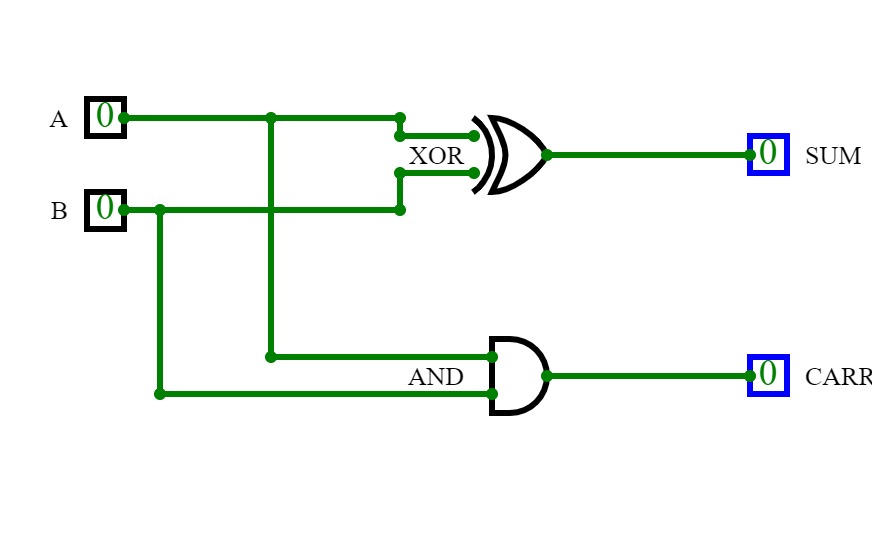

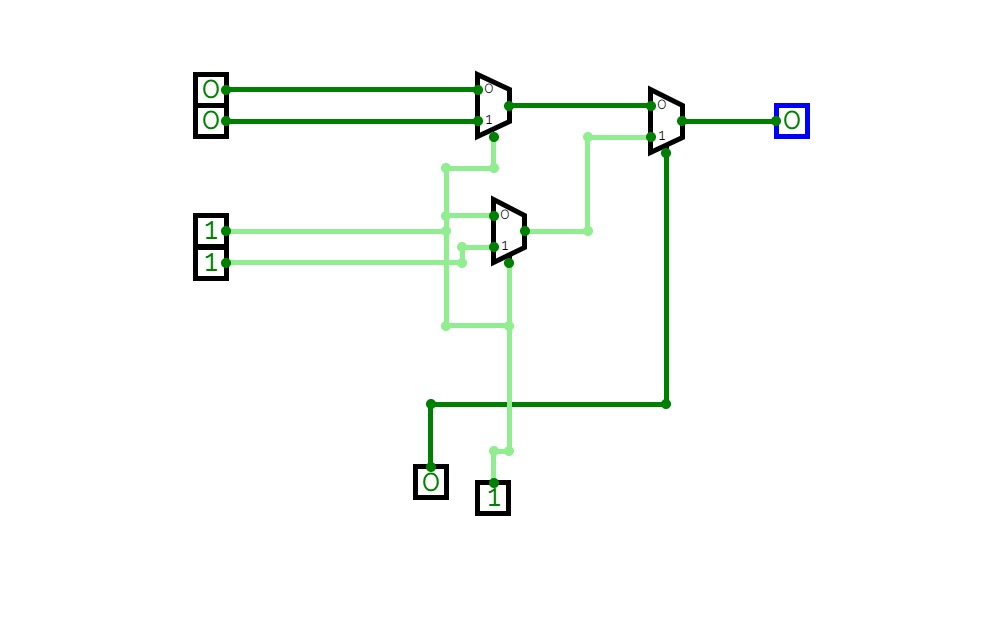

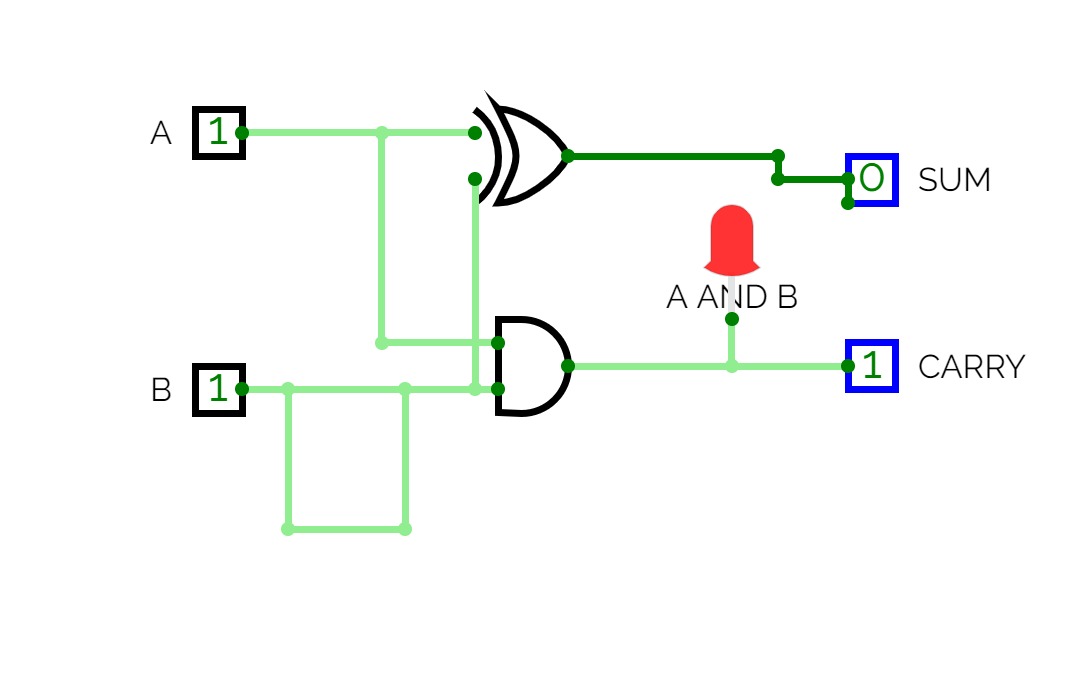

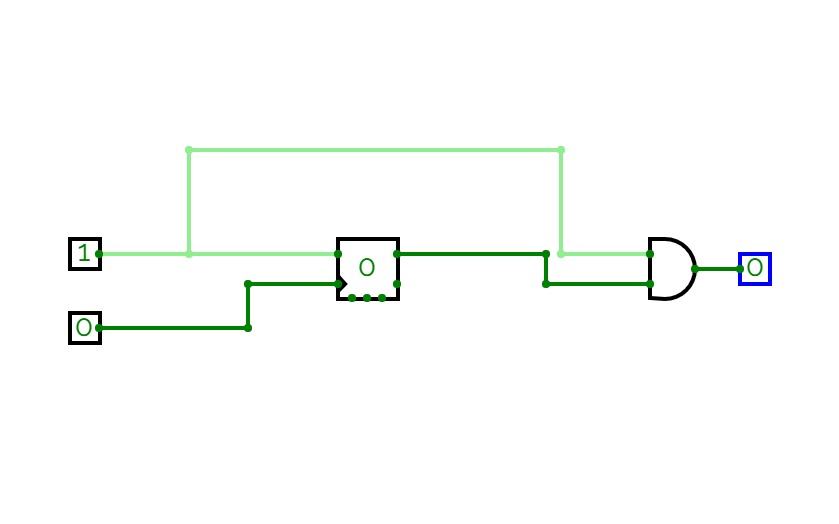

half_adder_21bce2911

half_adder_21bce2911

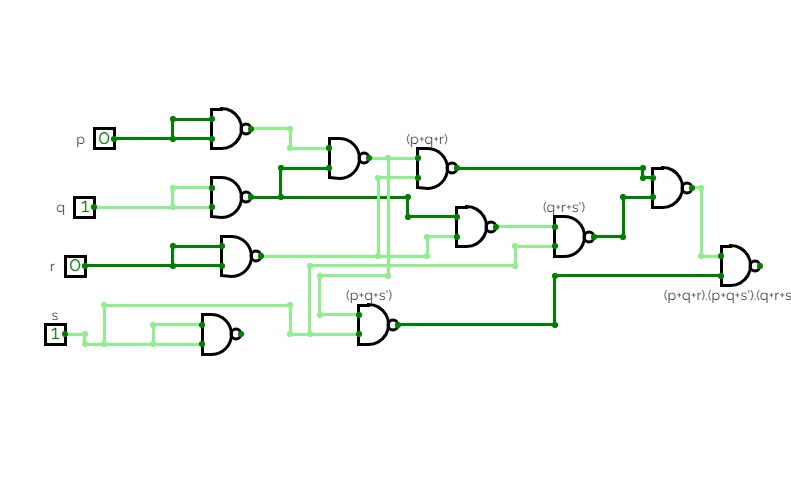

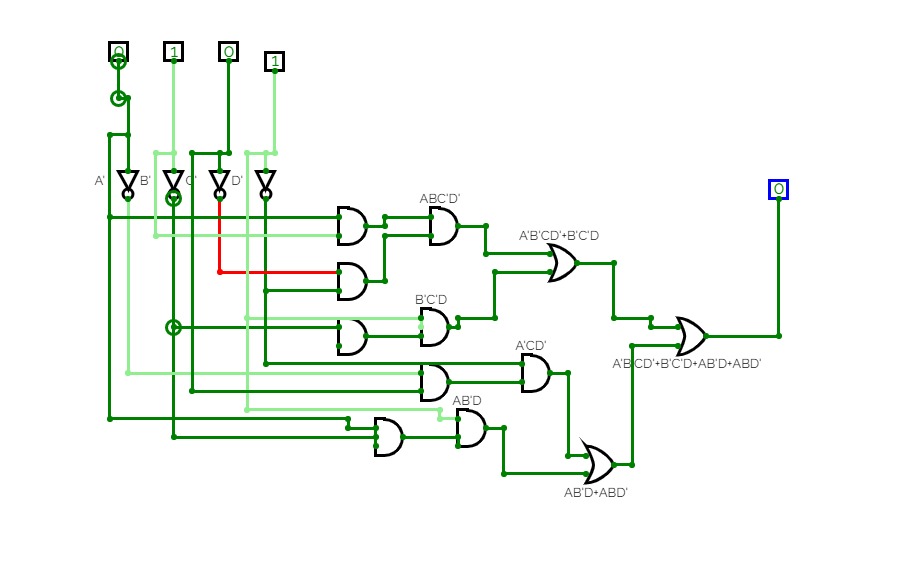

DA_4_AND_OR

DA_4_AND_OR

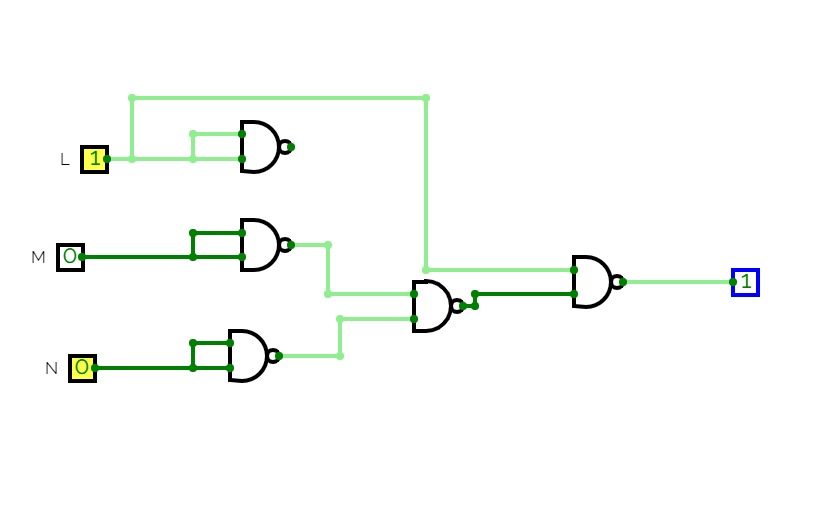

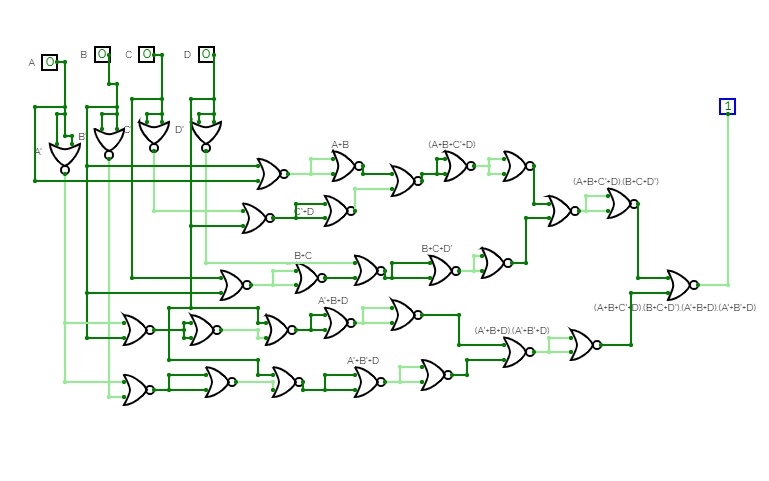

Q1_b

Q1_b

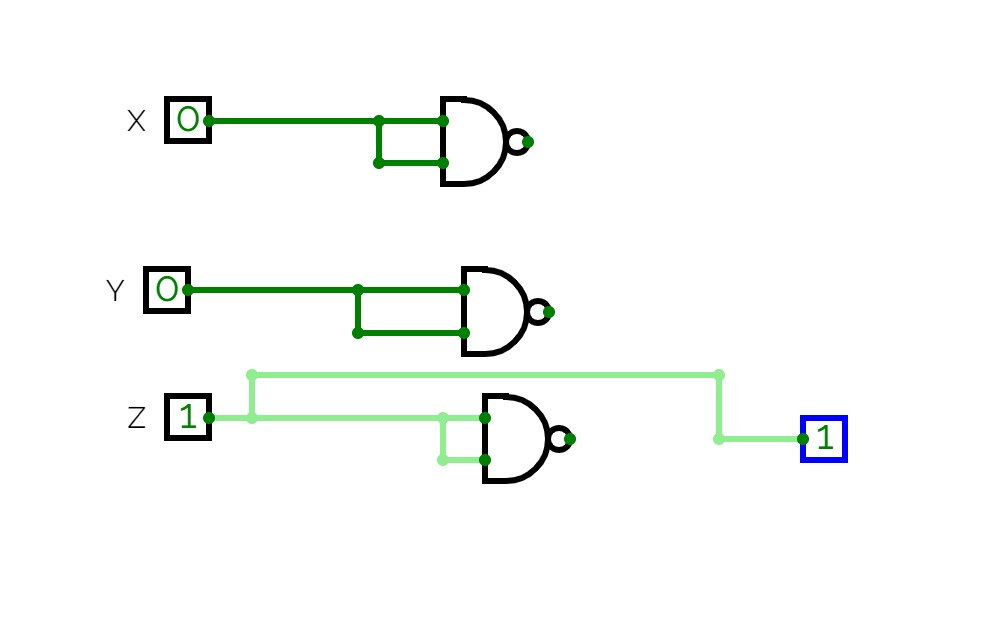

Q3_a

Q3_a

Q3(b)

Q3(b)

Q4_b

Q4_b

Q5_1

Q5_1

q4_a

q4_a

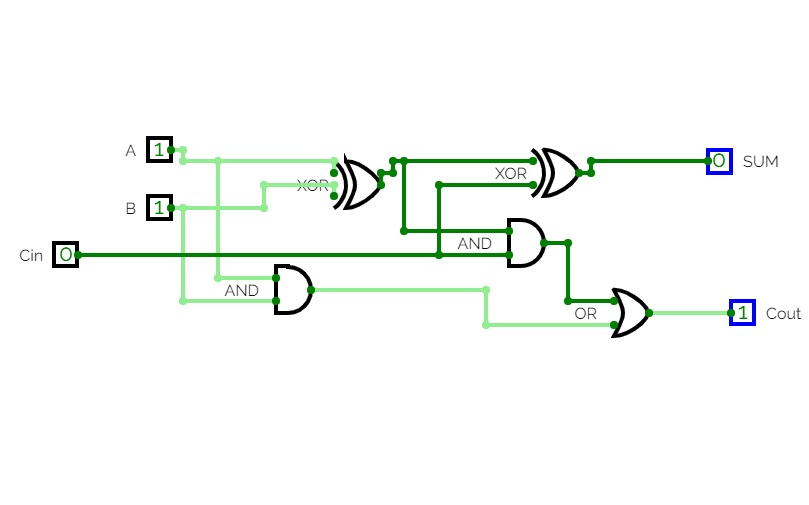

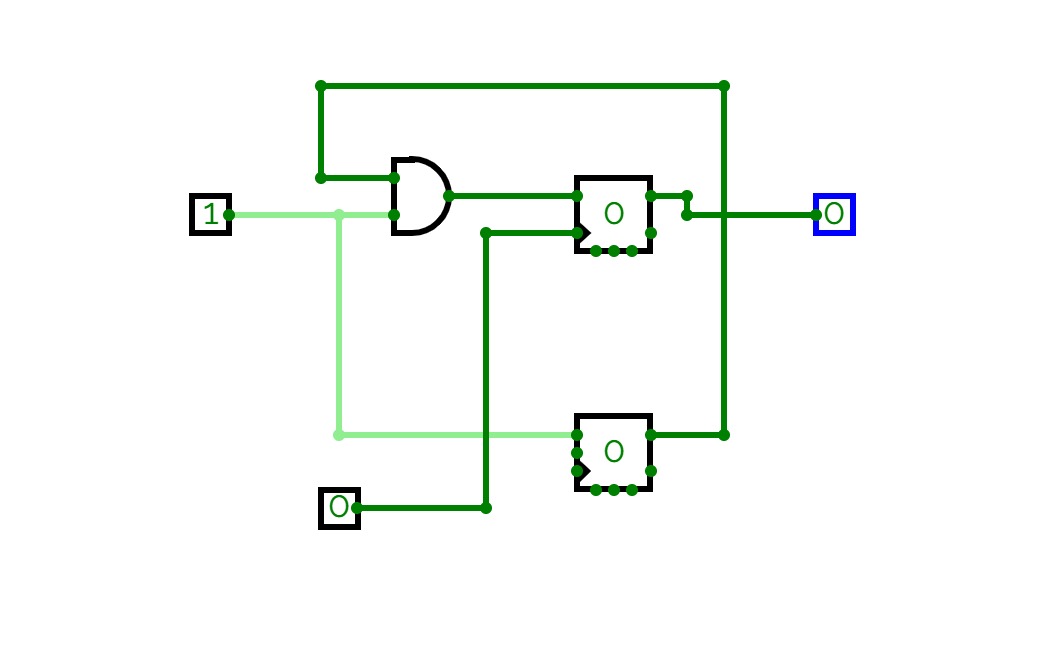

full_adder_21bce2911

full_adder_21bce2911

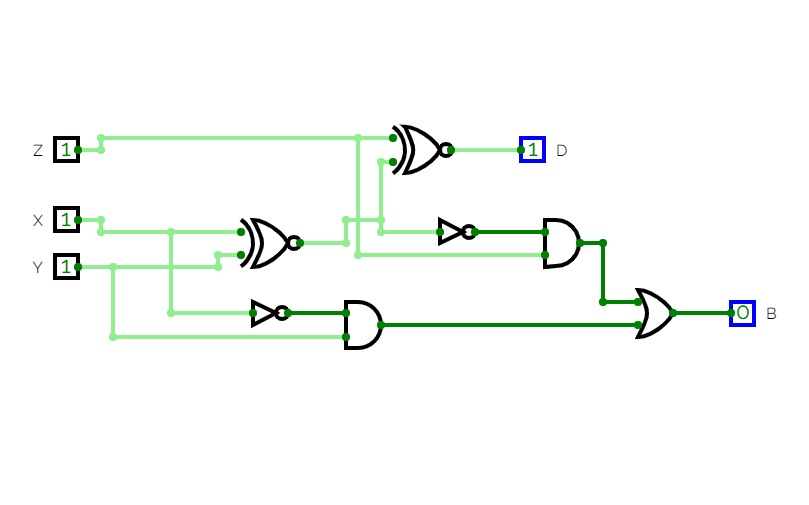

full_subtractor_21bce2911

full_subtractor_21bce2911

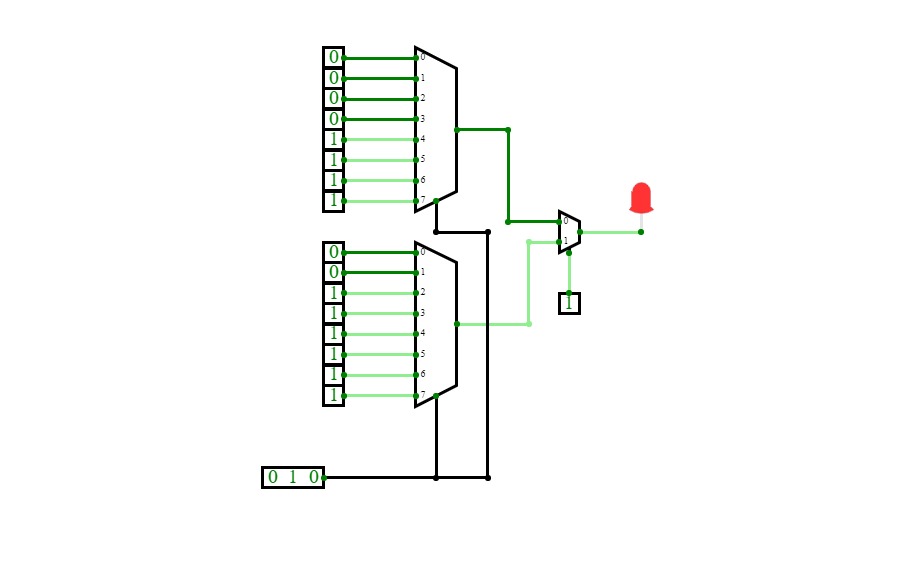

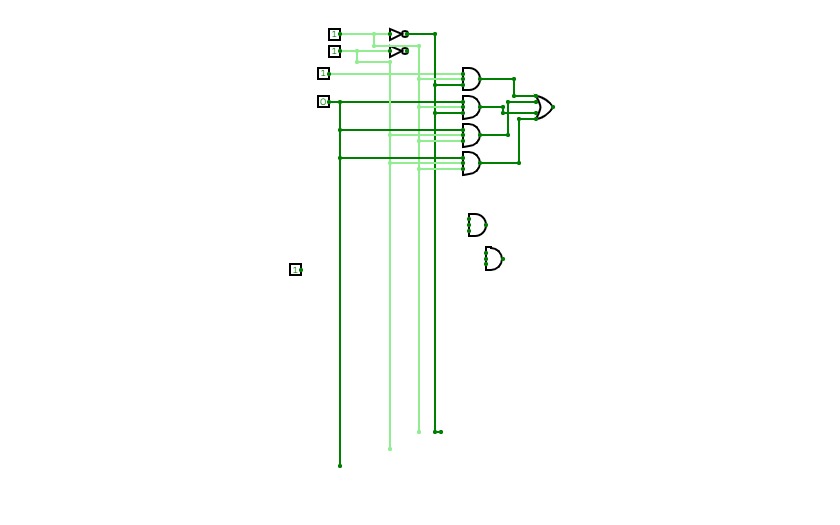

practice_16x1

practice_16x1

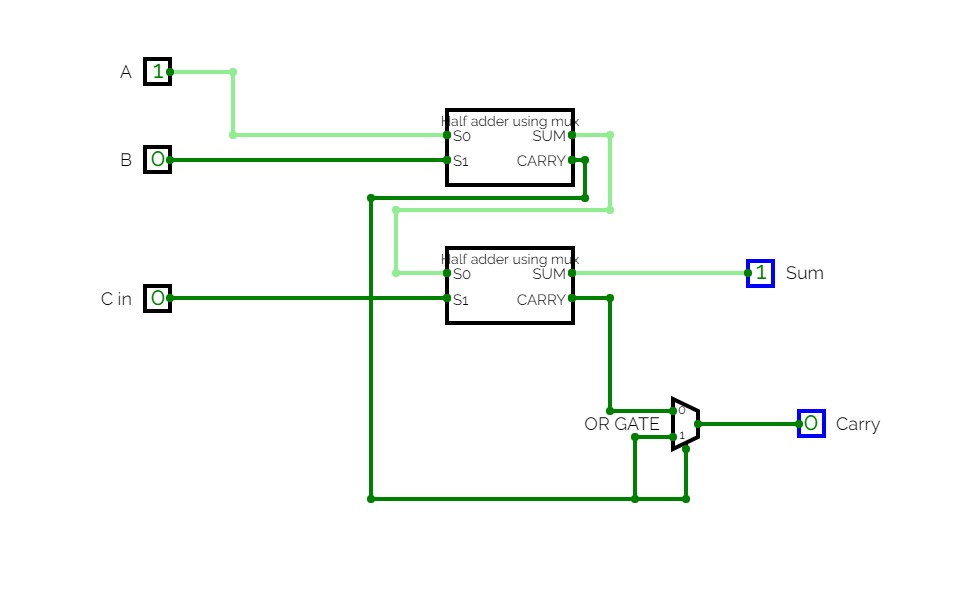

Full Adder using Half Adder using mux Using Mux

Full Adder using Half Adder using mux Using Mux

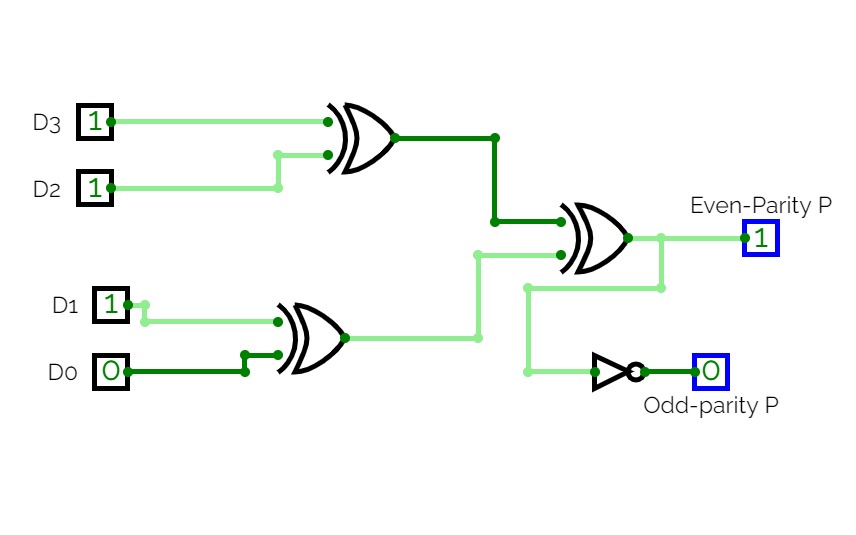

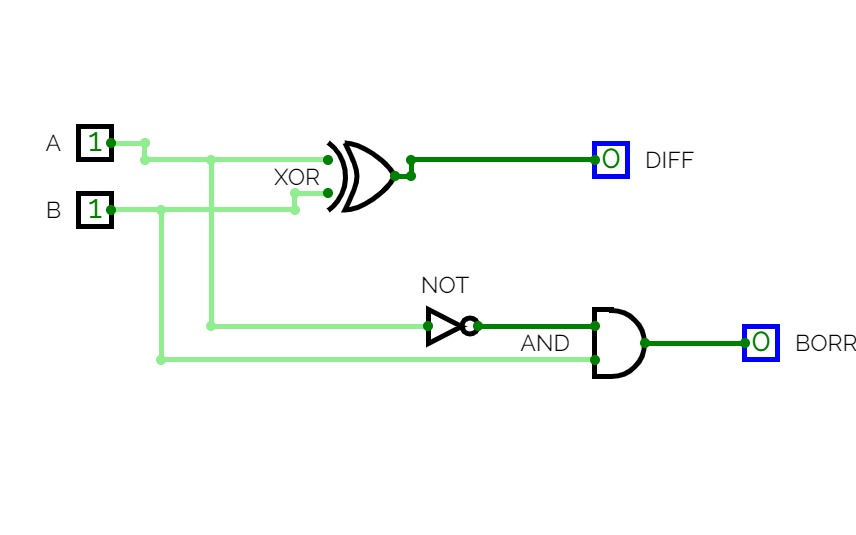

hs_21bce2911

hs_21bce2911

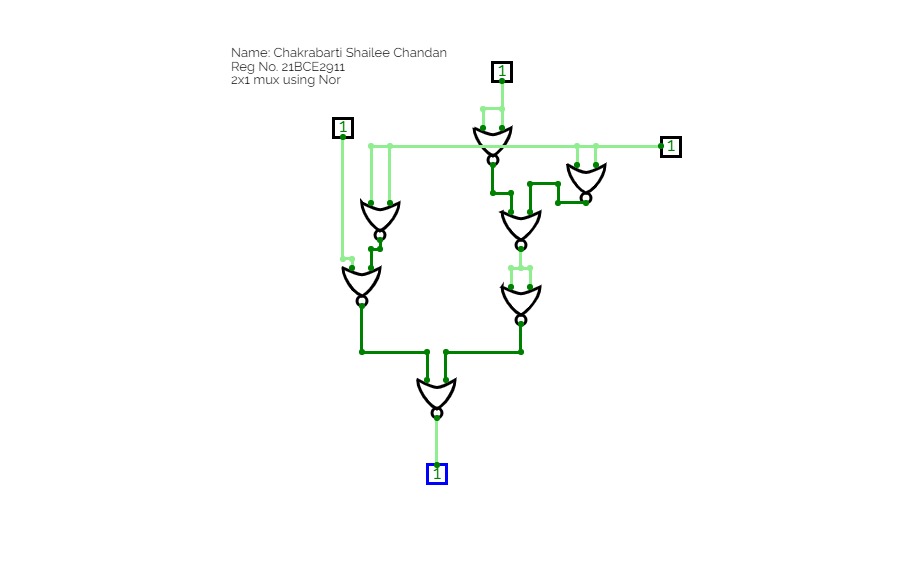

2x1_mux_using_nor

2x1_mux_using_nor

16x1_using_8x1_and_2x1

16x1_using_8x1_and_2x1

4x1_using_2x1

4x1_using_2x1

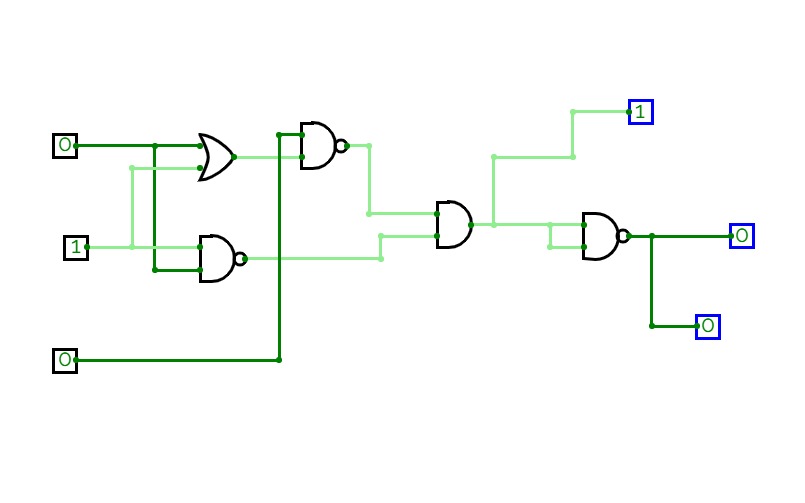

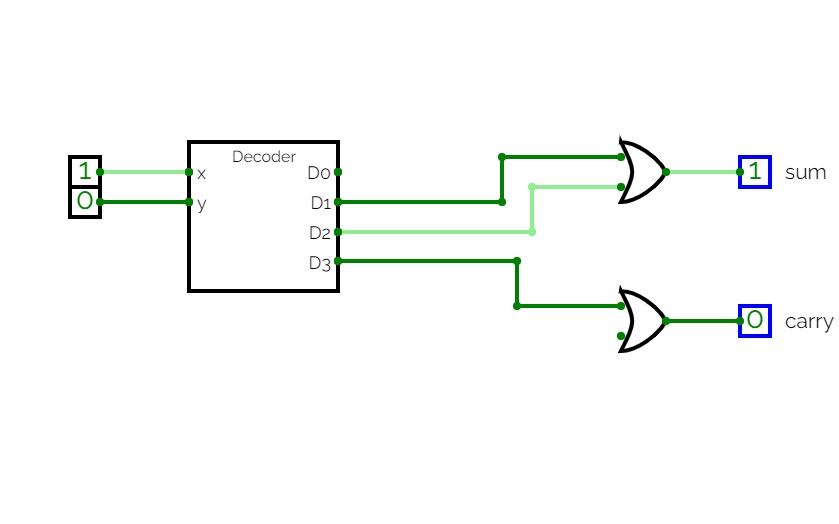

half_adder_using_decoder

half_adder_using_decoder

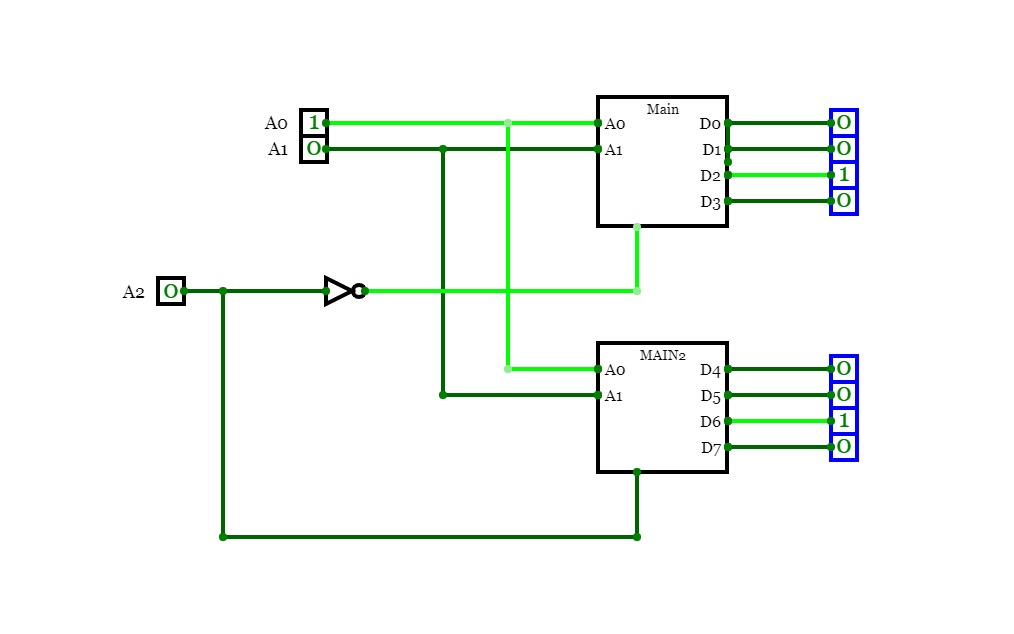

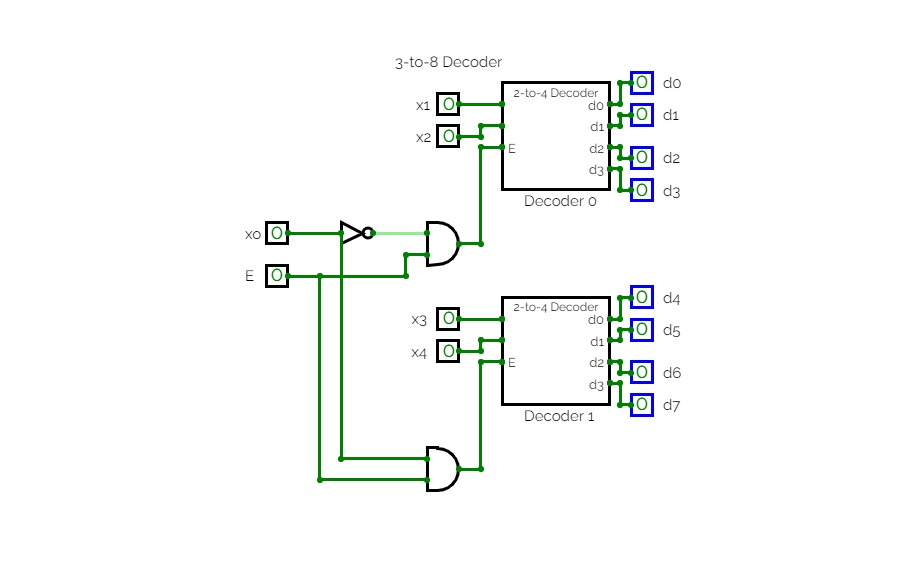

3x8_using_2x4_decoder

3x8_using_2x4_decoder

t1_34_21bce2911_1

t1_34_21bce2911_1

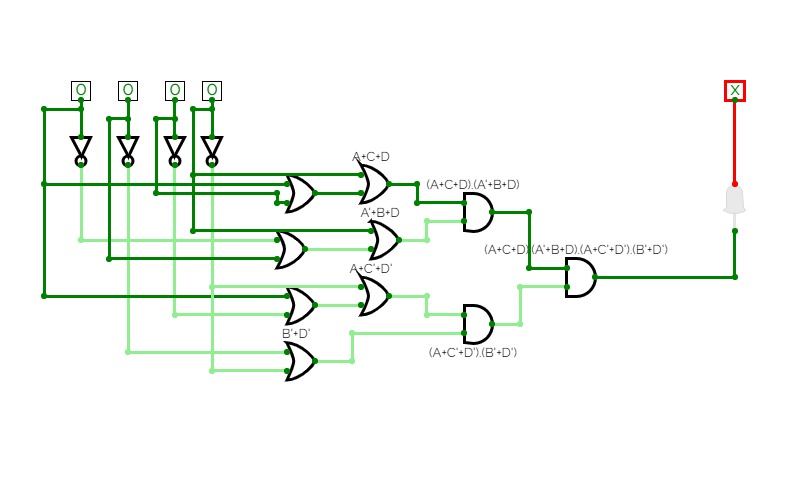

t1_34_21bce2911_pos_nor

t1_34_21bce2911_pos_nor

t1_34_21bce2911

t1_34_21bce2911

Task_2_example

Task_2_example

t1_34_21bce2911_SOP2

t1_34_21bce2911_SOP2

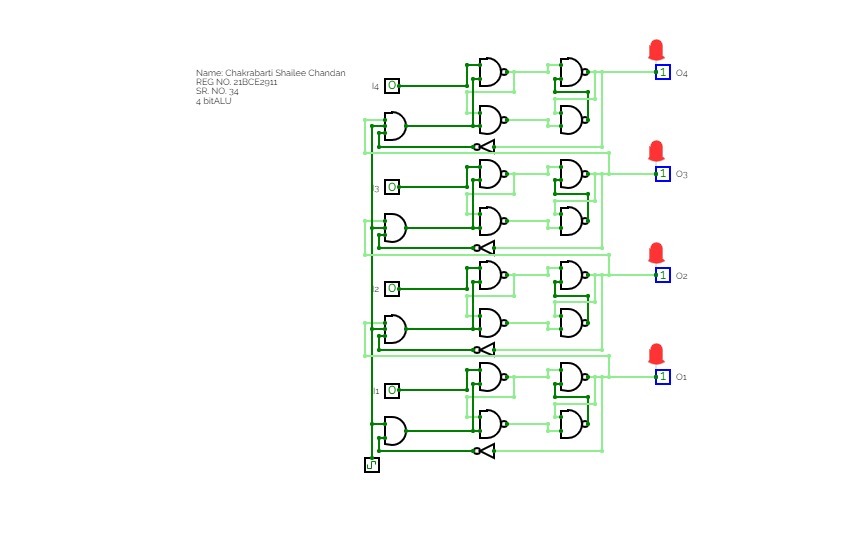

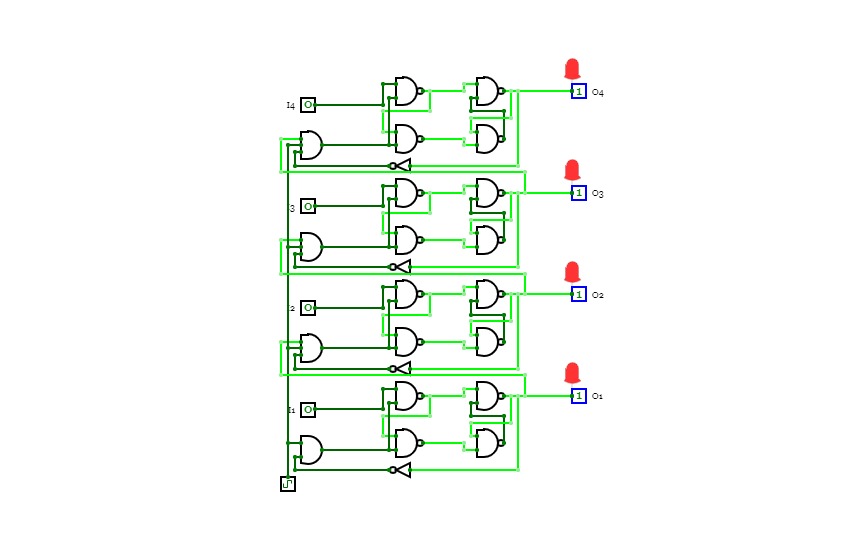

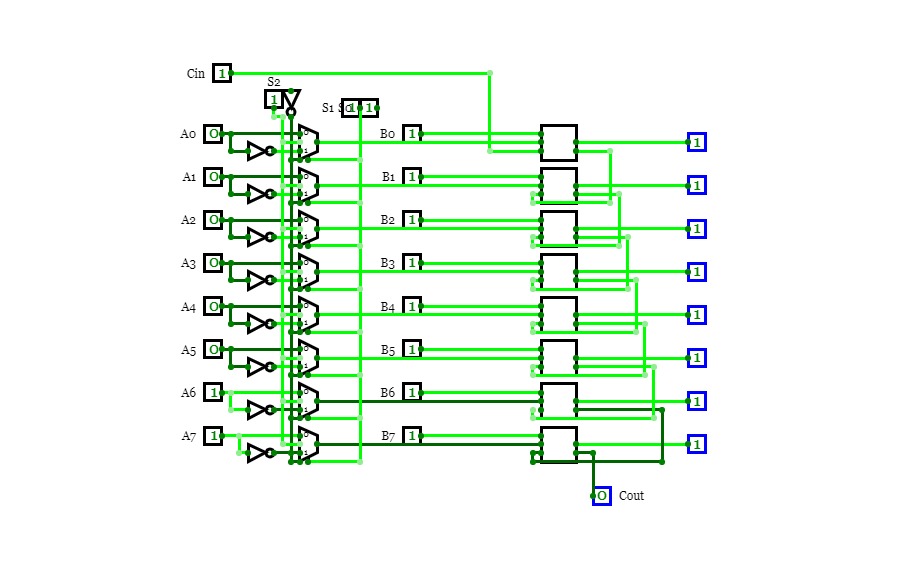

4-bit ALU

4-bit ALU

T1_34_VIVA_CIRCUIT_21BCE2911

T1_34_VIVA_CIRCUIT_21BCE2911

VIVA_34_21BCE2911_Q2

VIVA_34_21BCE2911_Q2

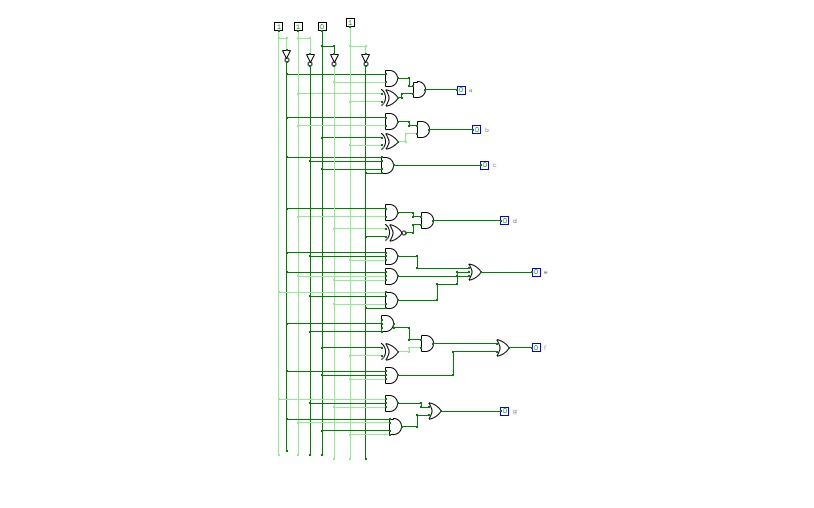

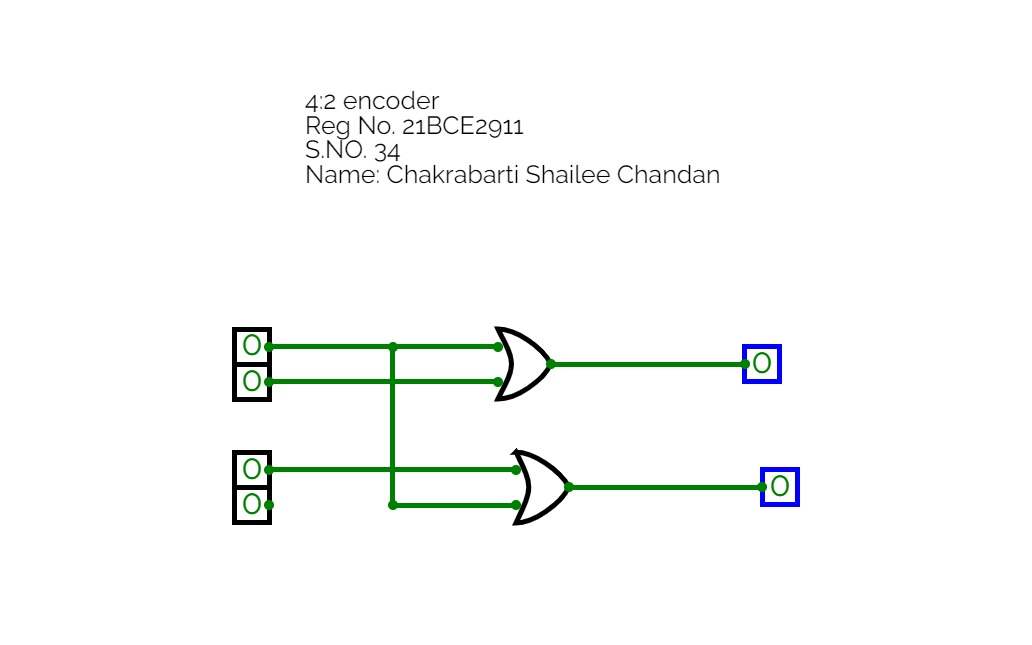

4:2 Encoder

4:2 Encoder

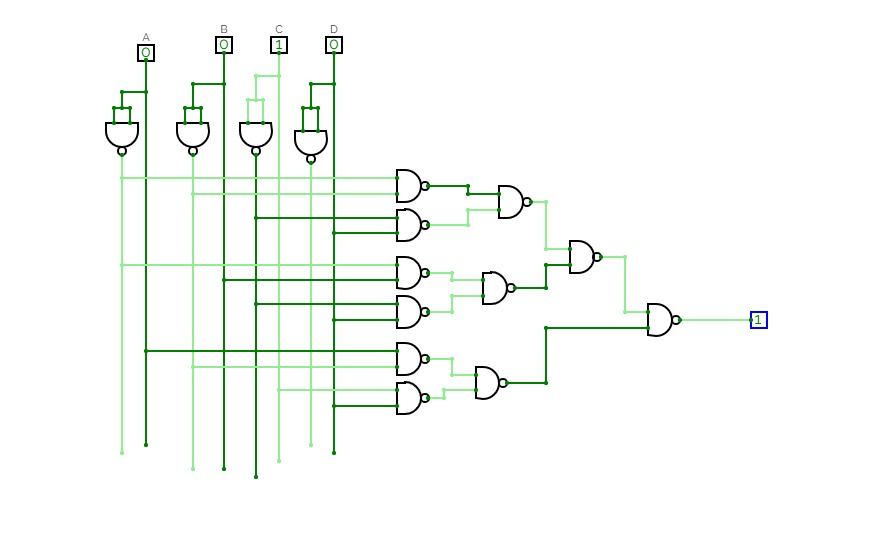

T1_34_21BCE2911_VIVA_Q1

T1_34_21BCE2911_VIVA_Q1

T1_34_21BCE2911_Q2

T1_34_21BCE2911_Q2

2x1_using_and_or

2x1_using_and_or

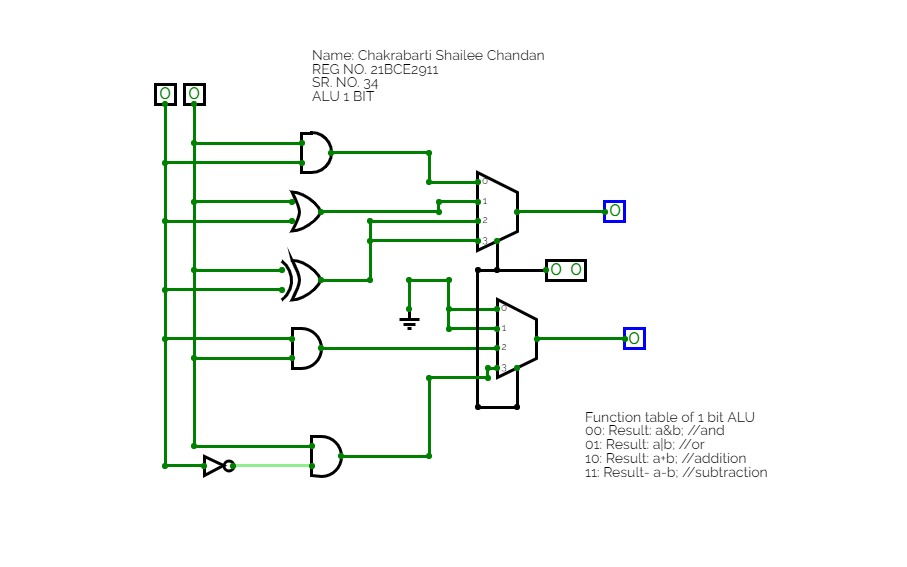

1_BIT_ALU

1_BIT_ALU

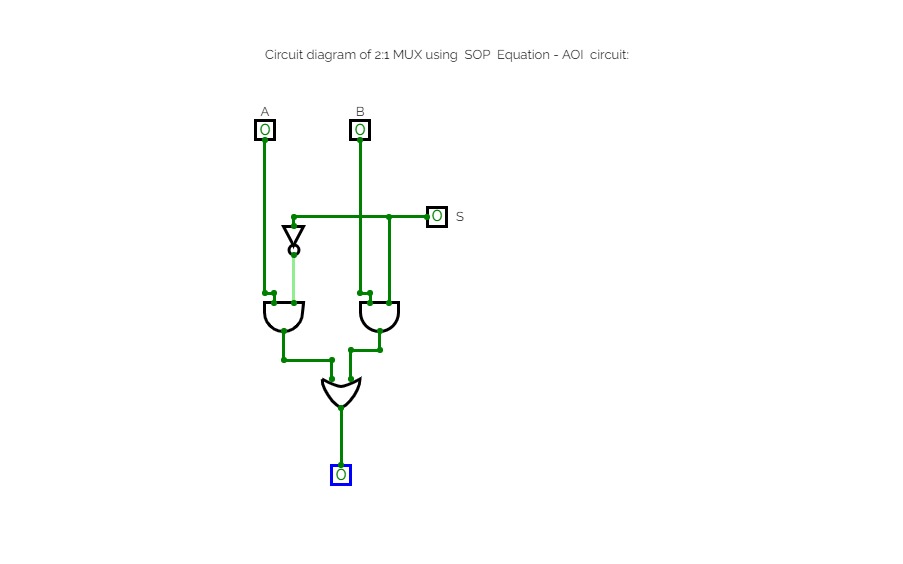

2x1_SOP

2x1_SOP

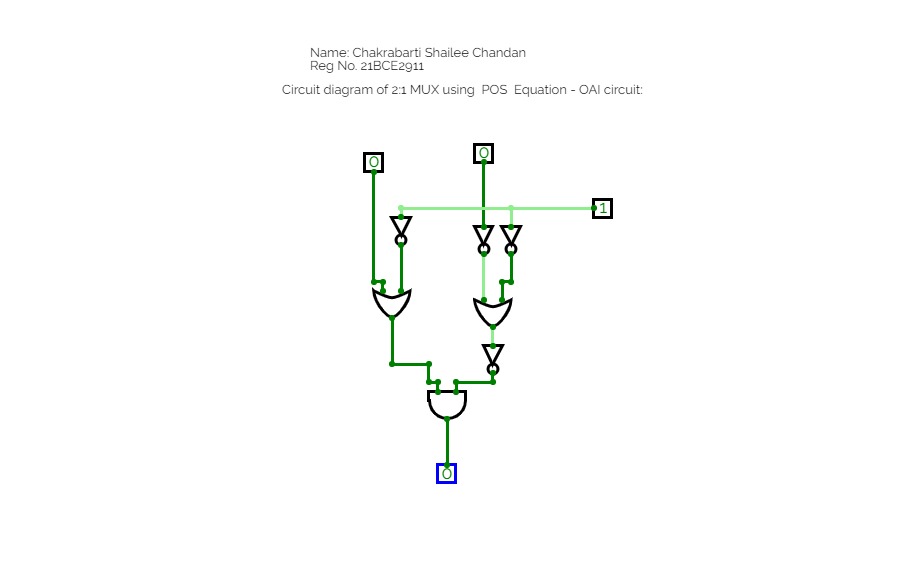

2x1_mux_POS

2x1_mux_POS

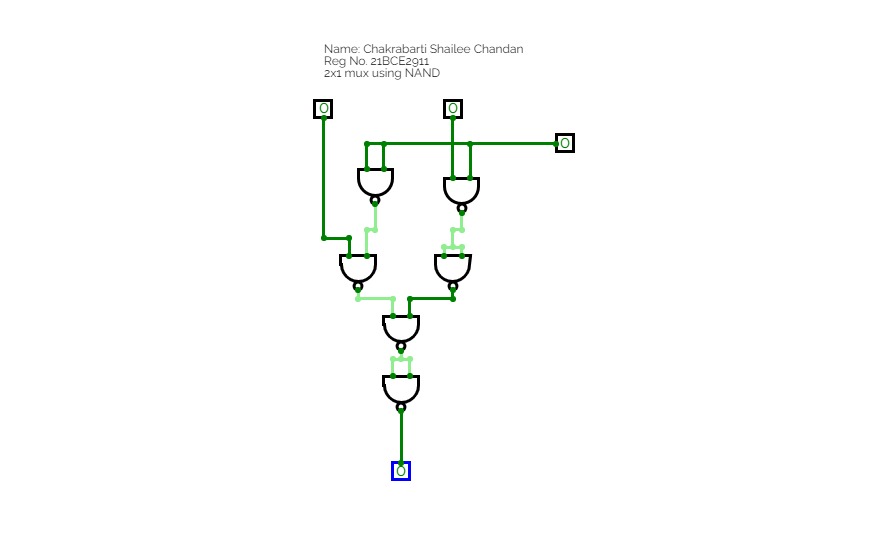

2X1_mux_nand

2X1_mux_nand

implement_16x1_t1_t2

implement_16x1_t1_t2

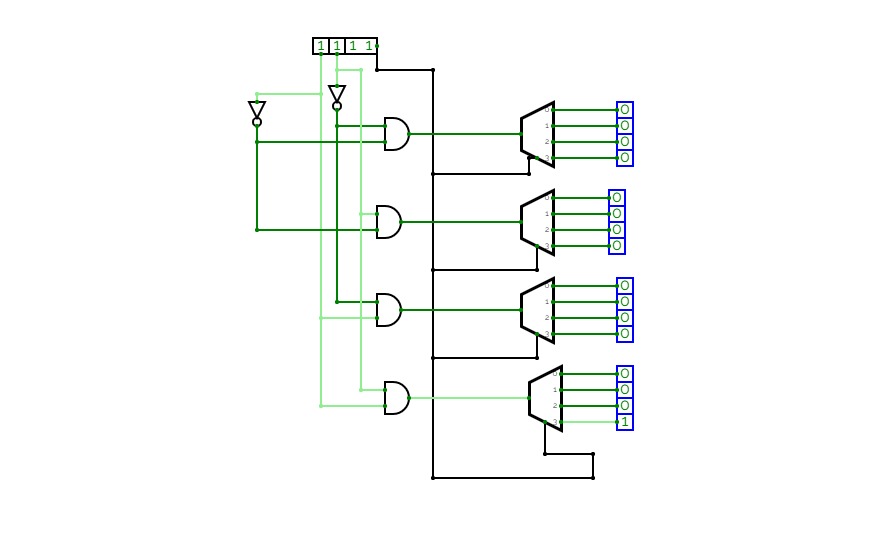

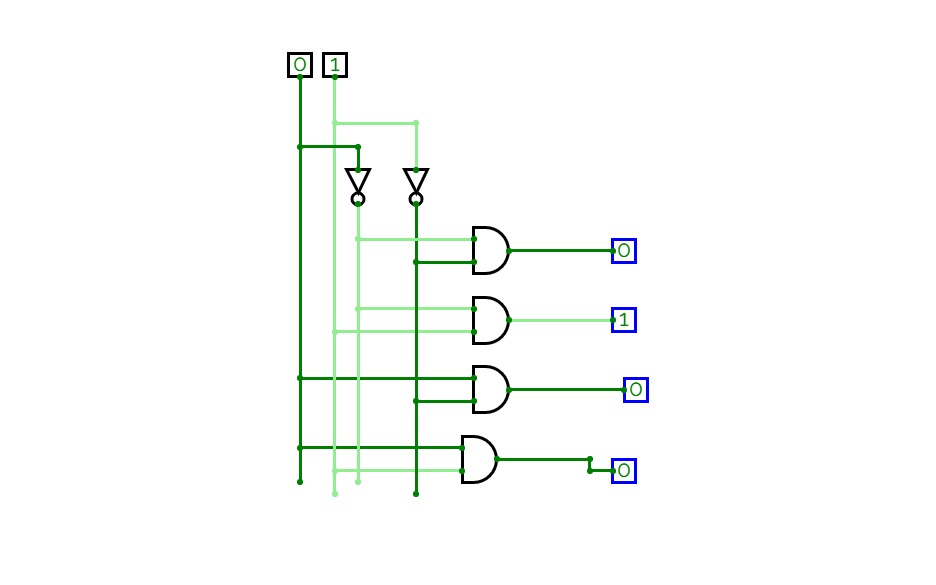

2:4 Decoder using NAND

2:4 Decoder using NAND

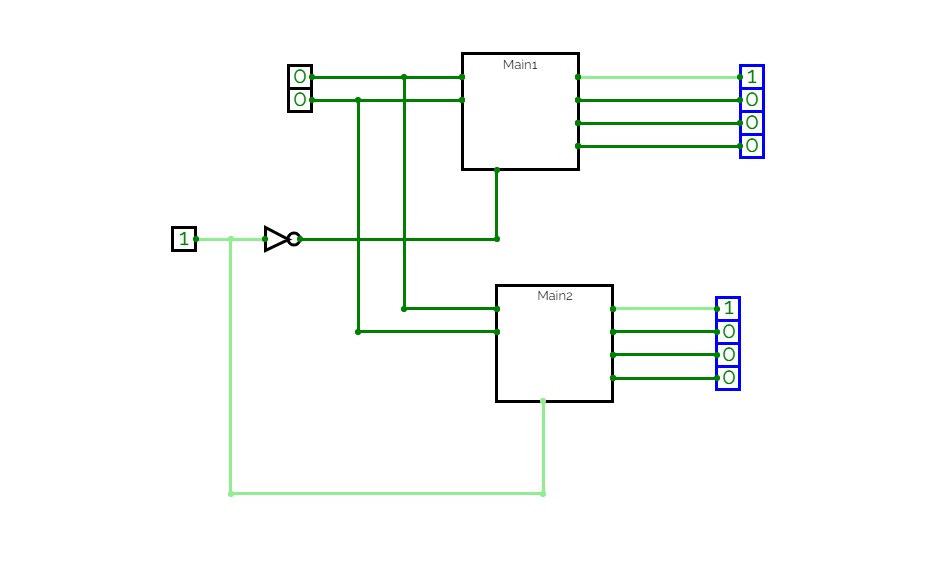

3*8 DECODER USING TWO 2*4 DECODERS

3*8 DECODER USING TWO 2*4 DECODERS

Full Adder using Decoder

Full Adder using Decoder

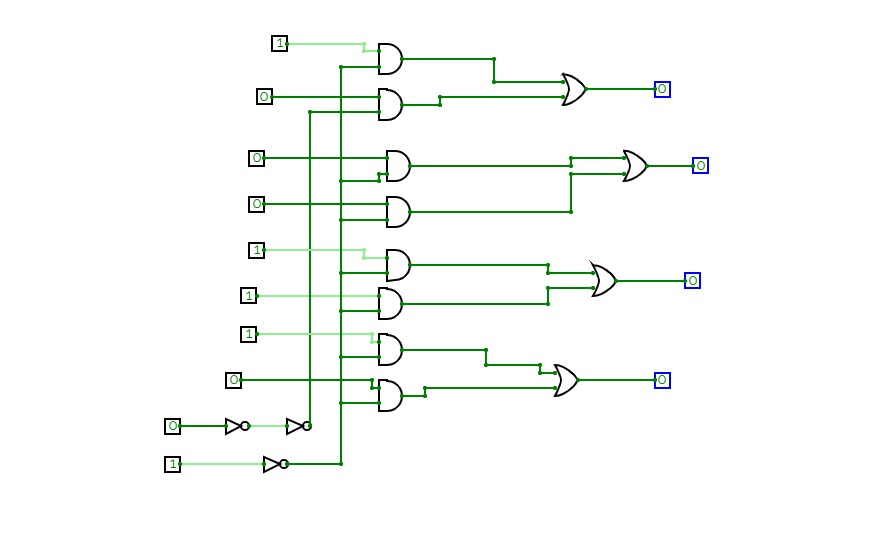

4-bit ALU

4-bit ALU

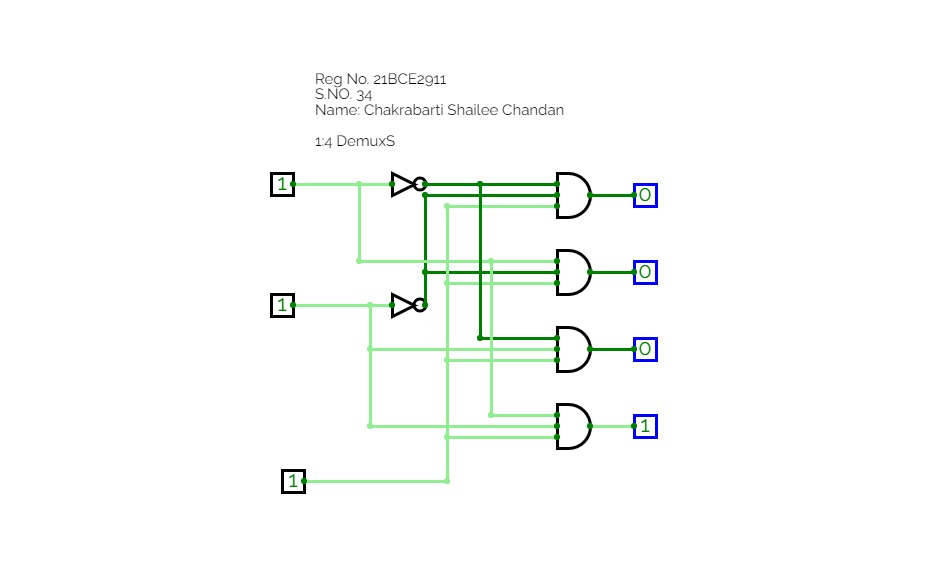

DeMux 1:4

DeMux 1:4

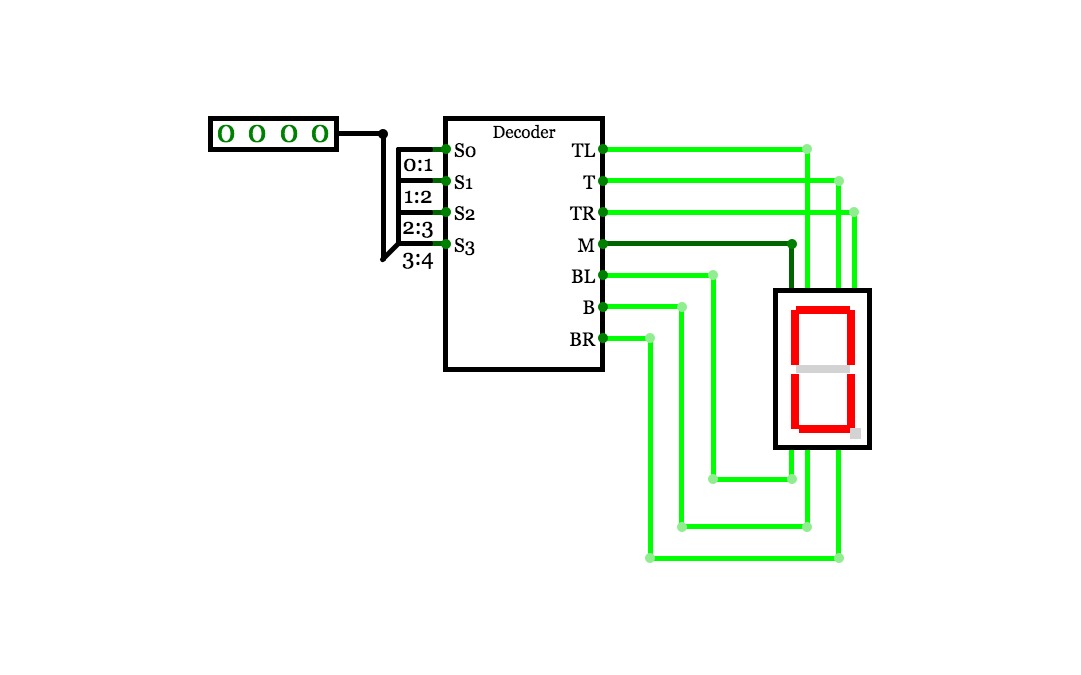

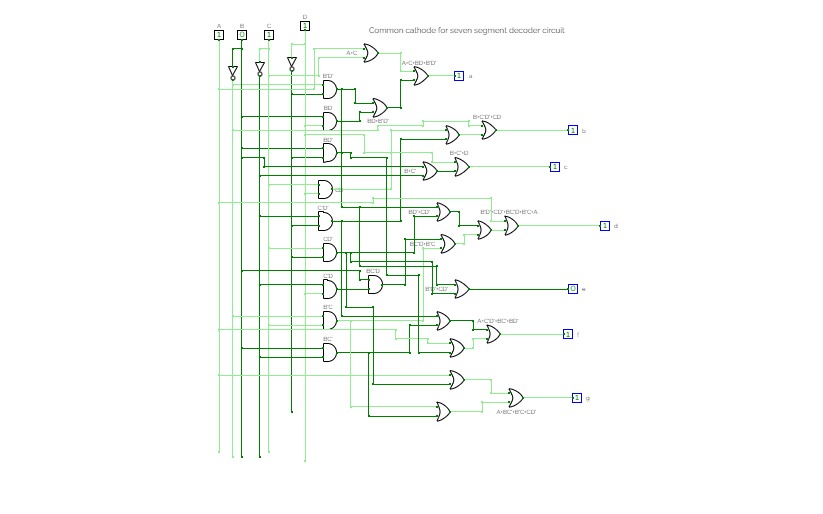

7 Segment Display

7 Segment Display

DA_3_NAND

DA_3_NAND

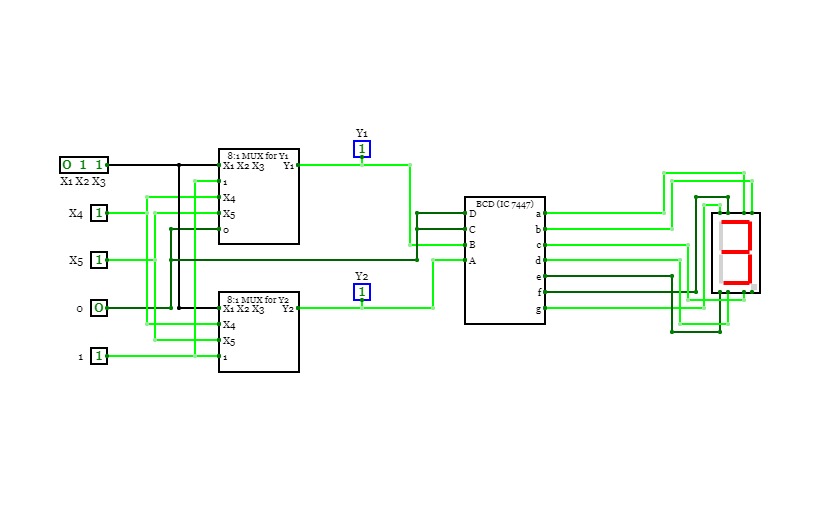

7_SEG_MUX_CATHODE

7_SEG_MUX_CATHODE

8X1_mux_7_segment

8X1_mux_7_segment

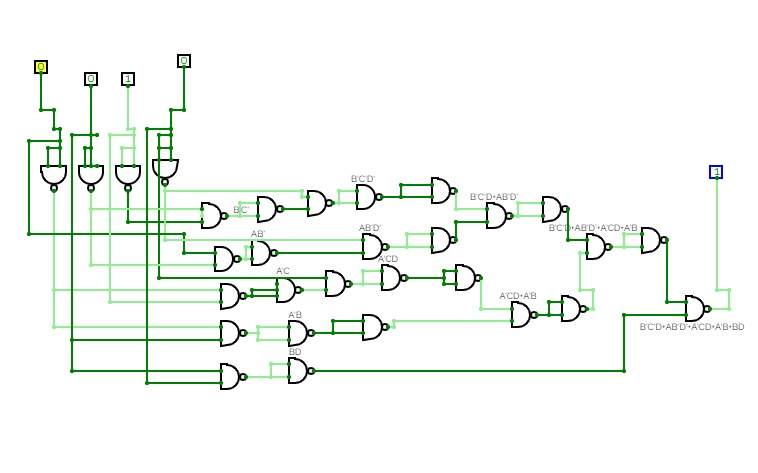

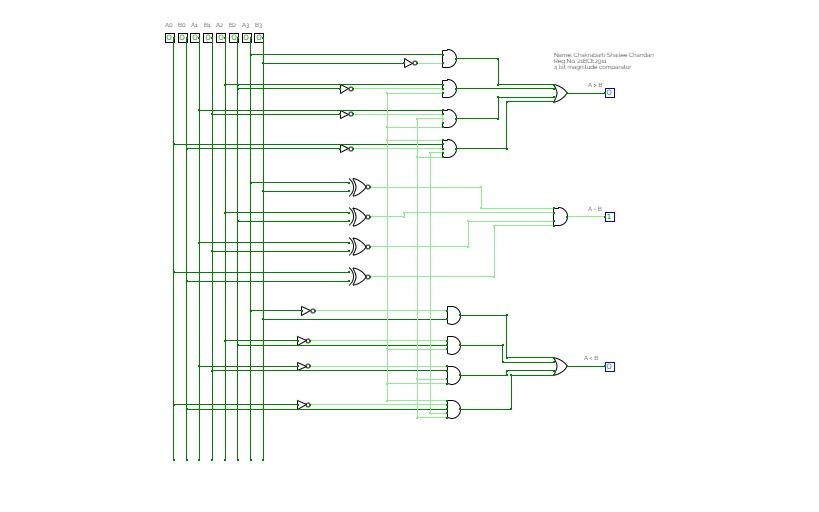

4-bit Magnitude comparator

4-bit Magnitude comparator

Mealy_machines

Mealy_machines

Moore_machine

Moore_machine

Synchron_ctr

Synchron_ctr

Aynchr_ctr

Aynchr_ctr

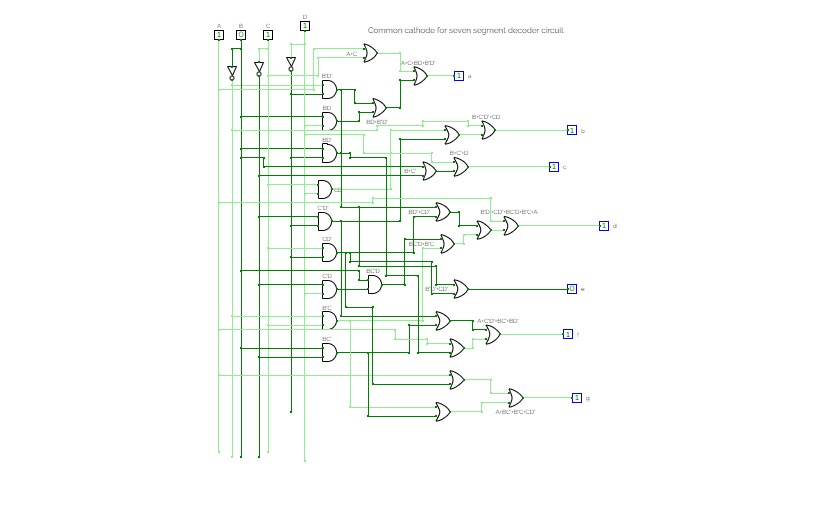

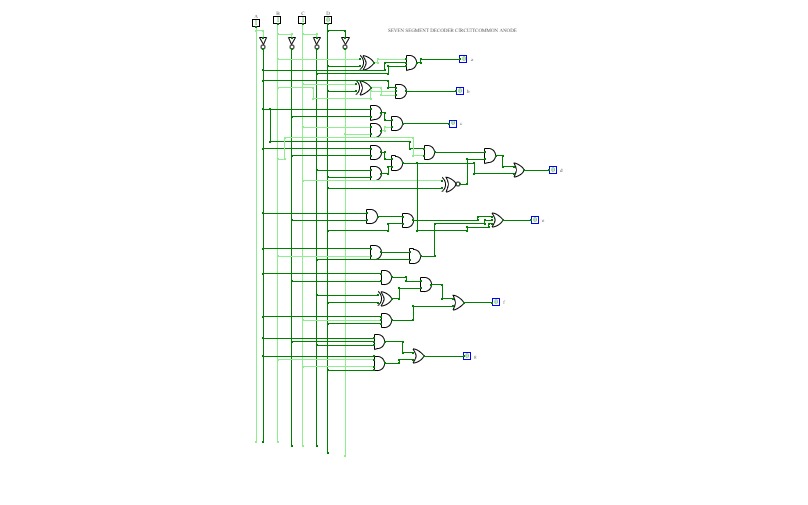

SEVEN SEGMENT DECODER CIRCUITCOMMON ANODE

SEVEN SEGMENT DECODER CIRCUITCOMMON ANODE

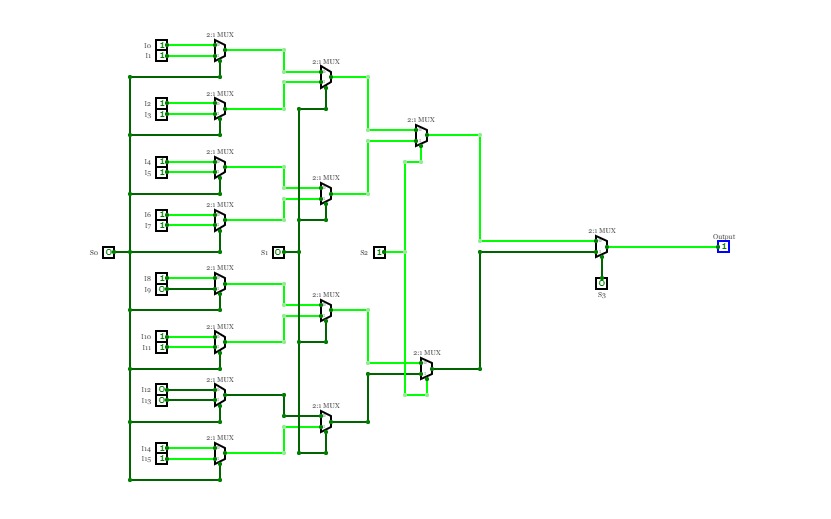

8:1 MUX using 2:1 MUX

8:1 MUX using 2:1 MUX

COMMON CATHODE 7 SEGMENT DECODER_16:1 MUX

COMMON CATHODE 7 SEGMENT DECODER_16:1 MUX

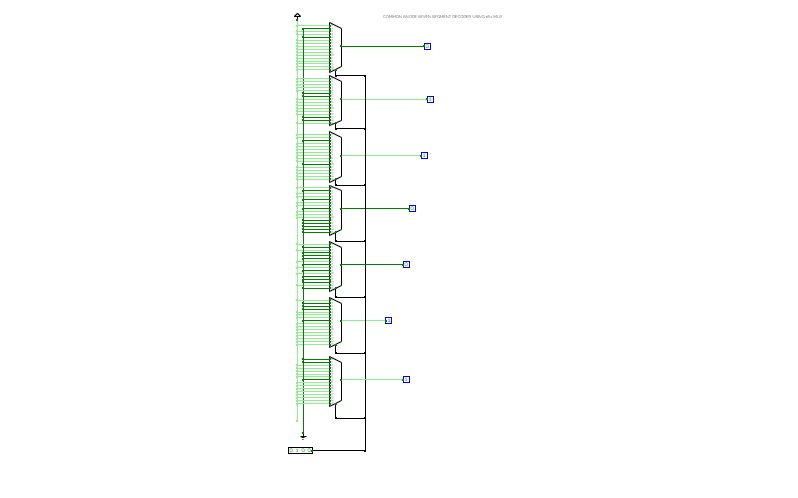

COMMON ANODE SEVEN SEGMENT DECODER USING 16:1 MUX

COMMON ANODE SEVEN SEGMENT DECODER USING 16:1 MUX

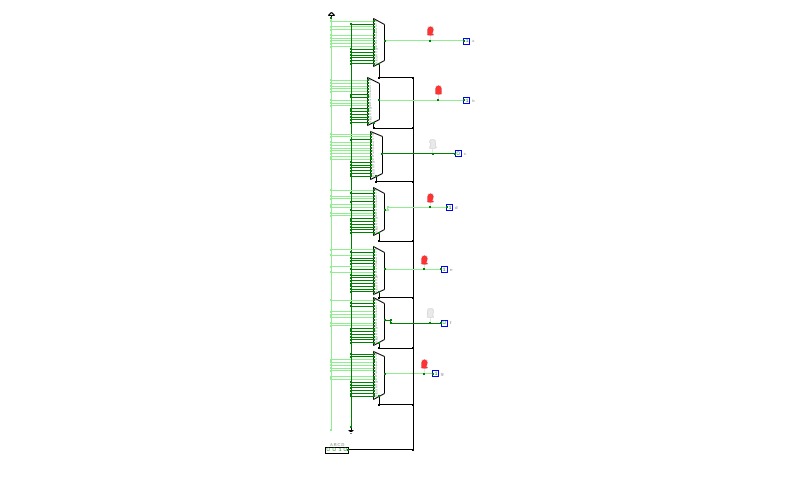

without_dc_cathode

without_dc_cathode

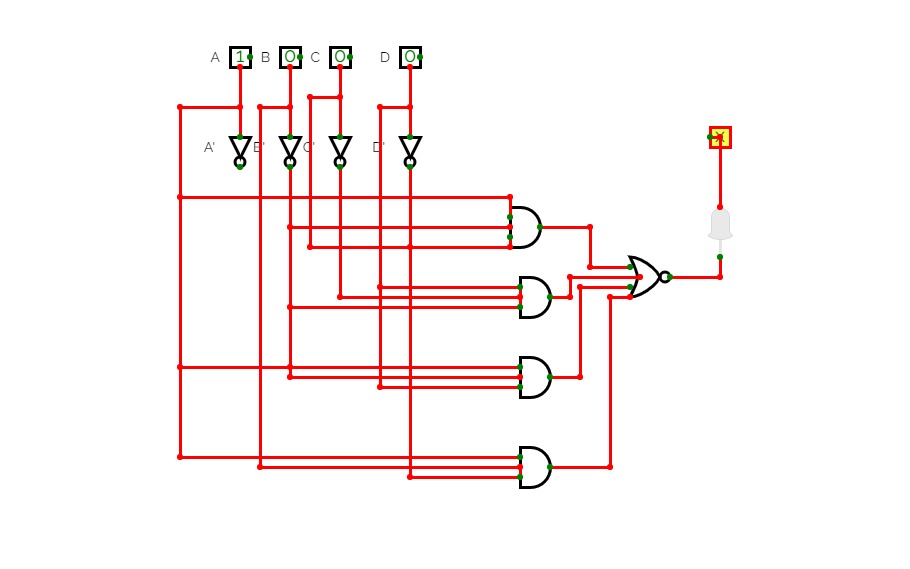

Q3_HOT_QUES_CIRCUITVERSE

Q3_HOT_QUES_CIRCUITVERSE

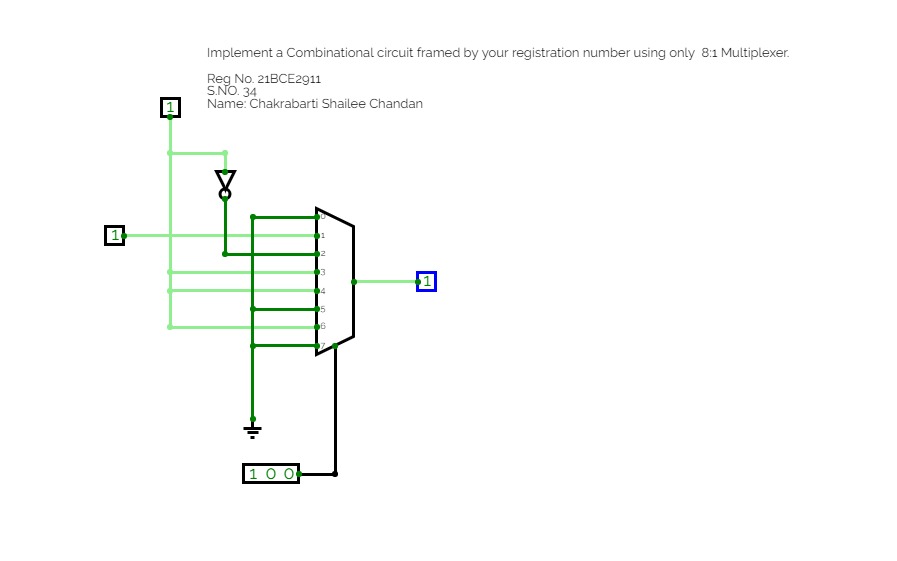

Implement a Combinational circuit framed by reg no 8:1 mux

Implement a Combinational circuit framed by reg no 8:1 mux

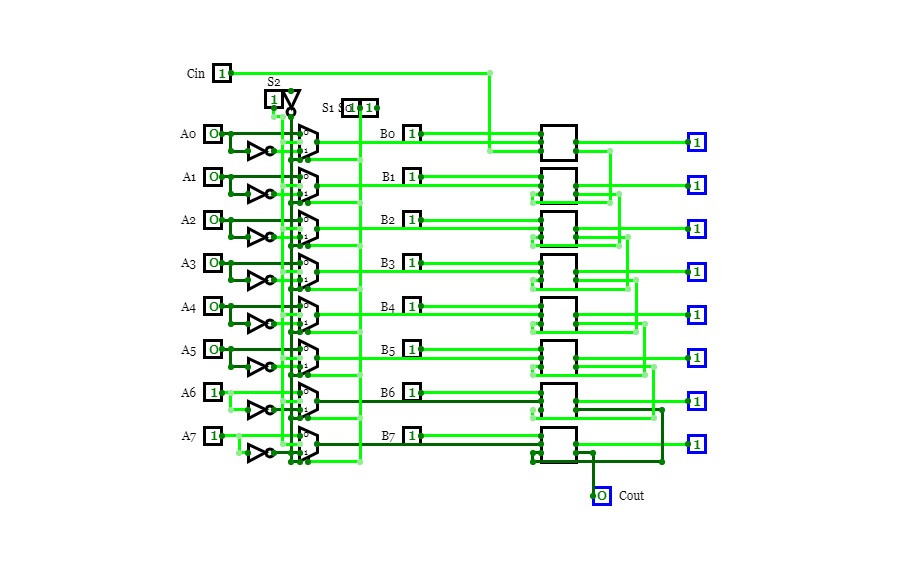

8 BIT ALU

8 BIT ALU

3:8_decoder

3:8_decoder

t1_34_21bce2911_pos_1

t1_34_21bce2911_pos_1

Untitled

Untitled

8 BIT ALU

8 BIT ALU

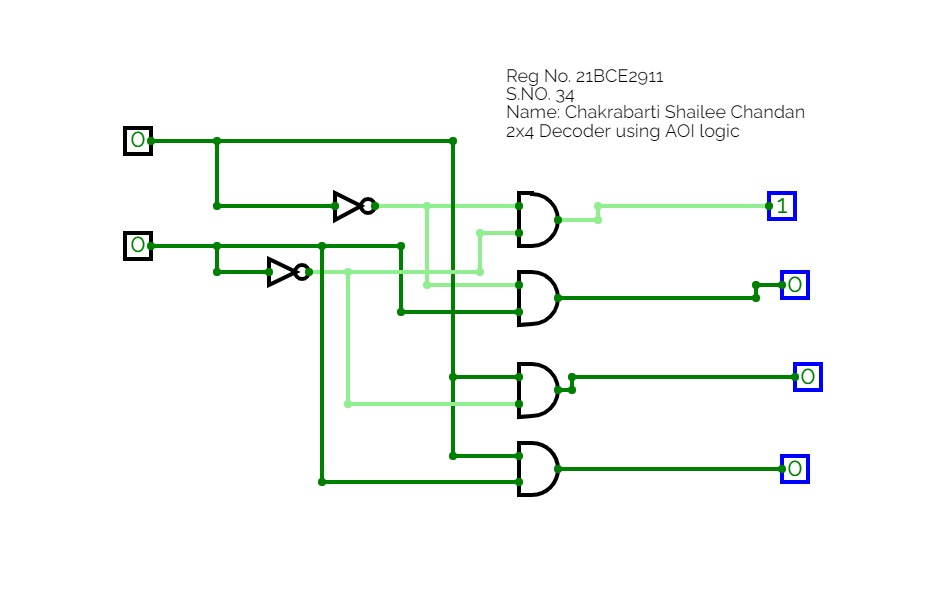

2x4_Decoder_using_AOI

2x4_Decoder_using_AOI

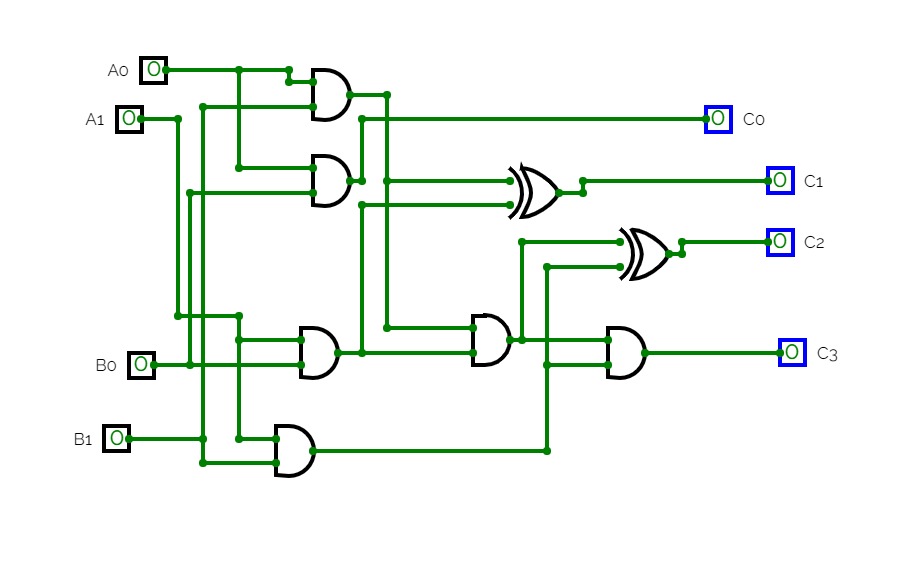

2x2_multiplier_21bce2911

2x2_multiplier_21bce2911

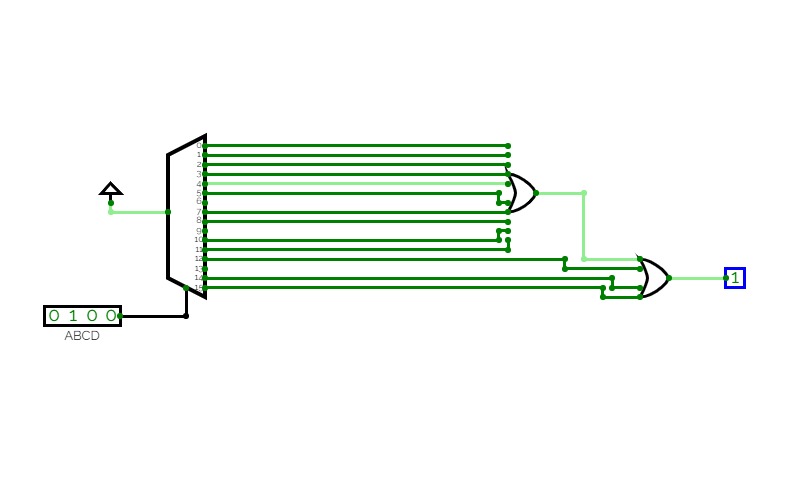

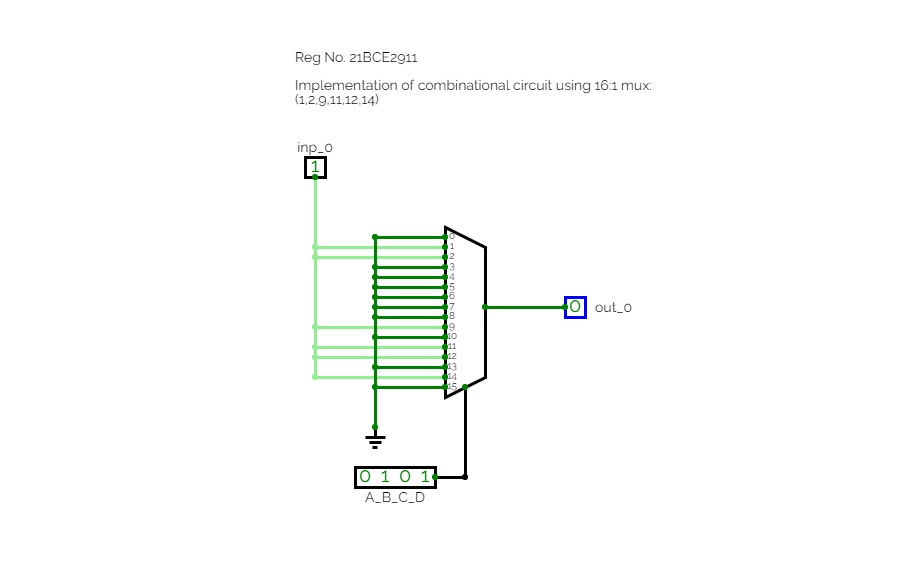

Implementation of combinational circuit using 16:1 mux:(1,2,9,11,12,14)

Implementation of combinational circuit using 16:1 mux:(1,2,9,11,12,14)

LAB 10

LAB 10