MOHAMMED FAIZAN

Member since: 2 years

Educational Institution: Not Entered

Country: Not Entered

Exp 9(2)

Exp 9(2)

Public

Half Adder using XOR and NAND

Half Adder using XOR and NAND

Public

Full Adder

Full Adder

Public

Exp 7(2)

Exp 7(2)

Public

7(3)

7(3)

Public

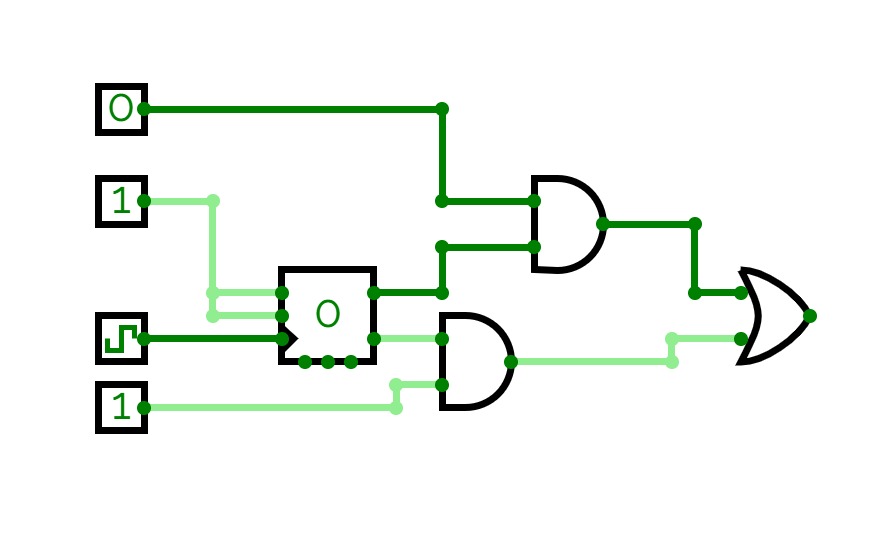

4:1 Mux using Logic Gates

4:1 Mux using Logic Gates

Public

Exp 3(2)

Exp 3(2)

Public

EXP 3(3)

EXP 3(3)

Public

EXP 3(4)

EXP 3(4)

Public

Exp 3(5)

Exp 3(5)

Public

Exp 3(6)

Exp 3(6)

Public

cIRCUIT 2

cIRCUIT 2

Public

Untitled

Untitled

Public

CIRCUIT 3

CIRCUIT 3

Public

exp 8(2)

exp 8(2)

Public

EXP 3 (1)

EXP 3 (1)

Public

Experiment 1

Experiment 1

Public

Untitled

Untitled

Public

EXP 4(3)

EXP 4(3)

Public

exp 4(4)

exp 4(4)

Public

exp 4(4)

exp 4(4)

Public

4) DESIGN AND IMPLEMENTATION OF COMBINATIONAL CIRCUITS USING BASIC GATES

4) DESIGN AND IMPLEMENTATION OF COMBINATIONAL CIRCUITS USING BASIC GATES

Public

Exp 5(2)

Exp 5(2)

Public

D To JK Flip Flop Conversion

D To JK Flip Flop Conversion

Public

Exp 4(2)

Exp 4(2)

Public

Exp 8(1)

Exp 8(1)

Public

exp 9(1)

exp 9(1)

Public

INTERNAL CIRCUIT OF 1:2 DEMUX USING TWO INPUT NAND GATE

INTERNAL CIRCUIT OF 1:2 DEMUX USING TWO INPUT NAND GATE

Public