Shiv Vishwakarma

Member since: 2 years

Educational Institution: Not Entered

Country: Not Entered

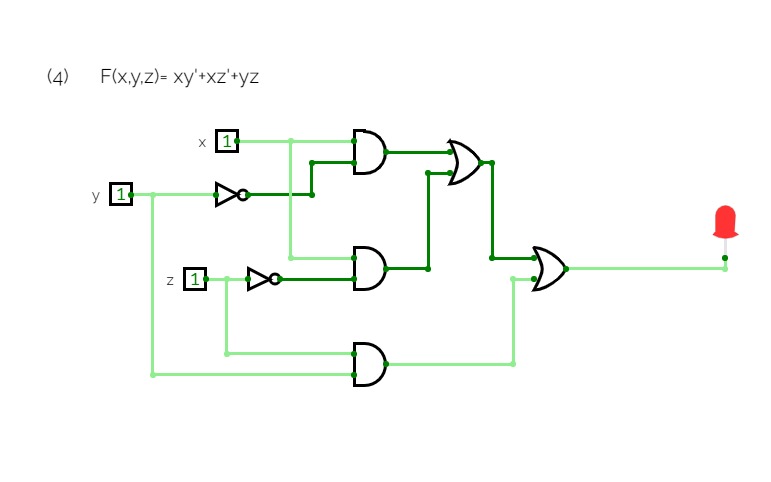

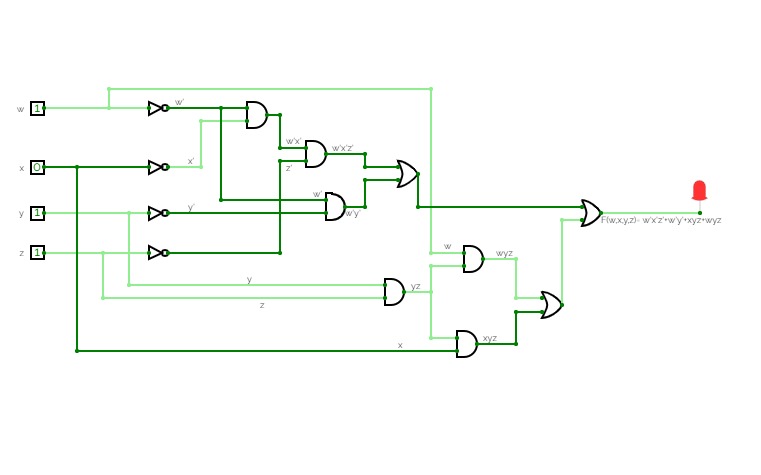

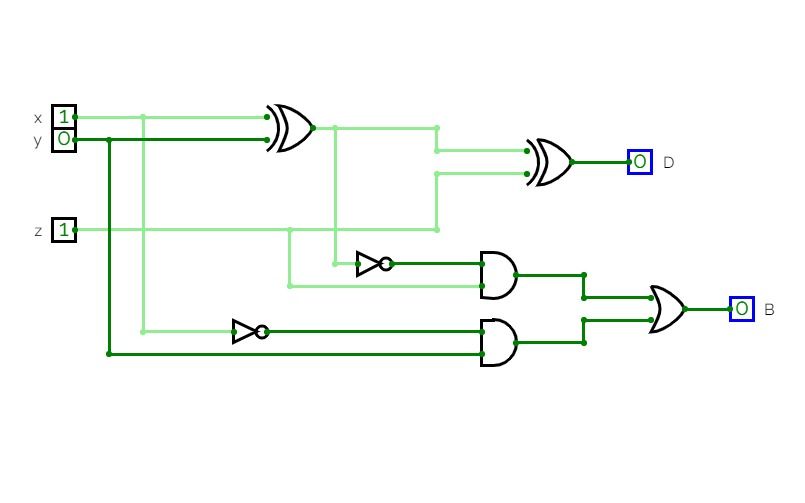

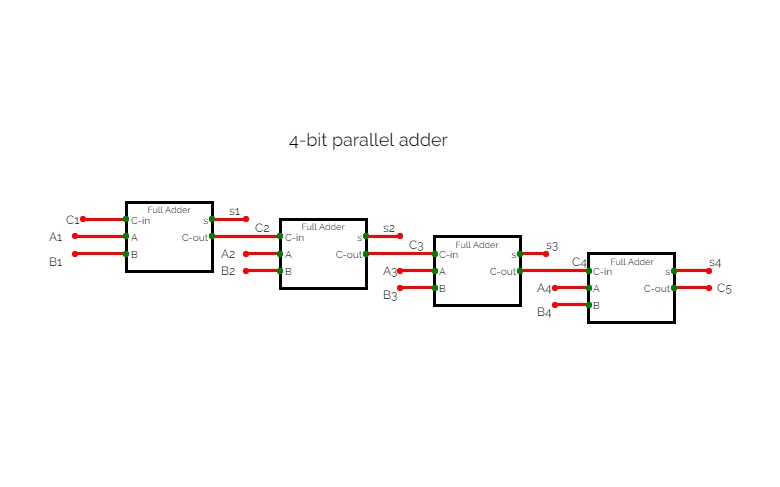

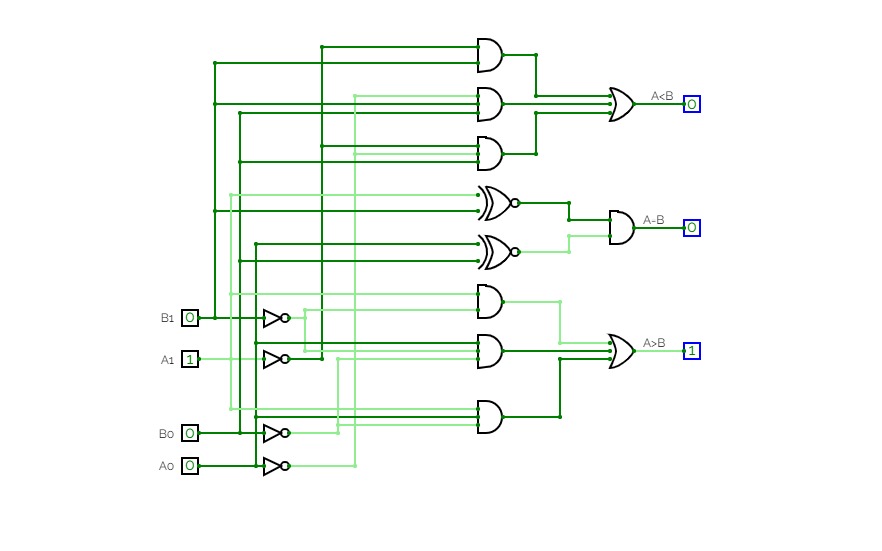

A3.1

A3.1

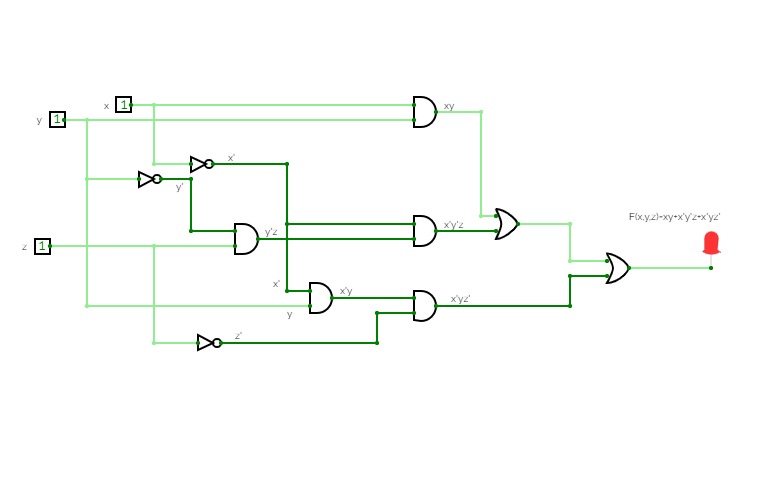

A3.2

A3.2

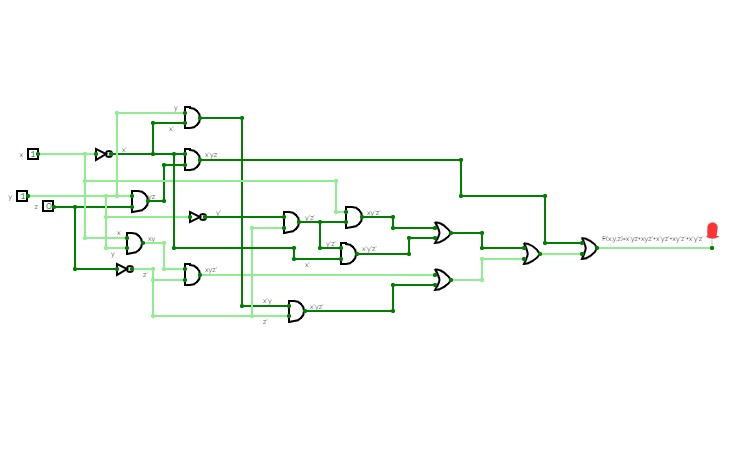

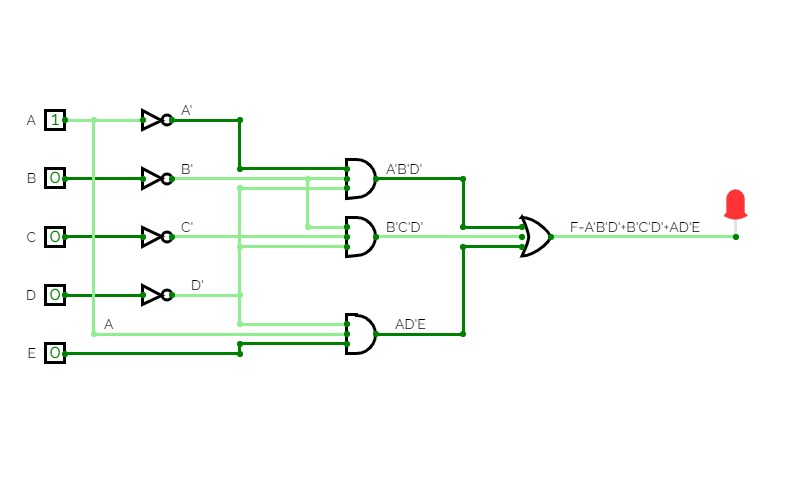

A3.3

A3.3

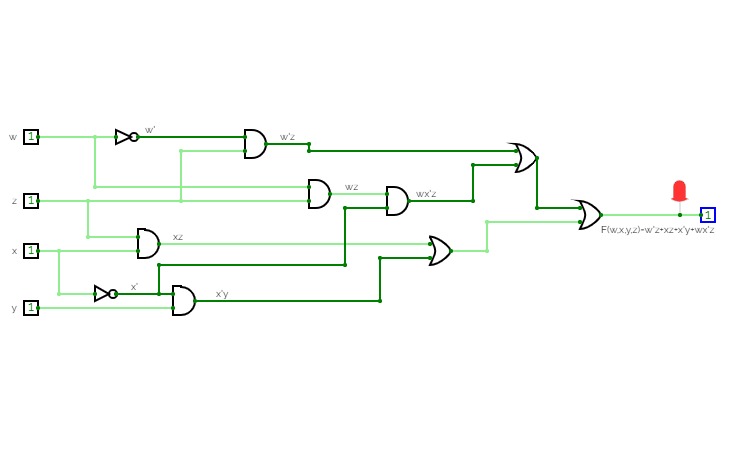

A3.4

A3.4

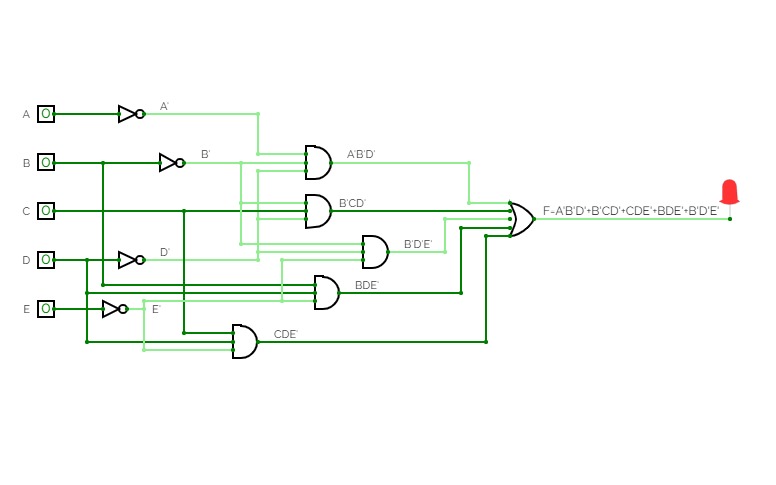

A4.1

A4.1

A4.2

A4.2

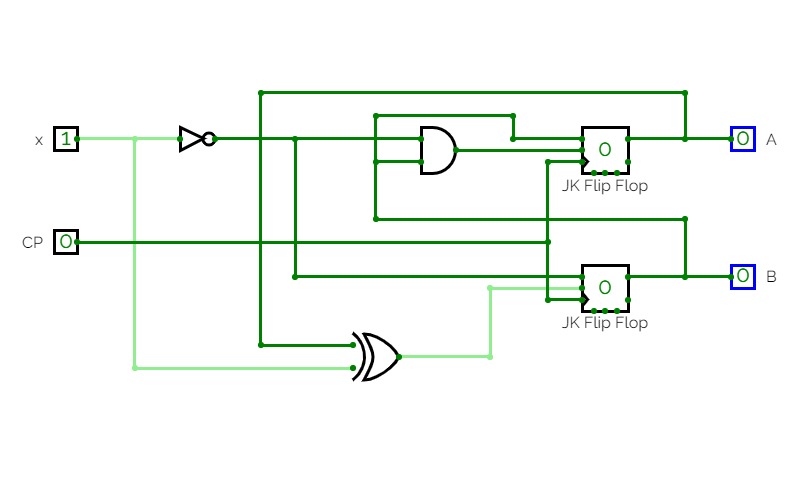

sequential circuit with JK flip flop

sequential circuit with JK flip flop

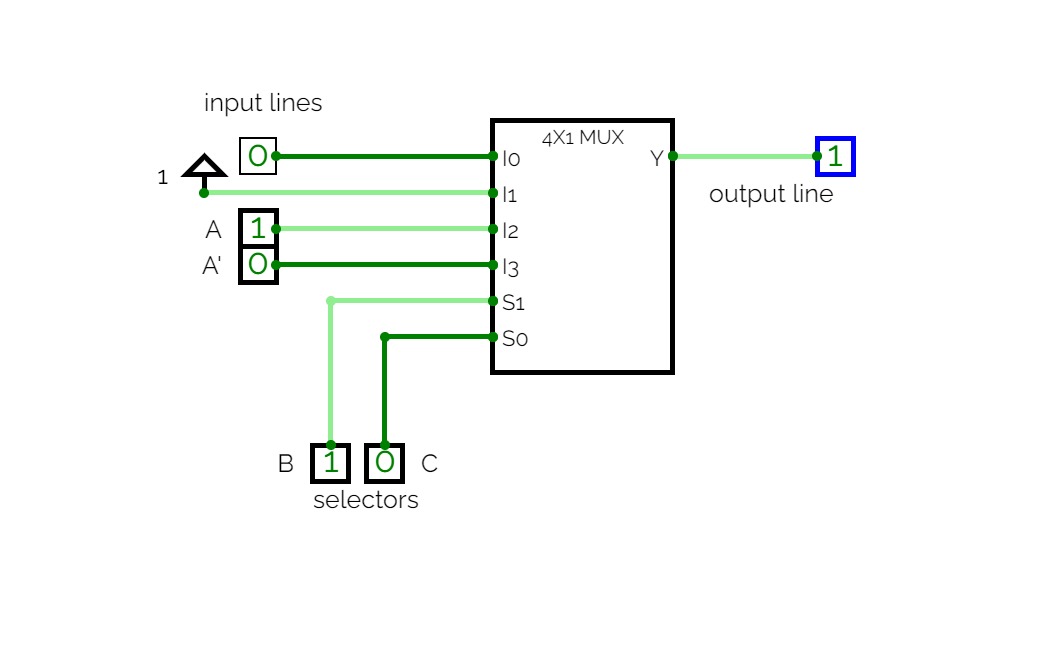

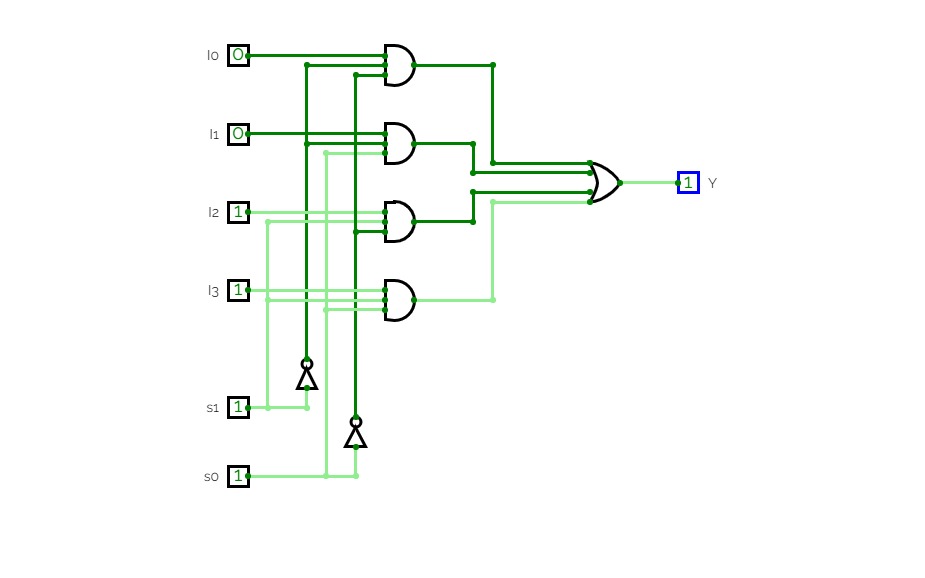

mux

mux

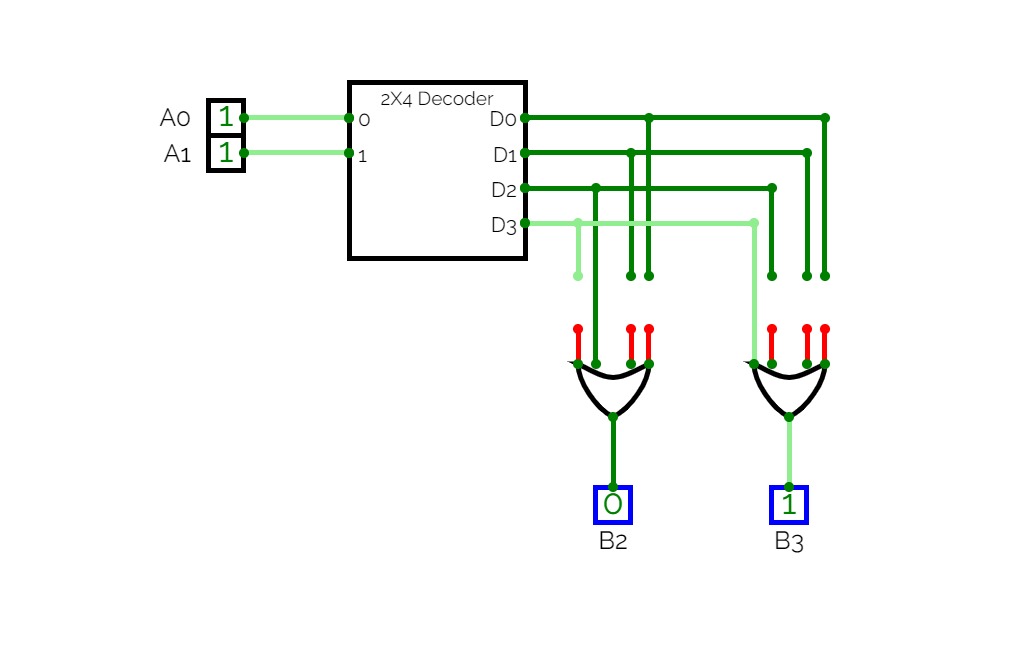

2X4 Decoder&16bit ROM& combinational circuit

2X4 Decoder&16bit ROM& combinational circuit

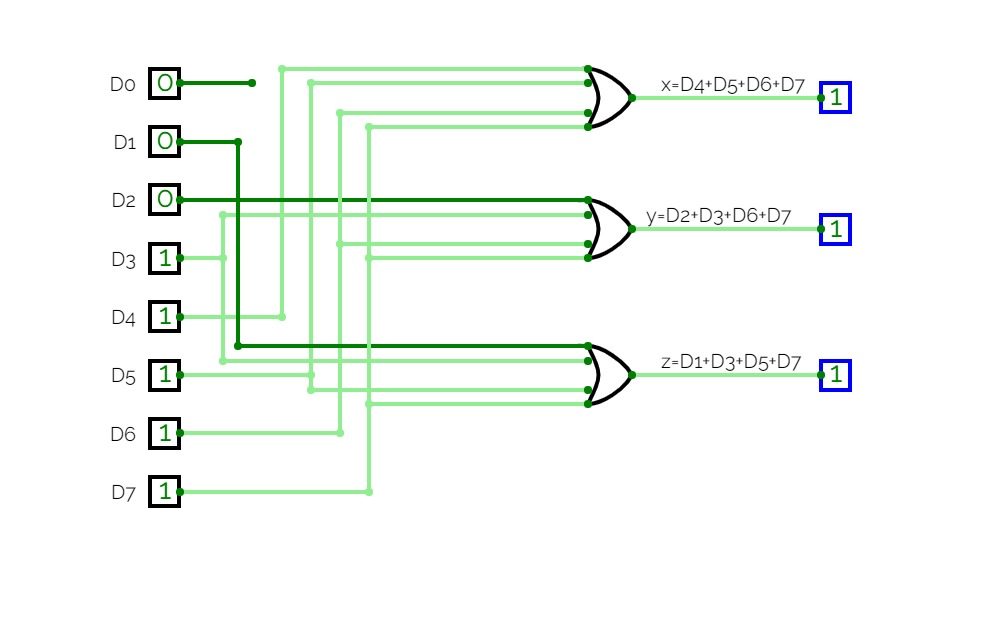

A5.1

A5.1

A5.4

A5.4

A5.3

A5.3

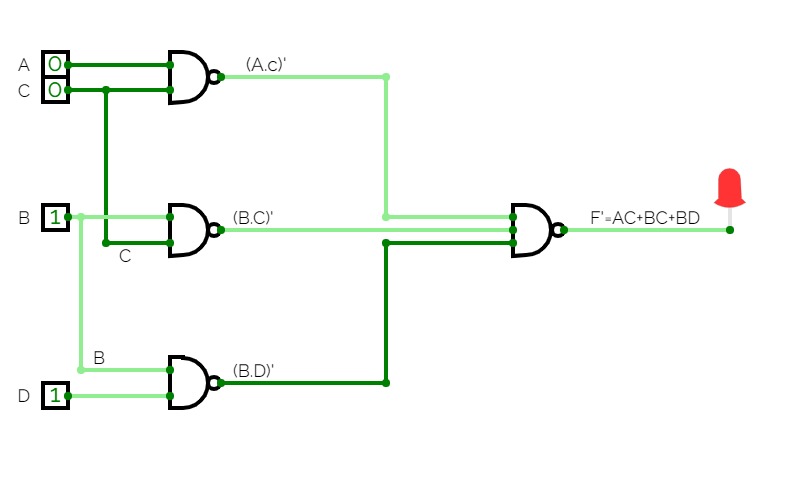

ABCD

ABCD

SSVcircuitverse

SSVcircuitverse

A5.2

A5.2

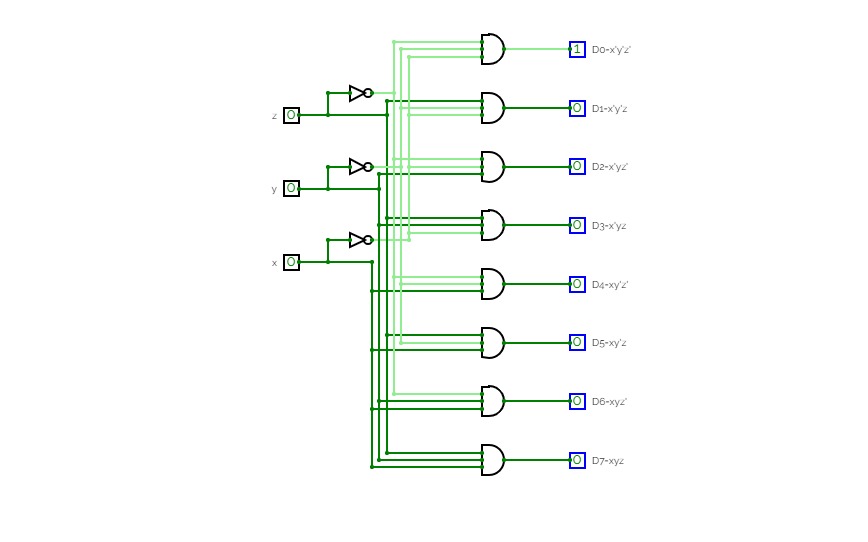

A6.1

A6.1

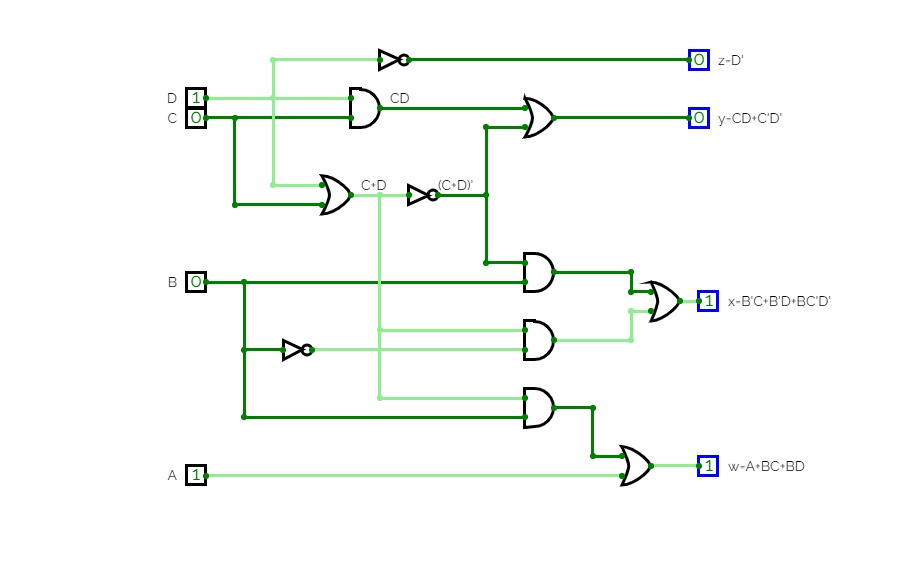

A6.2

A6.2

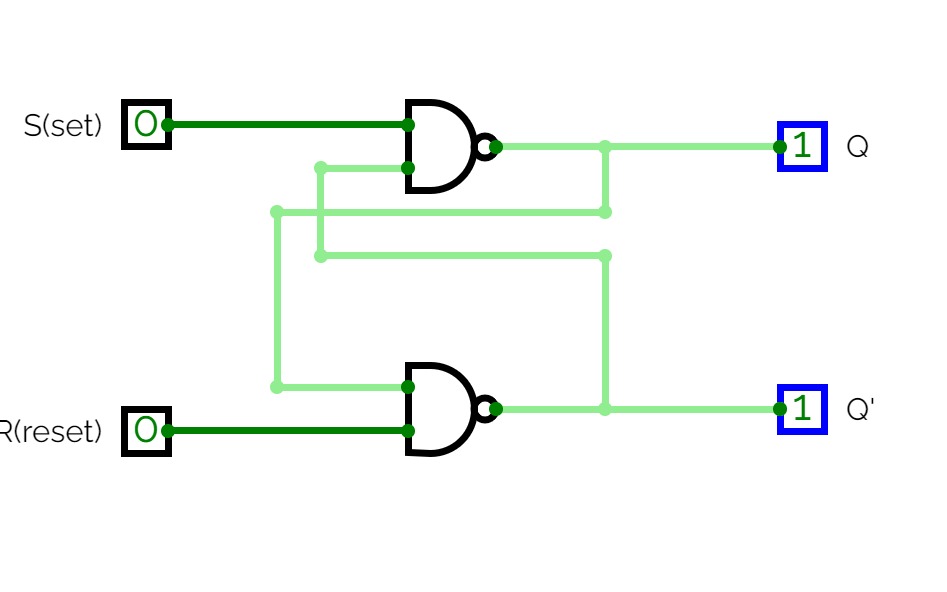

S R latch

S R latch

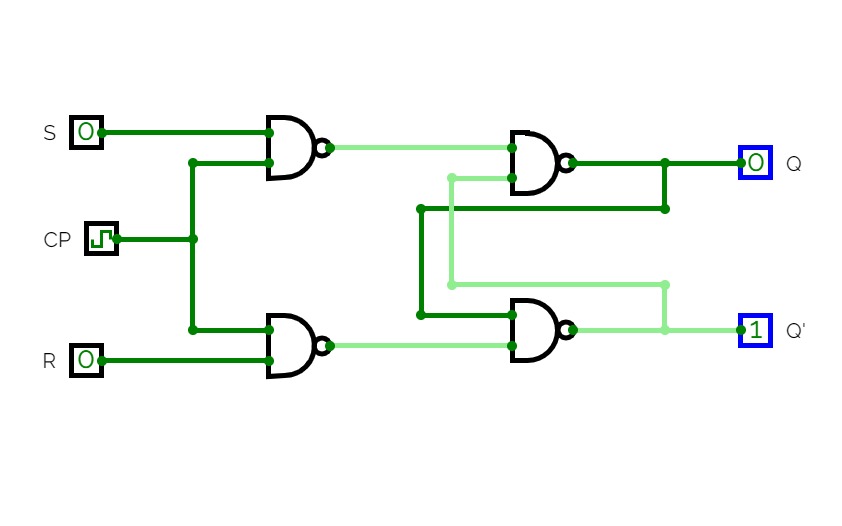

s R latch with CP using NAND gate

s R latch with CP using NAND gate

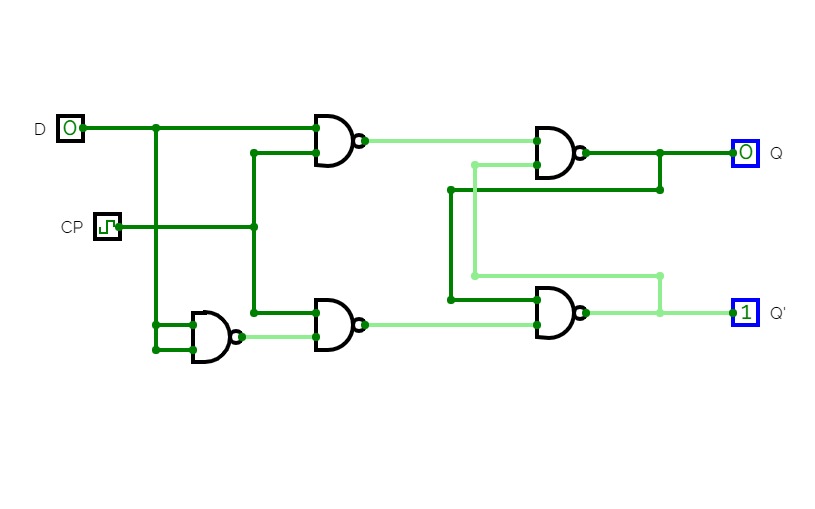

D flip flop

D flip flop

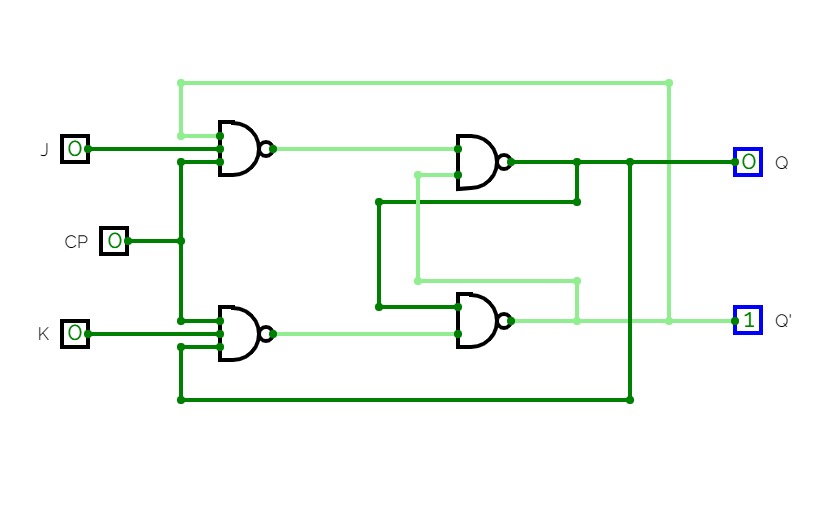

J K flip flop

J K flip flop

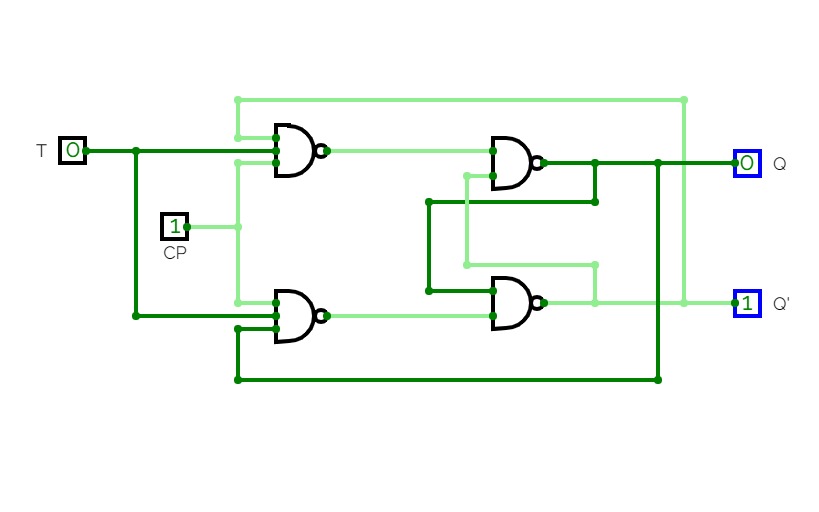

T flip flop

T flip flop

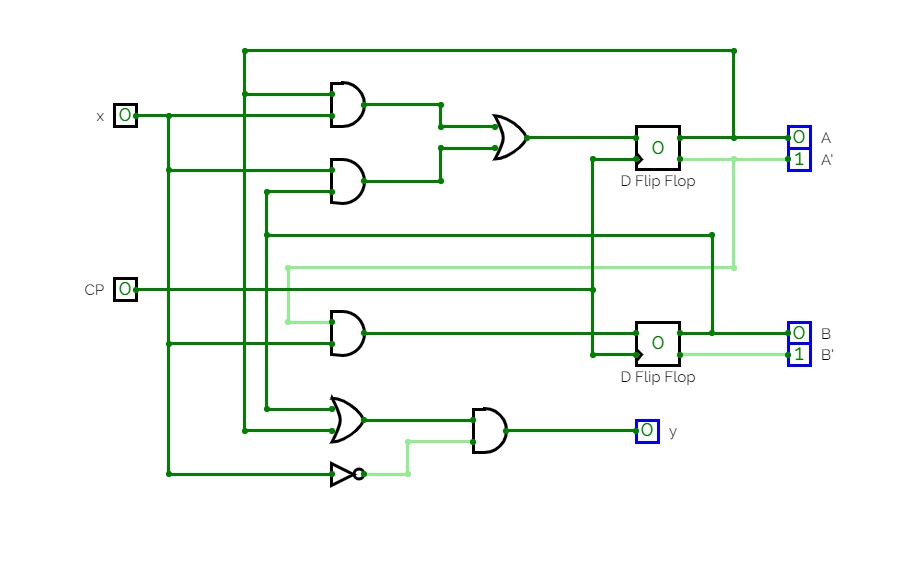

sequential circuit using D flip flop

sequential circuit using D flip flop

simple CPU

simple CPU

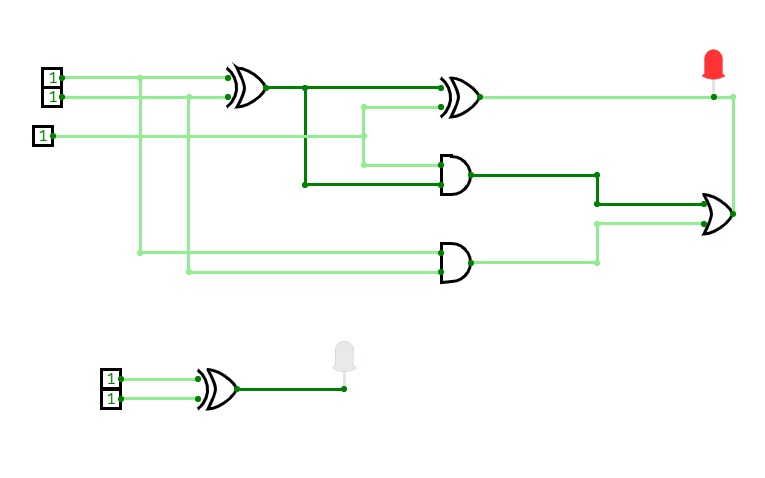

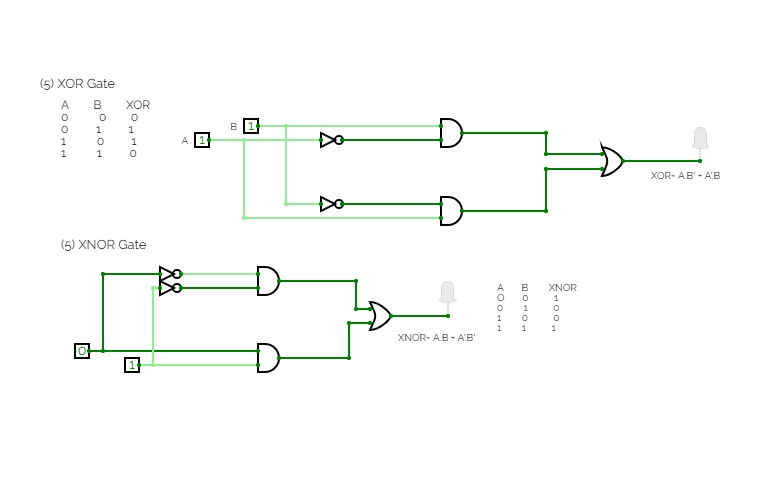

Exclusive OR

Exclusive OR

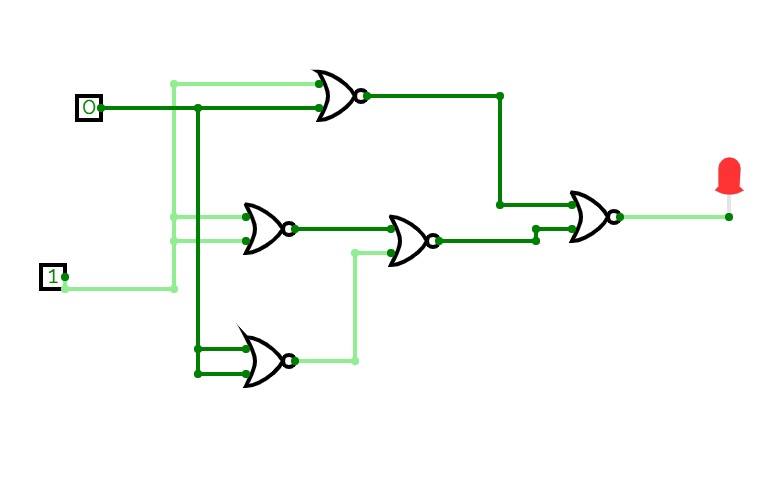

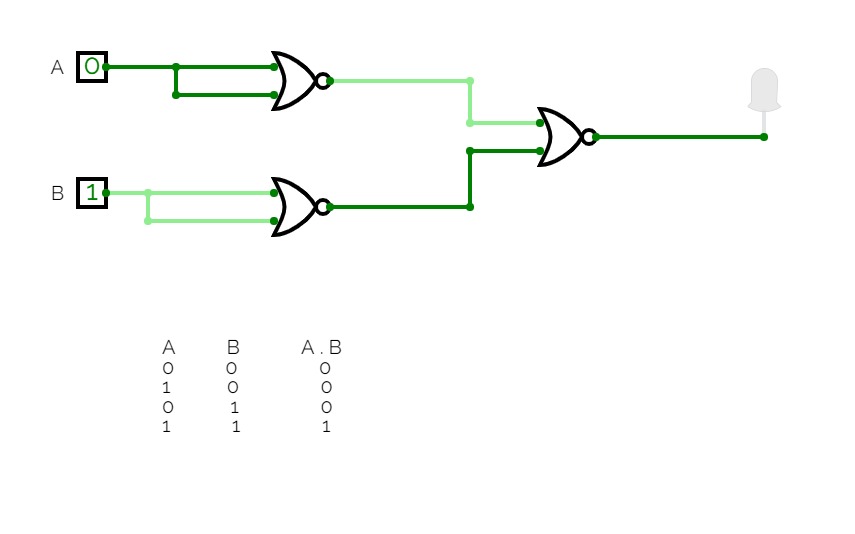

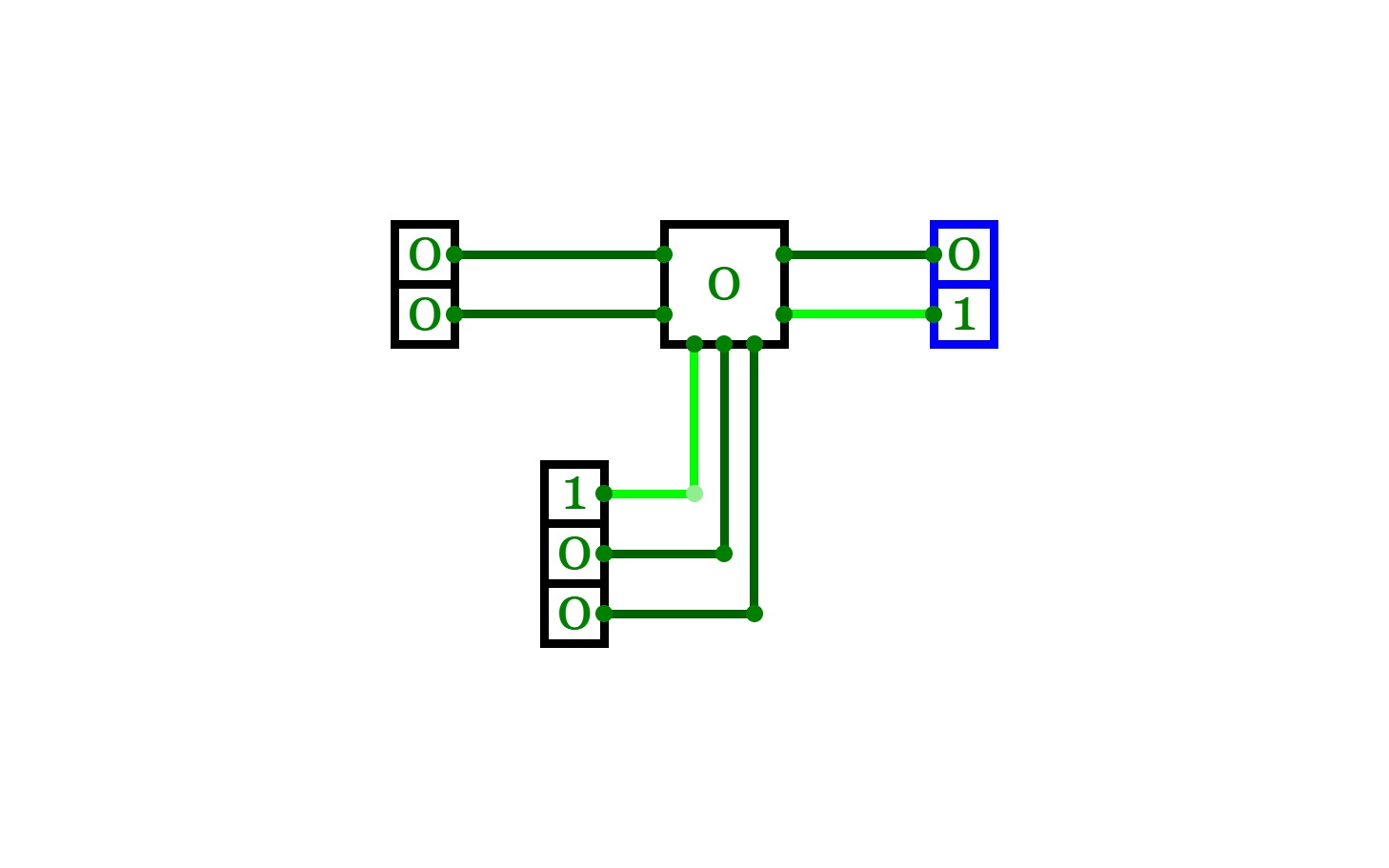

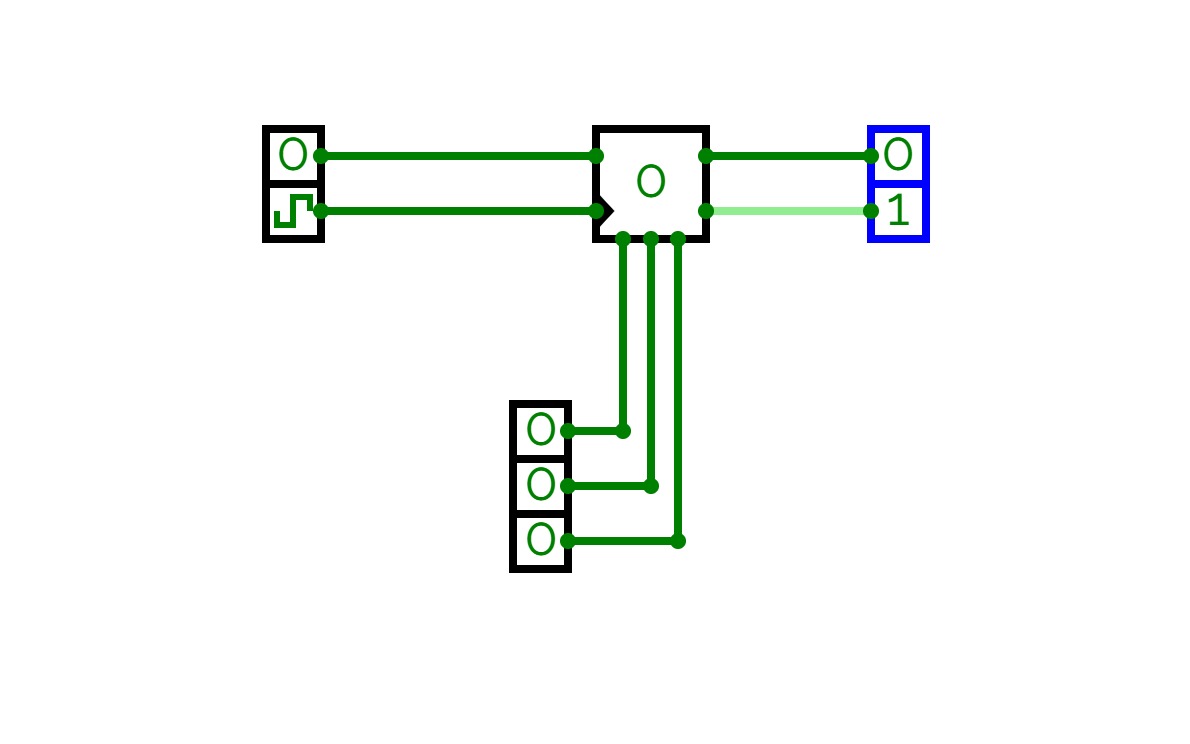

AND GATE

AND GATE

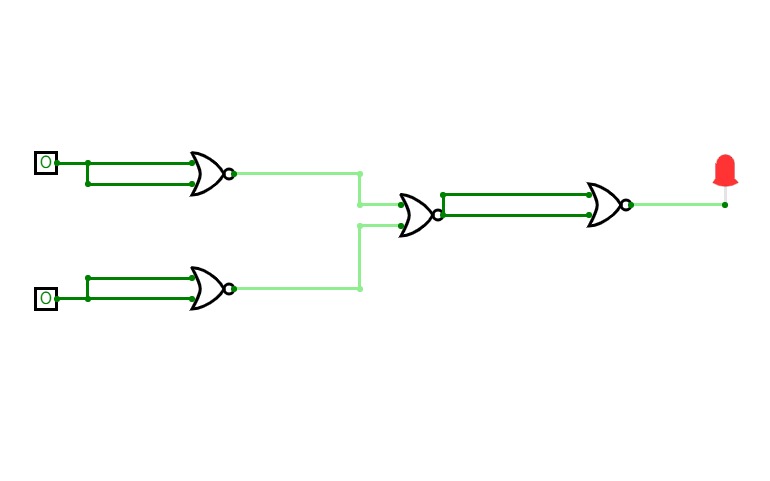

NAND GATE

NAND GATE

Pratham Maheshwari/Verify the excitation tables of various FLIP-FLOPS.

Pratham Maheshwari/Verify the excitation tables of various FLIP-FLOPS.

Verify the excitation tables of various FLIP-FLOPS.

Verify the excitation tables of various FLIP-FLOPS.

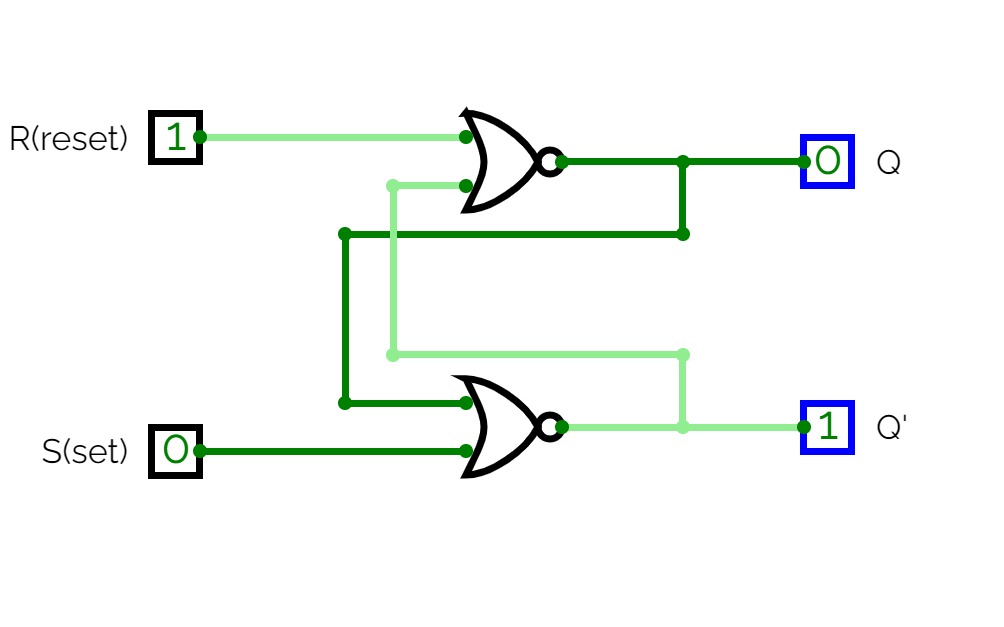

s r latch using nor gate

s r latch using nor gate

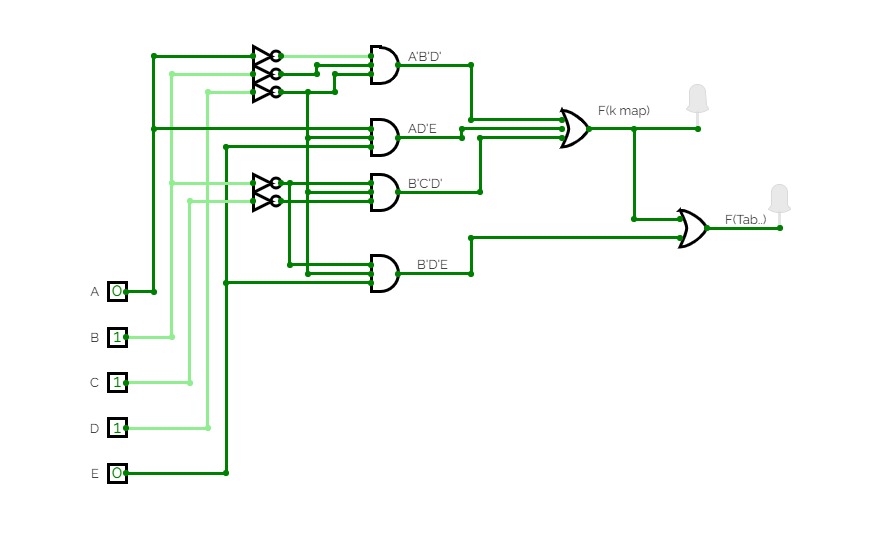

kMAPvsTabulation

kMAPvsTabulation

Untitled

Untitled

A7.1

A7.1

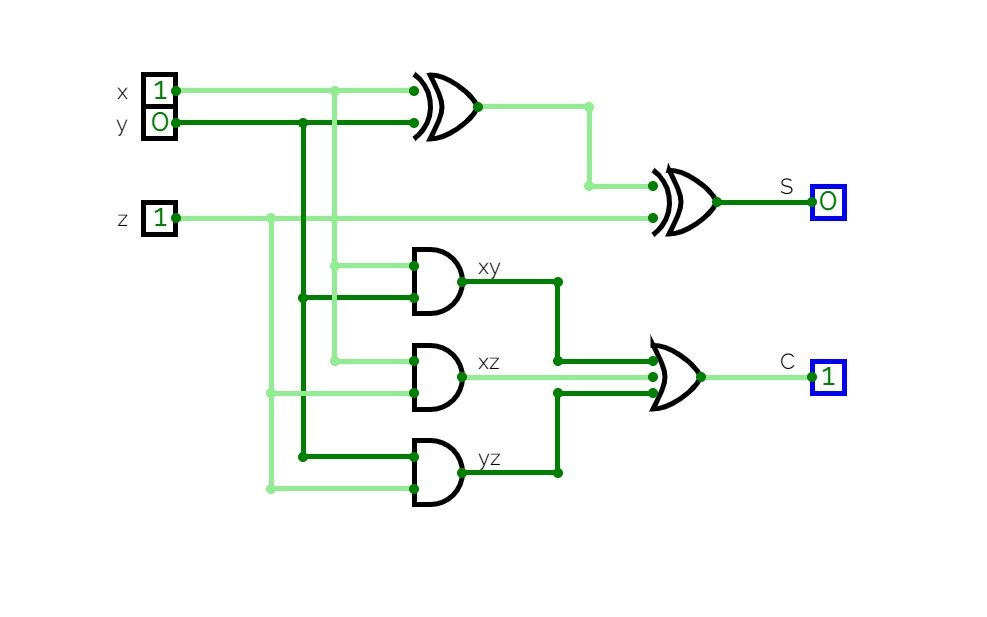

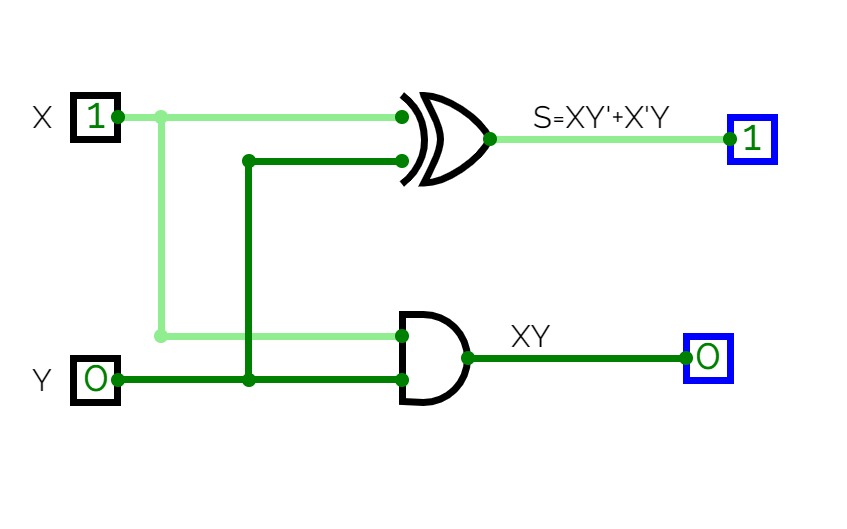

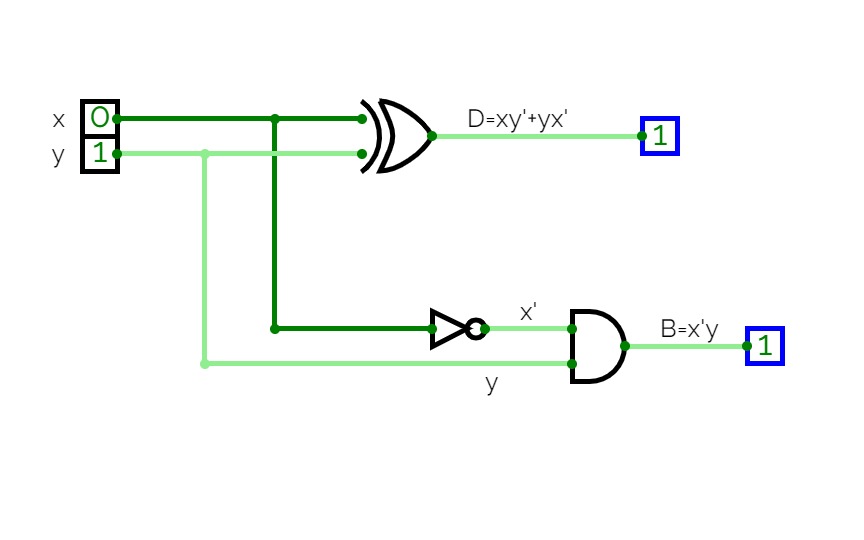

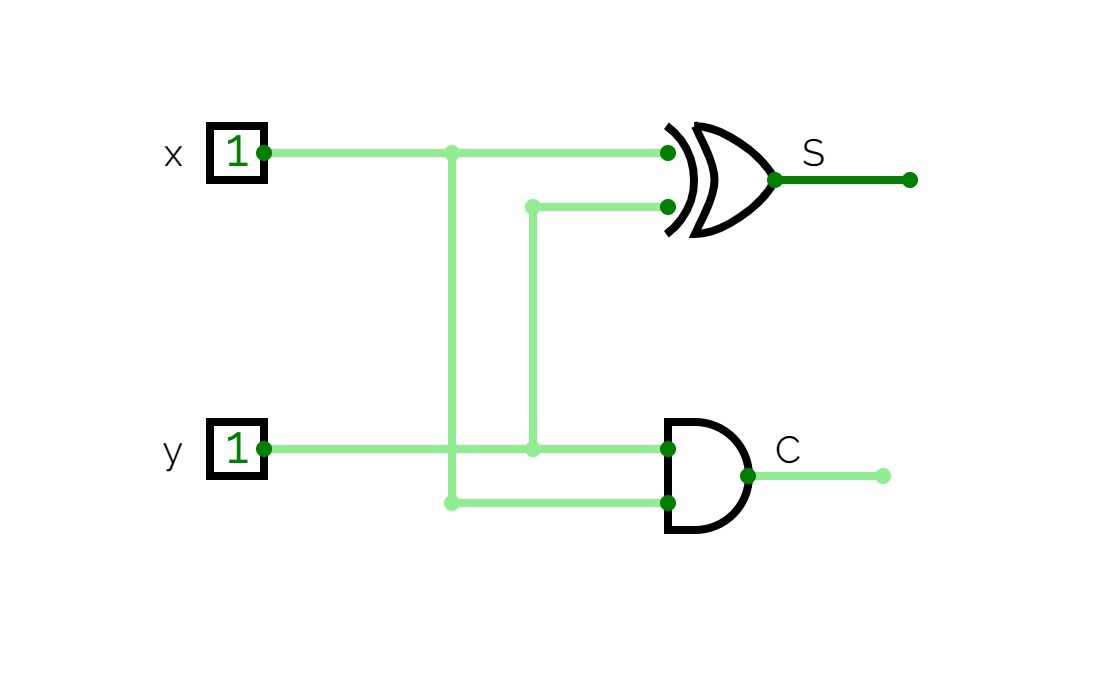

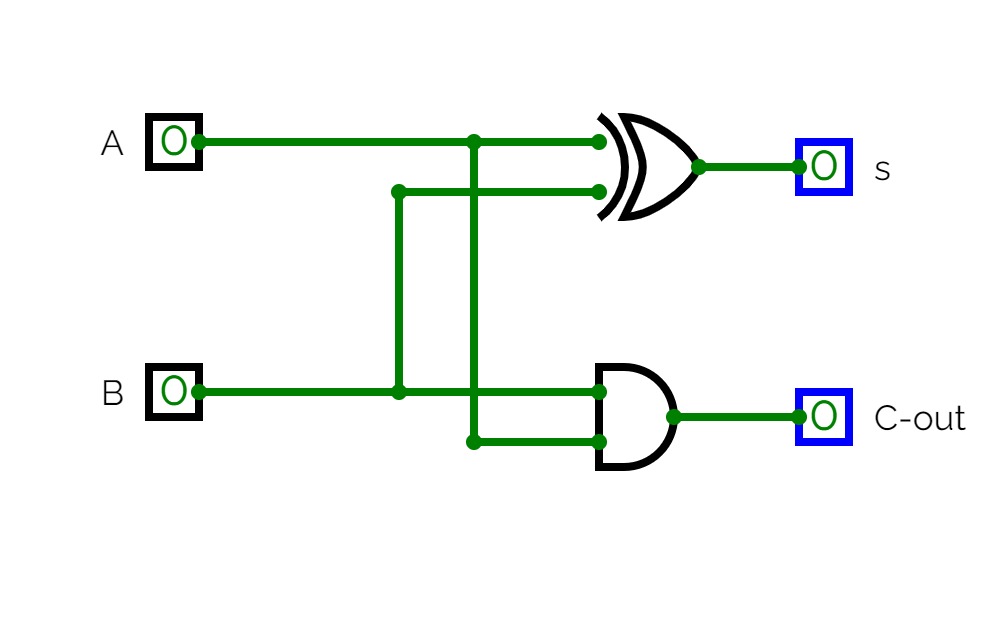

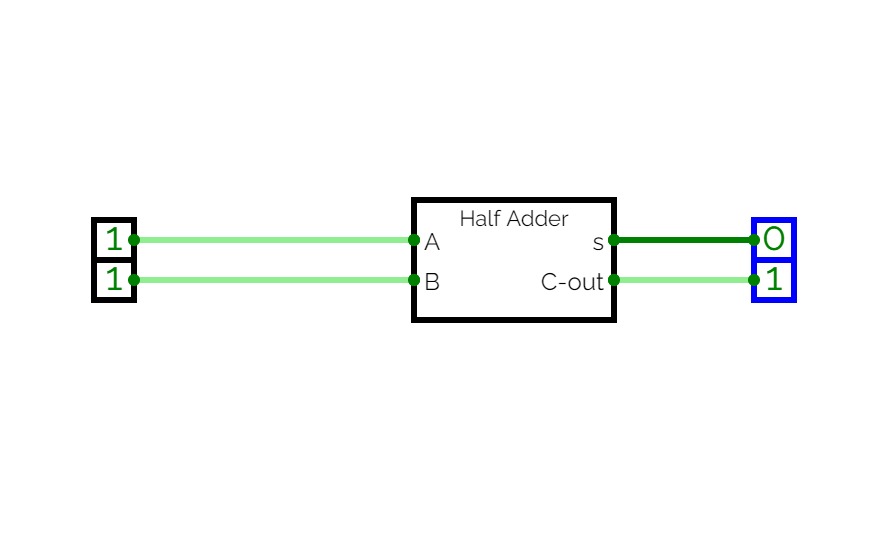

Half Adder

Half Adder

Untitled

Untitled

A7.6

A7.6

A7.4

A7.4

A7.3

A7.3

A7.5

A7.5

A7.2

A7.2

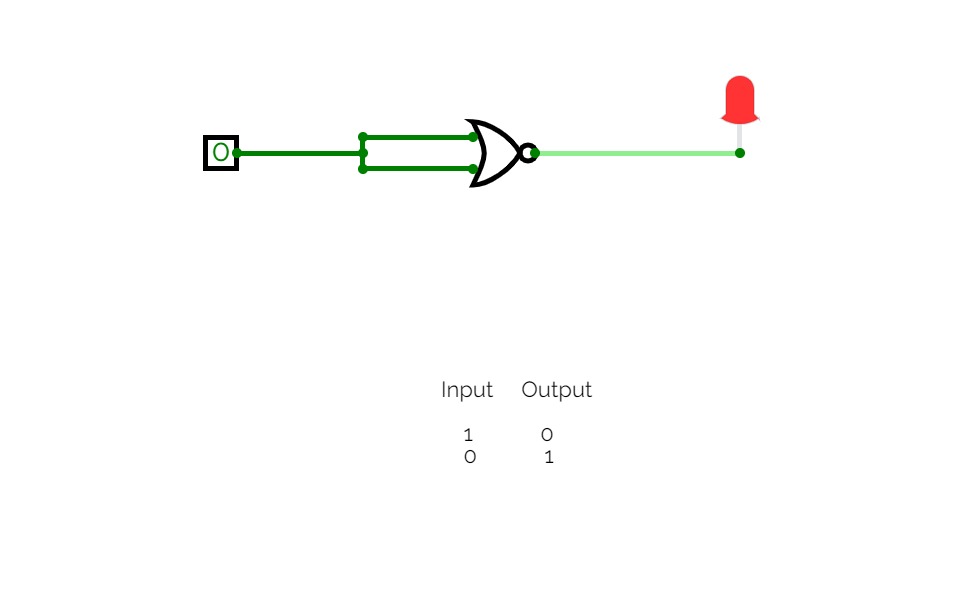

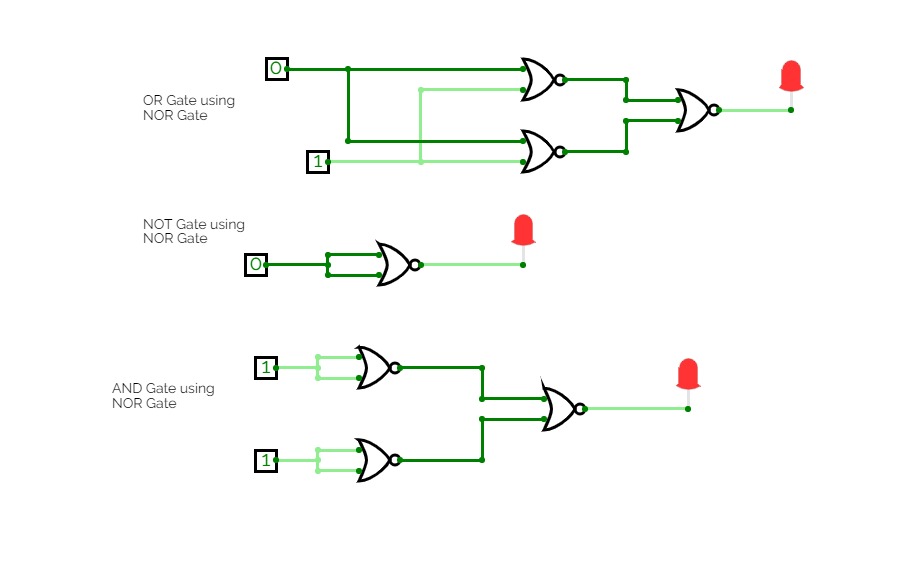

NOT gate using NOR gate

NOT gate using NOR gate

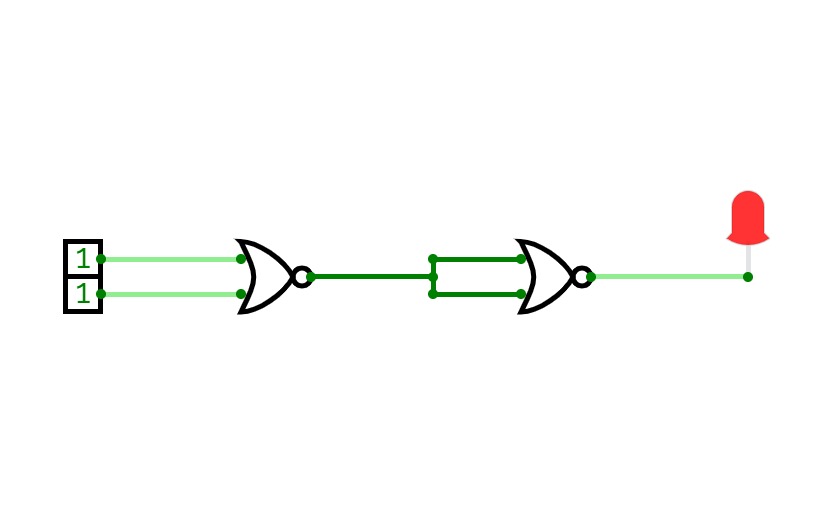

OR gate using NOR gate

OR gate using NOR gate

Untitled

Untitled

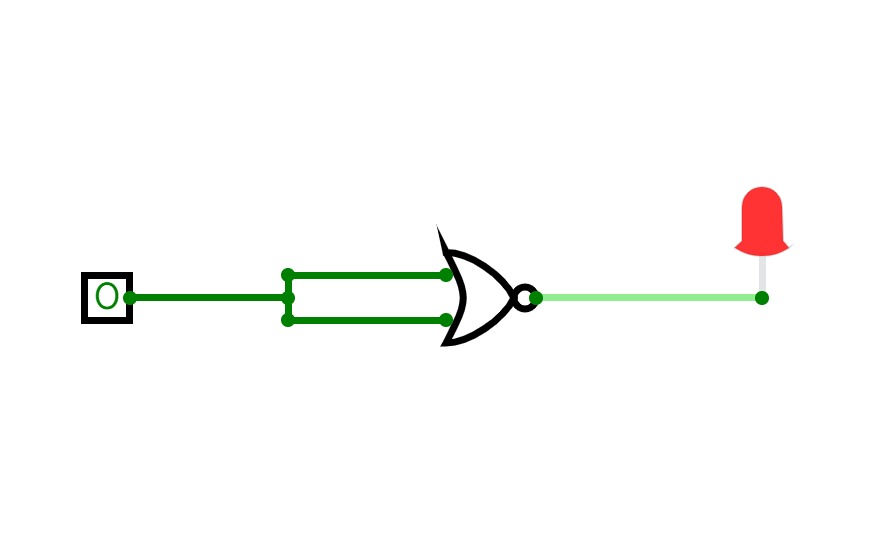

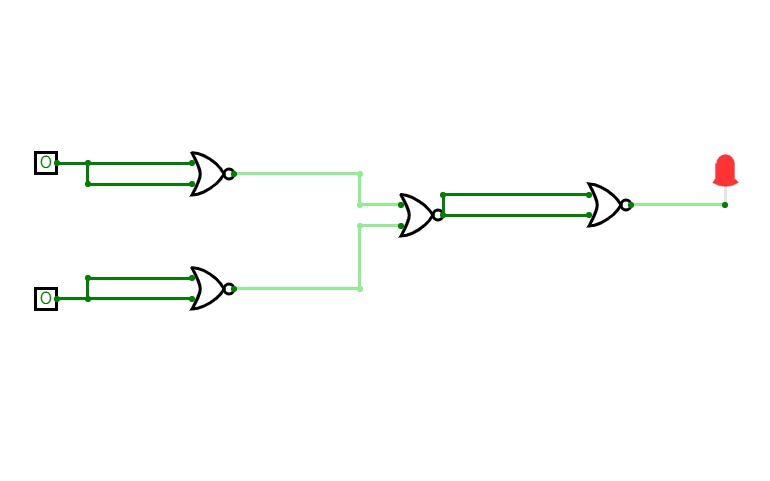

gates using nor gate

gates using nor gate

NAND GATE

NAND GATE

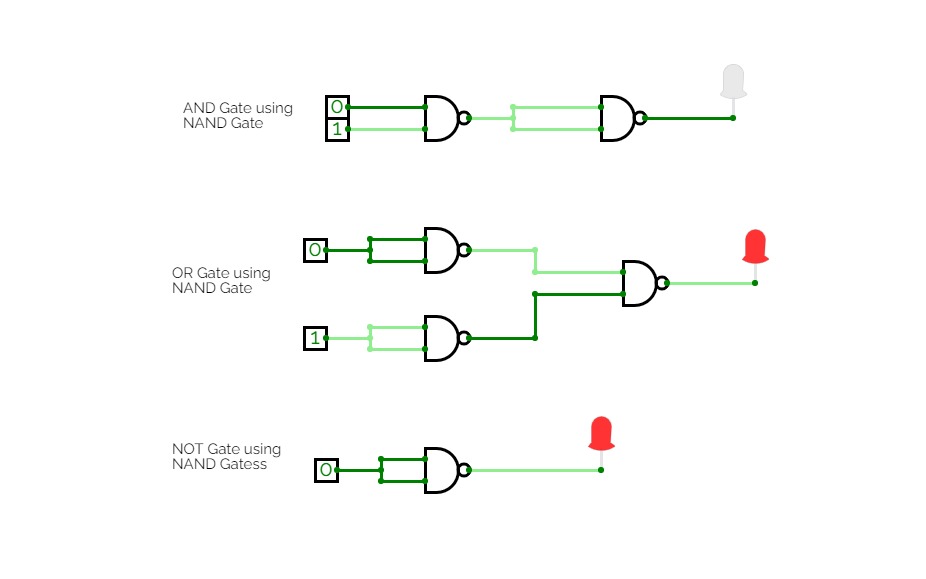

gates using nand gate

gates using nand gate

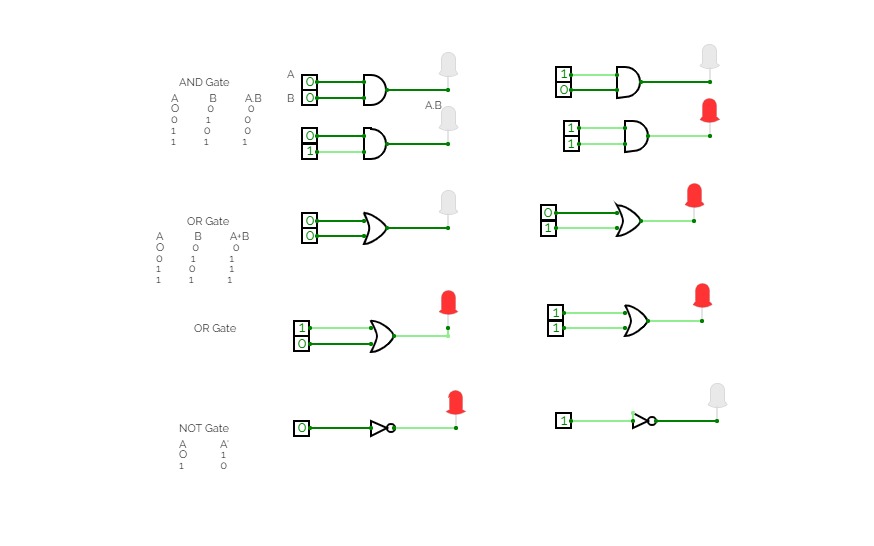

gates

gates

xor/xnor using basic gates

xor/xnor using basic gates

gate1

gate1