Akriti Kumari

Member since: 3 years

Educational Institution: Not Entered

Country: Not Entered

LAB TASK-1 NOR CIRCUIT

LAB TASK-1 NOR CIRCUIT

7 Segment Display

7 Segment Display

4*4 Array Multiplier_oe

4*4 Array Multiplier_oe

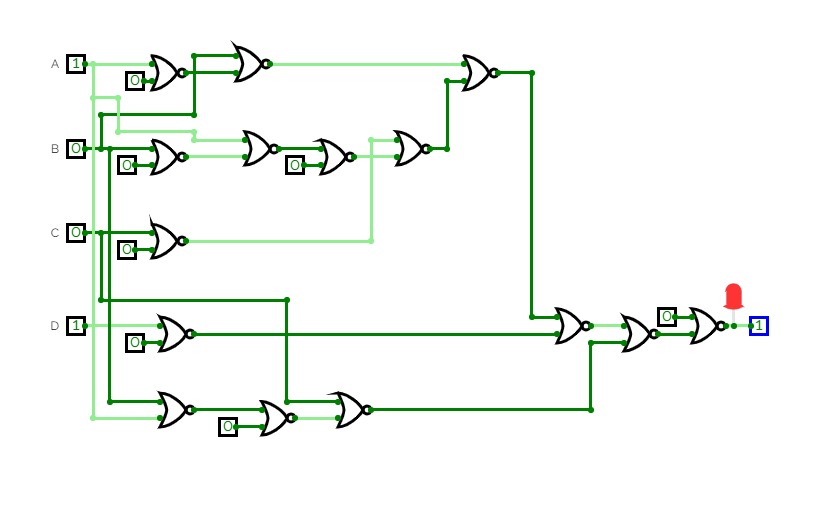

POS

POS

COMMON CATHODE WITH DON'T CARES

COMMON CATHODE WITH DON'T CARES

COMMON ANODE WITH DON'T CARES 16:1 MUX

COMMON ANODE WITH DON'T CARES 16:1 MUX

COMMON ANODE with / without DON'T CARE

COMMON ANODE with / without DON'T CARE

full adder using decoder

full adder using decoder

Multiplication

Multiplication

1 : 16 demultiplexer

1 : 16 demultiplexer

16:1 for F'

16:1 for F'

DLCD TASK3 16:1 MUX

DLCD TASK3 16:1 MUX

8:1 for F'

8:1 for F'

FULL ADDER

FULL ADDER

Q1-SEVEN SEGMENT DECODER TO DISPLAY NAME & REG NO

Q1-SEVEN SEGMENT DECODER TO DISPLAY NAME & REG NO

4:1 Mux using Logic Gates

4:1 Mux using Logic Gates

16:1

16:1

LAB TASK-1

LAB TASK-1

LAB TASK 2

LAB TASK 2

SOP in AND OR INV

SOP in AND OR INV

1-bit comparator

1-bit comparator

Half-Adder

Half-Adder

1*1 Bit Multiplier

1*1 Bit Multiplier

LAB TASK-2 NAND

LAB TASK-2 NAND

2:1 NAND

2:1 NAND

SOP

SOP

16:1 mux using 2:1 mux

16:1 mux using 2:1 mux

active high sop and pos using 4:16

active high sop and pos using 4:16

LAB TASK-2

LAB TASK-2

16:1 mux using 2:1 mux

16:1 mux using 2:1 mux

LAB TASK-2

LAB TASK-2

4*4 Bit Array Multiplier

4*4 Bit Array Multiplier

8:1 for F

8:1 for F

2:1 NOR

2:1 NOR

2:1 NAND

2:1 NAND

Q1-SEVEN SEGMENT DECODER TO DISPLAY NAME & REG NO

Q1-SEVEN SEGMENT DECODER TO DISPLAY NAME & REG NO

INTERNAL CIRCUIT OF 1:2 DEMUX USING TWO INPUT NAND GATE

INTERNAL CIRCUIT OF 1:2 DEMUX USING TWO INPUT NAND GATE

full subtractor using mux

full subtractor using mux

POS(OR AND INV)

POS(OR AND INV)

4:1 Mux using Logic Gates

4:1 Mux using Logic Gates

3:8 DECODER USING 2:4 DECODER

3:8 DECODER USING 2:4 DECODER

1*8 Demultiplexer

1*8 Demultiplexer

Half-Adder

Half-Adder

MAGNITUDE COMPARATOR

MAGNITUDE COMPARATOR

Decoder 7 seg CC

Decoder 7 seg CC

FULL ADDER

FULL ADDER

COMMON CATHODE WITHOUT DON'T CARE

COMMON CATHODE WITHOUT DON'T CARE

4:16 decoder using 2:4 decoders

4:16 decoder using 2:4 decoders

7 segment display with common anode

7 segment display with common anode

2:1 multiplexer

2:1 multiplexer

1:4 Demultiplexer using logic gates

1:4 Demultiplexer using logic gates