Dr.Dhanabal

Member since: 3 years

Educational Institution: Not Entered

Country: Not Entered

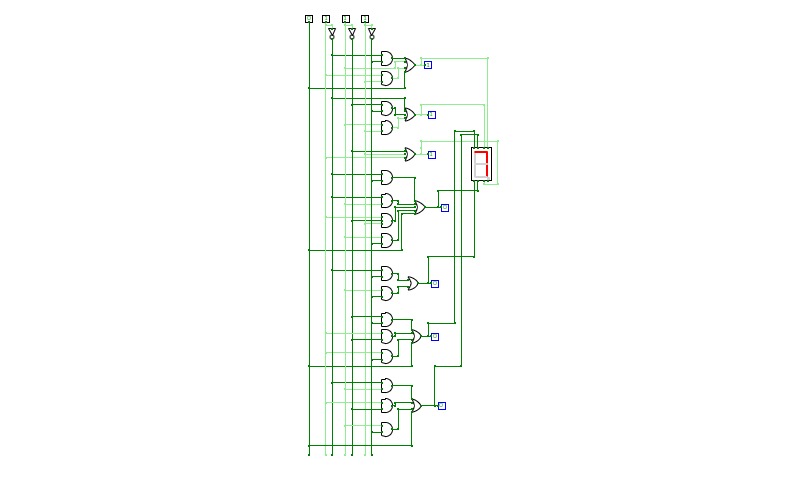

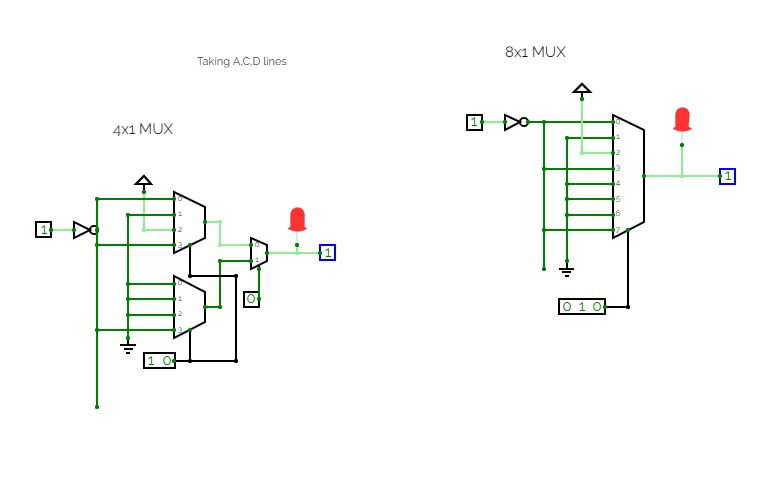

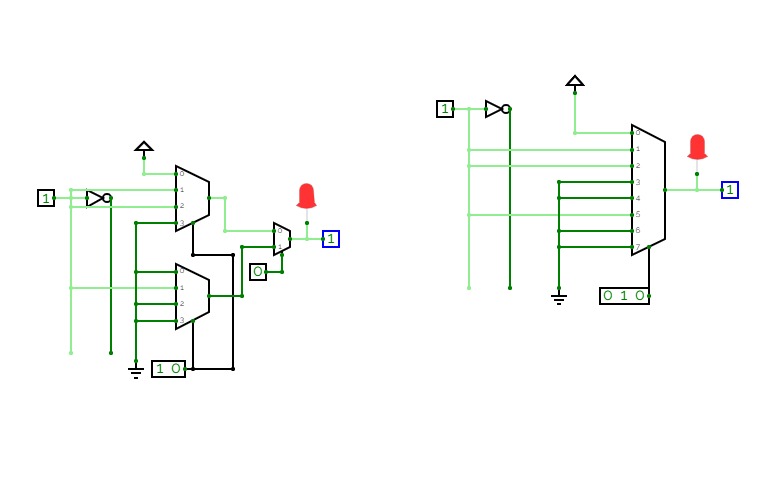

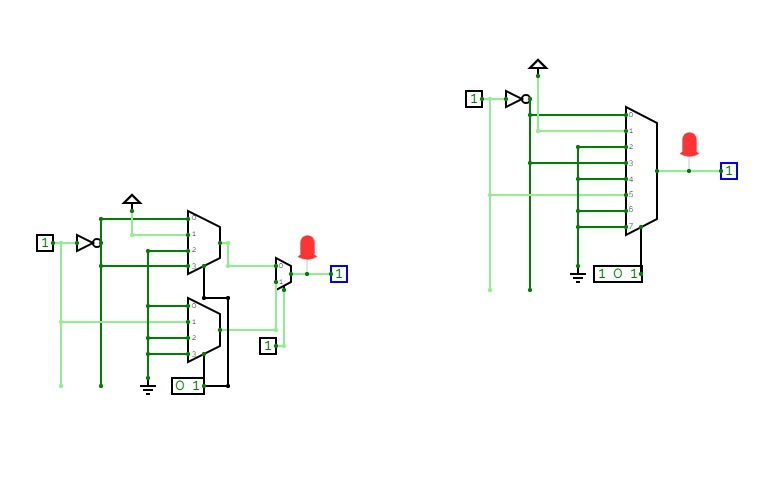

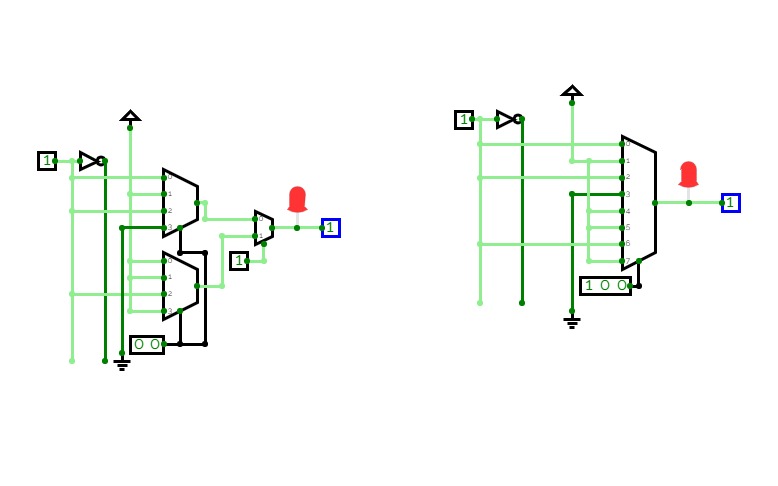

HA DCD

HA DCD

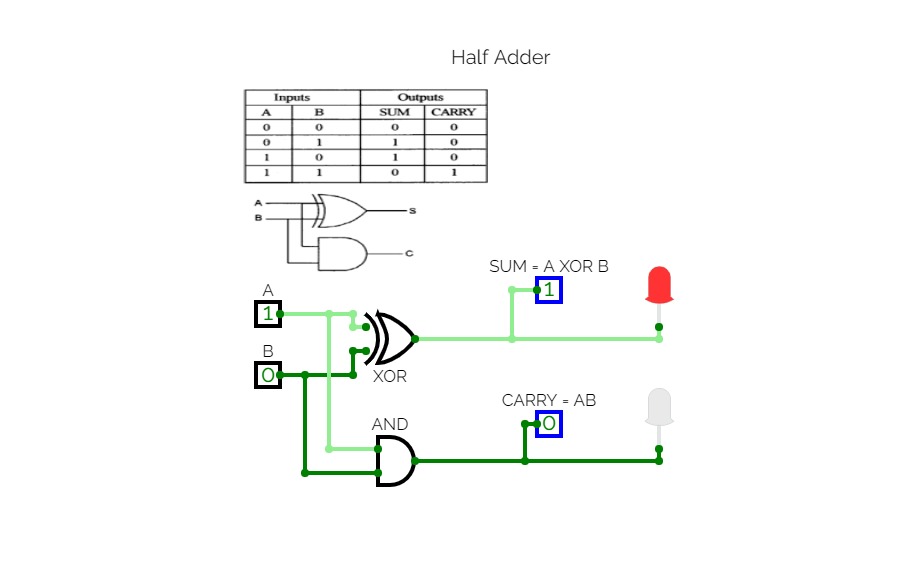

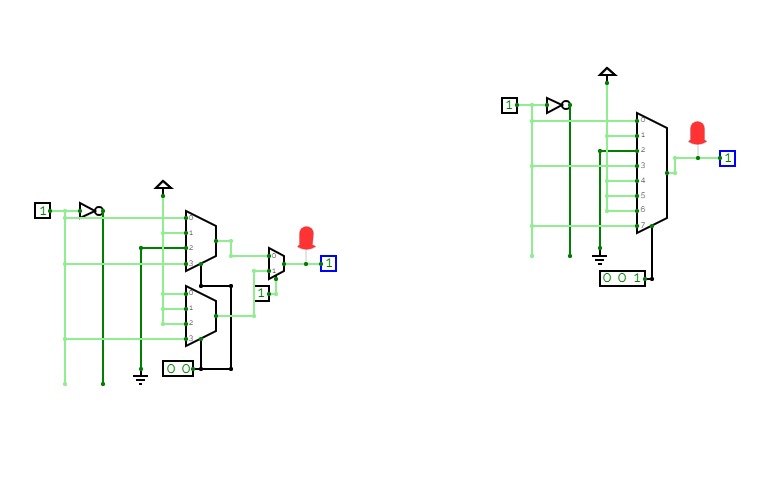

half adder

half adder

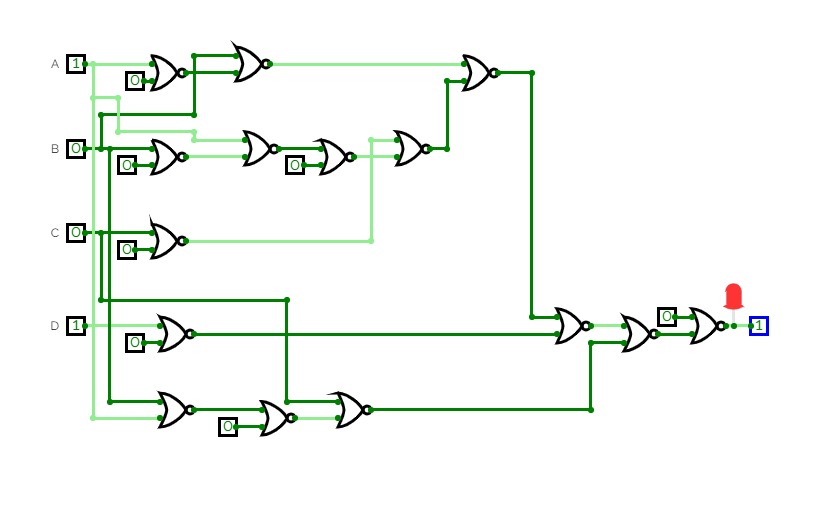

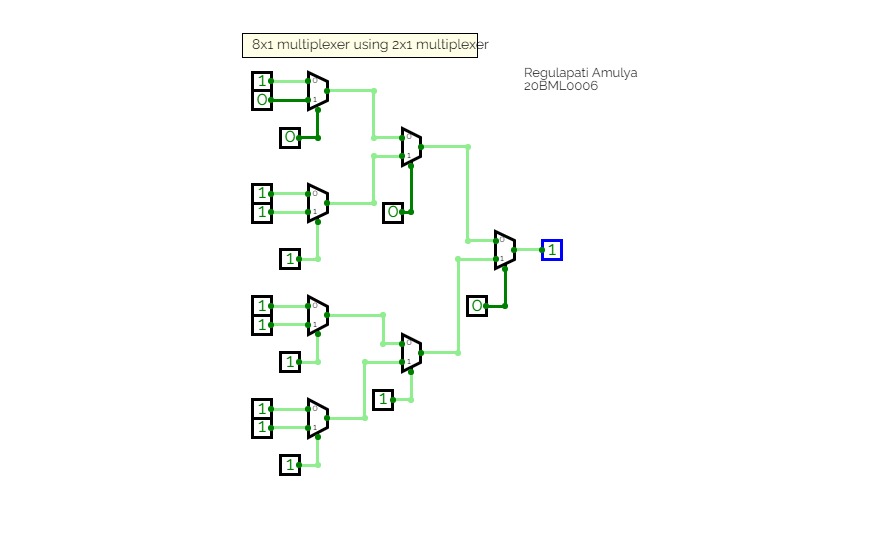

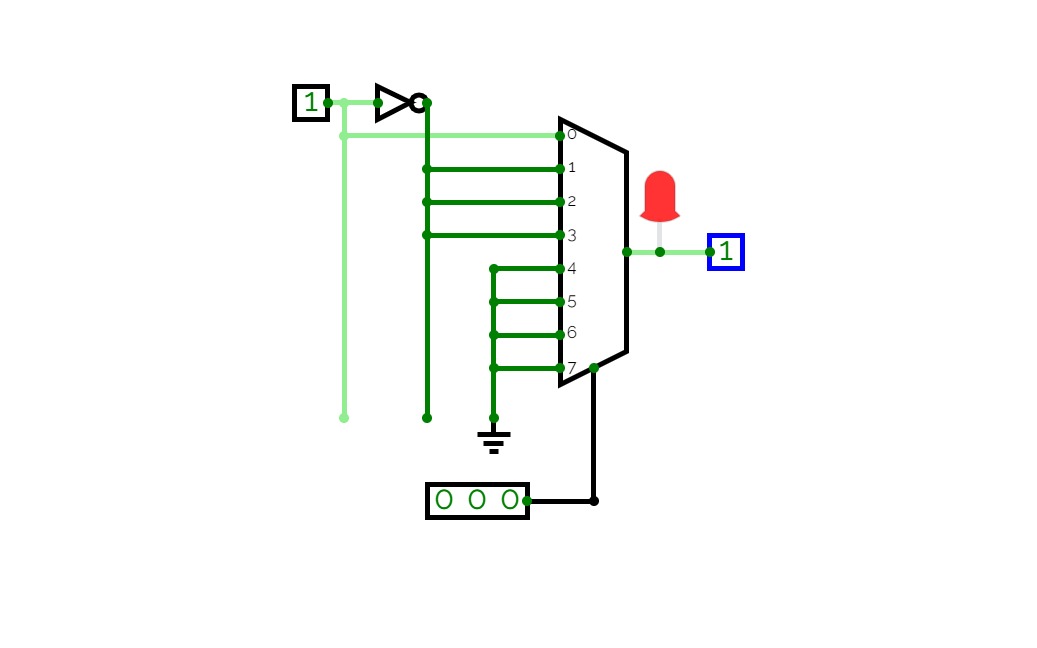

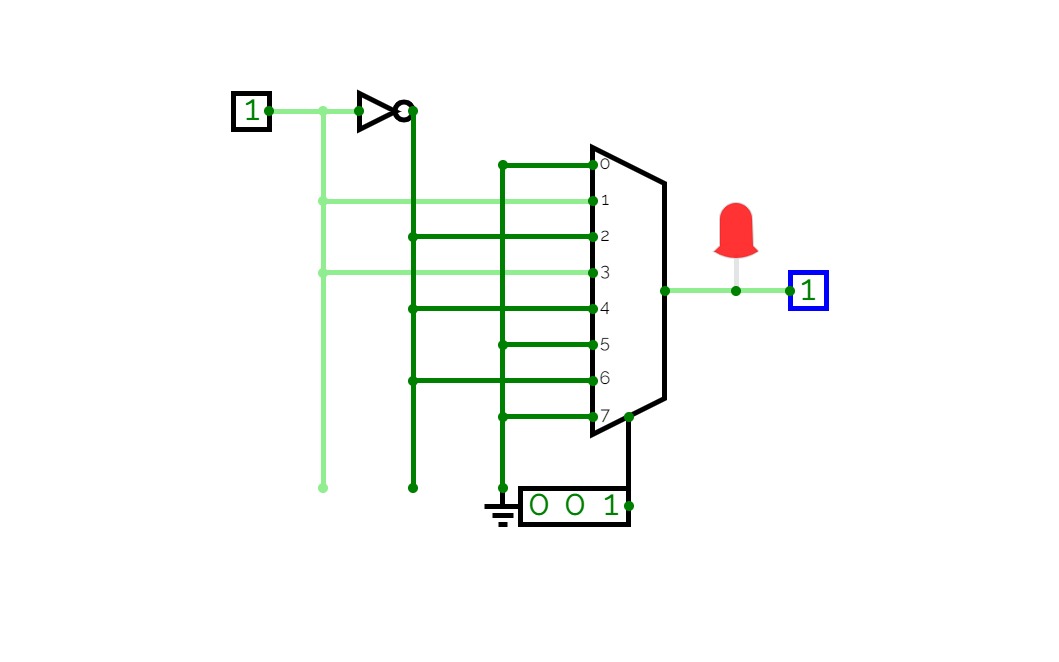

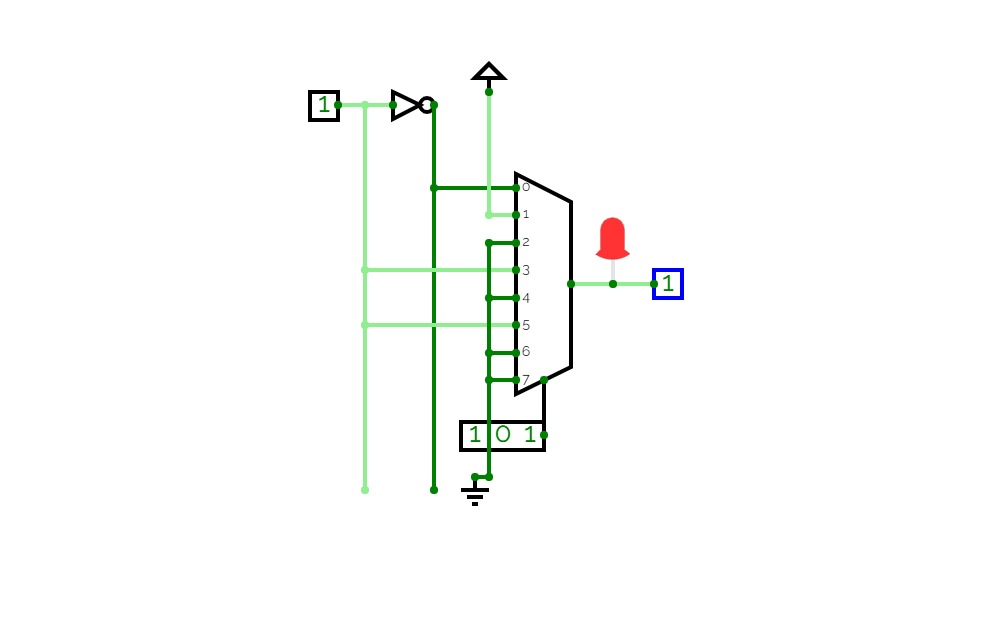

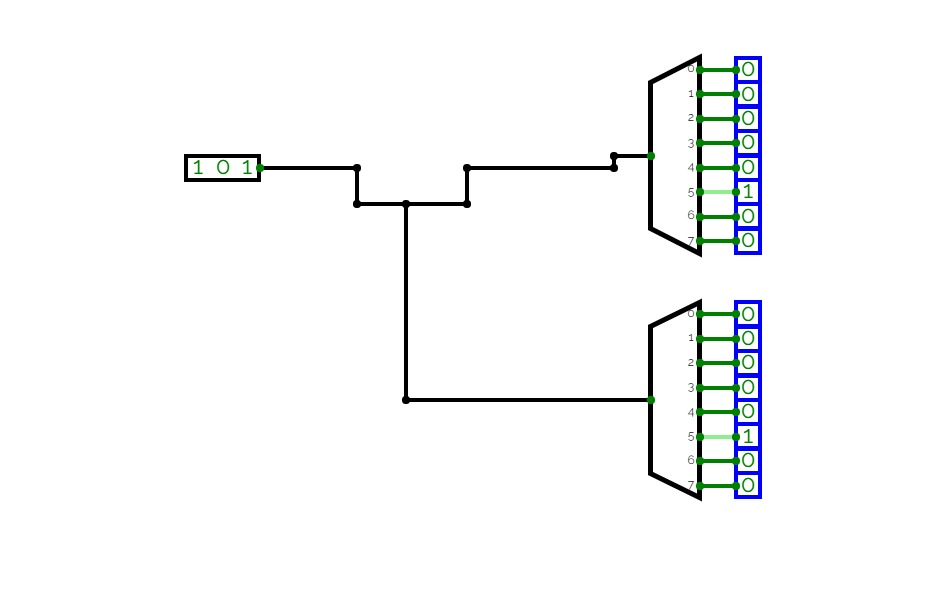

8:1 MUX circuit

8:1 MUX circuit

HA HS 1 bit Multiplier

HA HS 1 bit Multiplier

4:! mux using 2:1 mux

4:! mux using 2:1 mux

NAND logic -NOT,AND,OR,XOR logic gates

NAND logic -NOT,AND,OR,XOR logic gates

logic gate

logic gate

Verification of TT of Logic gates

Verification of TT of Logic gates

TASK III: Verification of logic gates

TASK III: Verification of logic gates

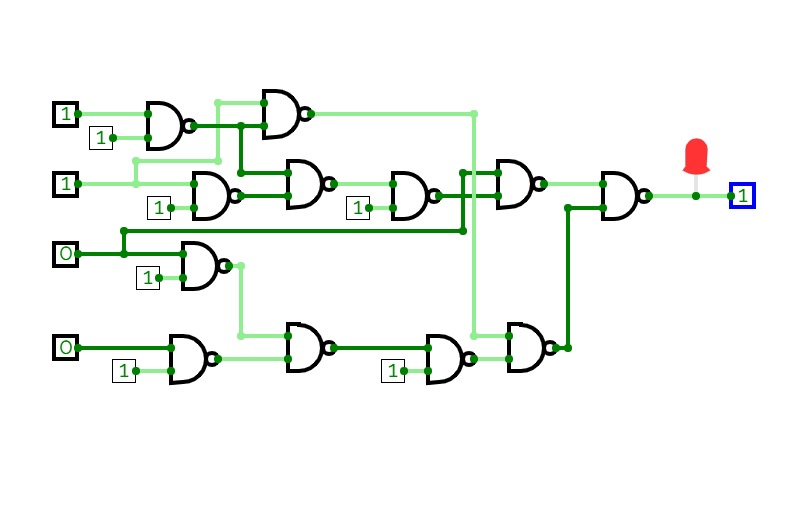

BE using 8:1 MUX (d as i/p, and a,b,c as select lines)

BE using 8:1 MUX (d as i/p, and a,b,c as select lines)

nand nor

nand nor

Dr.Dhanabal doesn't have any favourites.

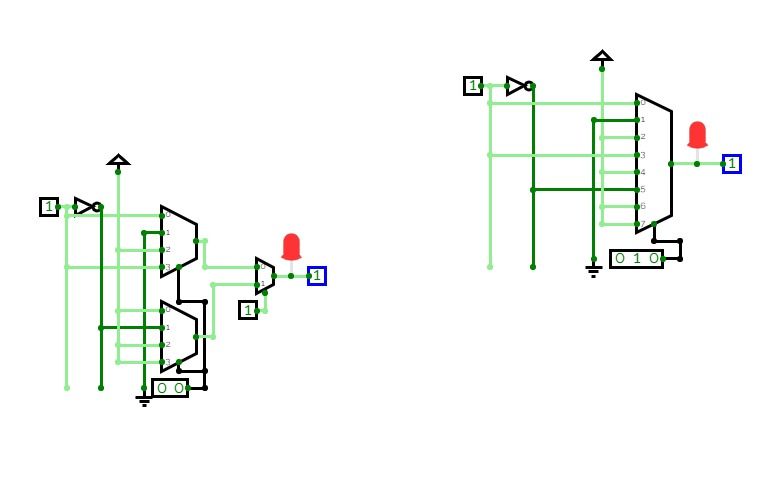

halfadder

halfadder

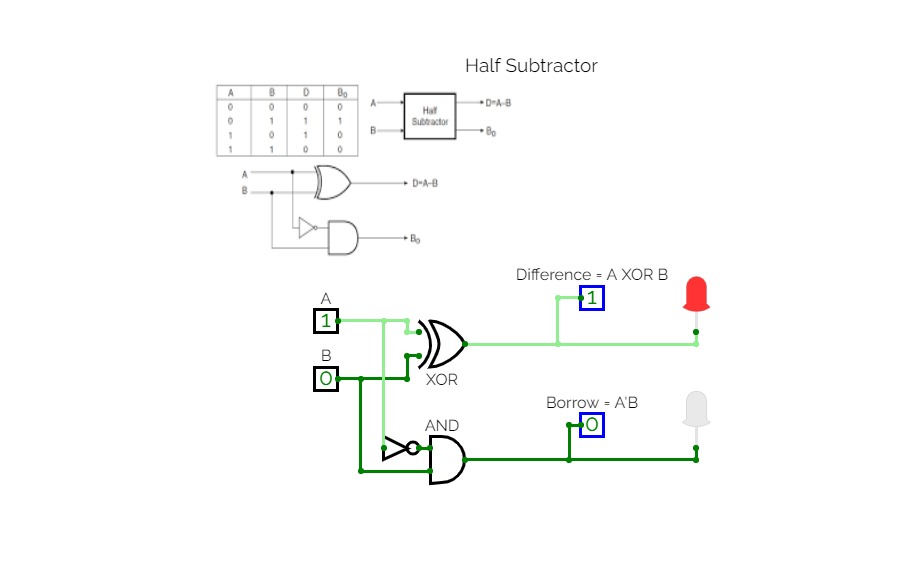

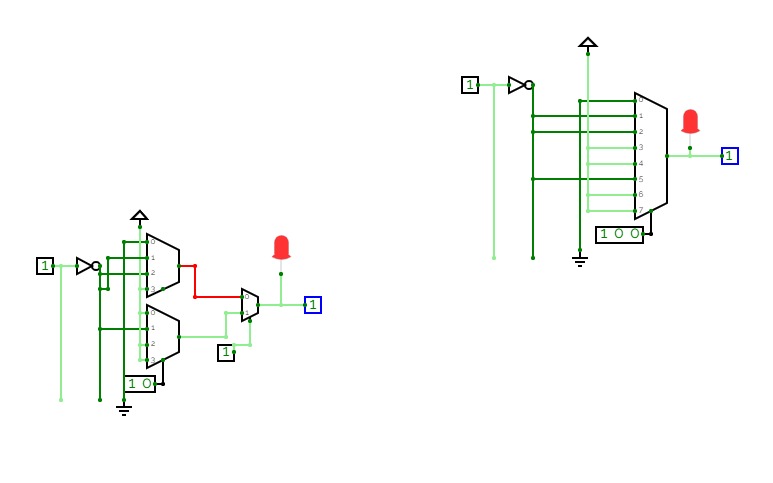

Halfsubtractor

Halfsubtractor

LAB TASK-1

LAB TASK-1

LAB TASK-2 NAND

LAB TASK-2 NAND

LAB TASK 2

LAB TASK 2

LAB TASK-2

LAB TASK-2

LAB TASK-2

LAB TASK-2

LAB TASK-1 NOR CIRCUIT

LAB TASK-1 NOR CIRCUIT

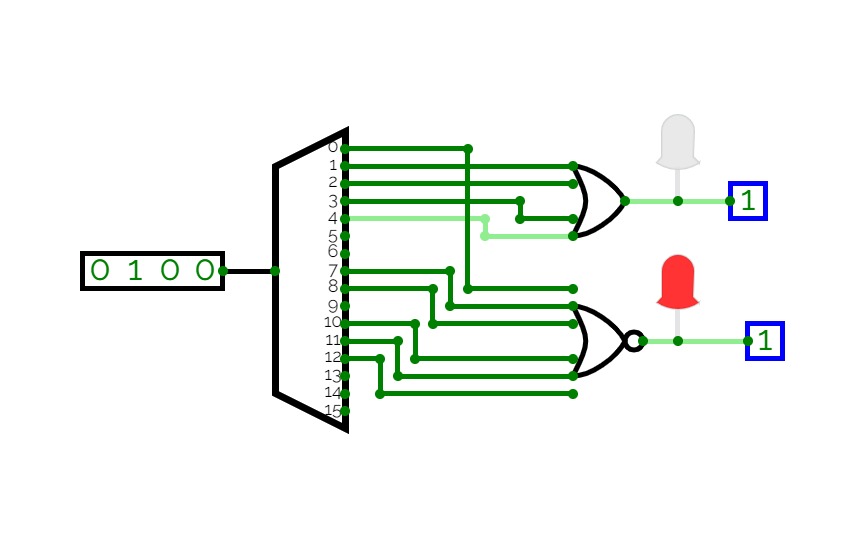

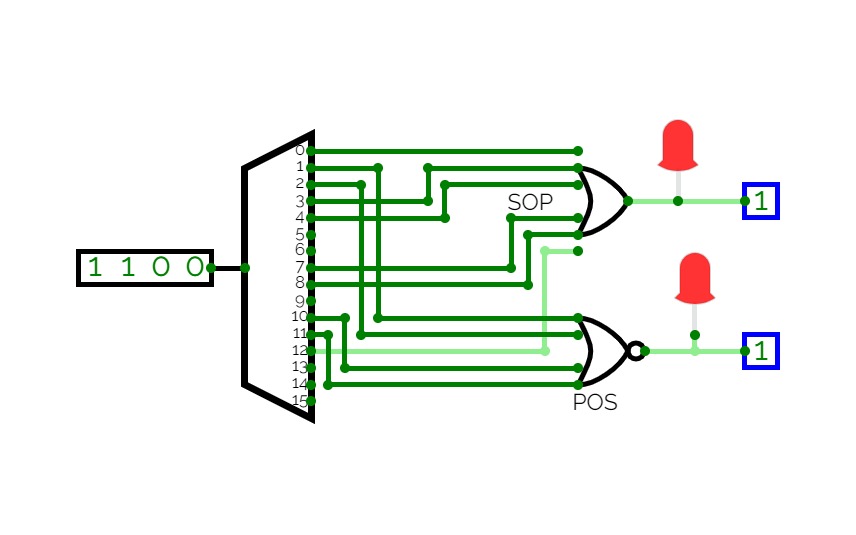

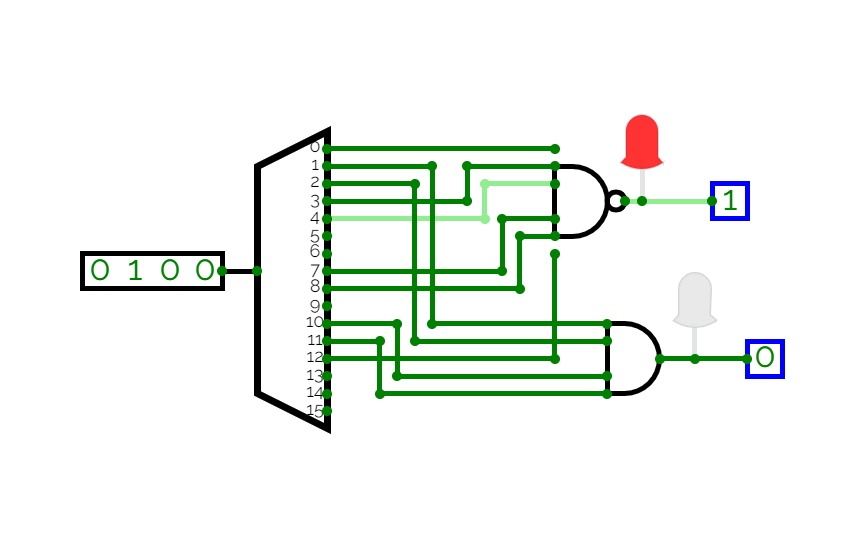

SOP in AND OR INV

SOP in AND OR INV

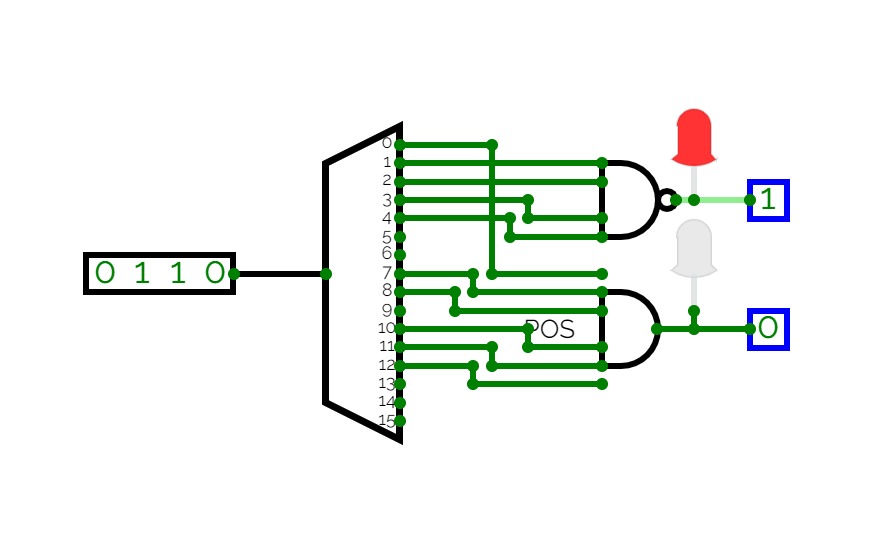

POS(OR AND INV)

POS(OR AND INV)

dcd_task3i

dcd_task3i

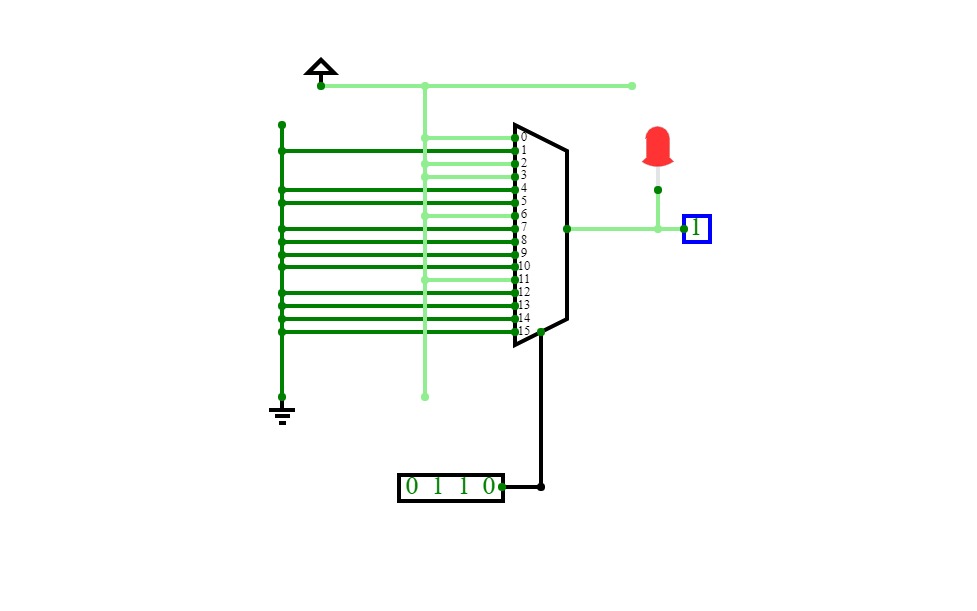

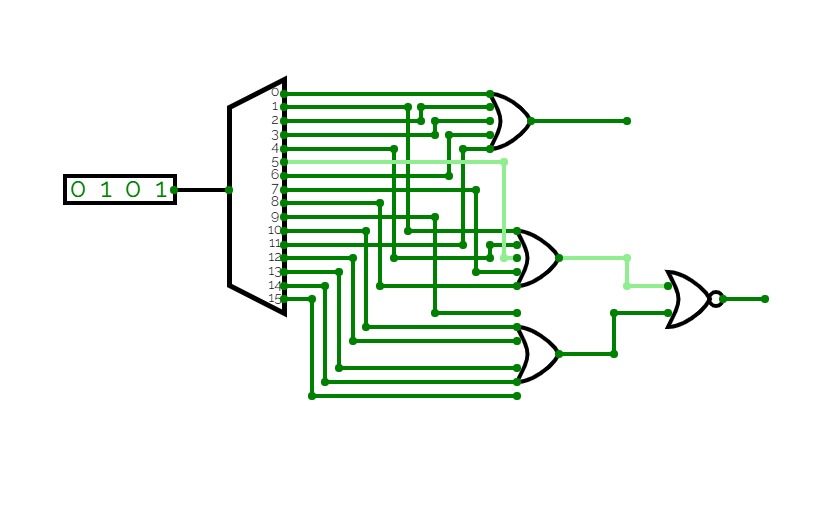

16:1 FMUX

16:1 FMUX

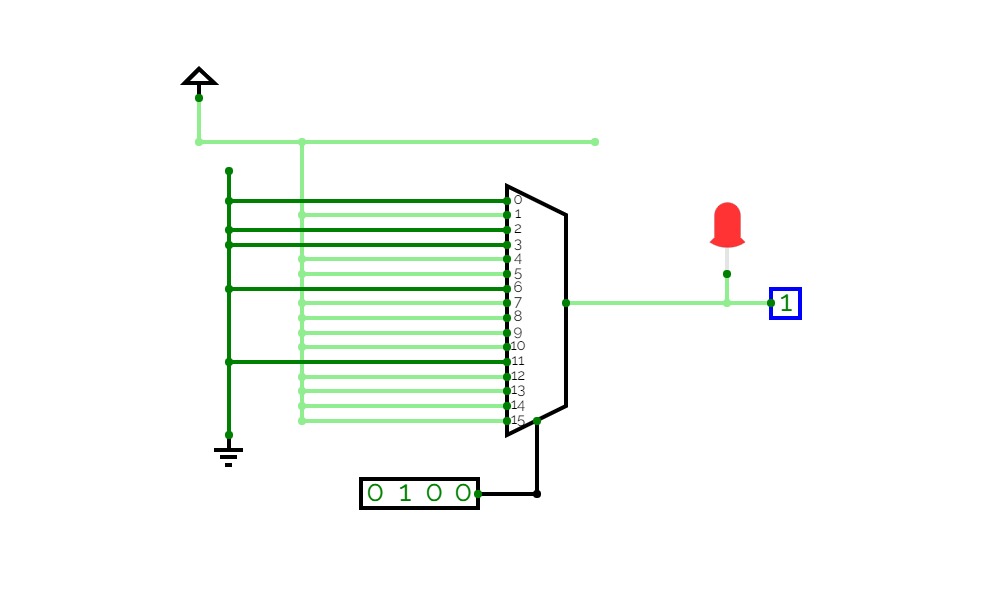

16:1F'MUX

16:1F'MUX

8x1AinMUX

8x1AinMUX

8x1FMUX

8x1FMUX

8x1FCMUX

8x1FCMUX

8x1FDMUX

8x1FDMUX

8x1FdAMUX

8x1FdAMUX

8x1FdBMUX

8x1FdBMUX

8x1FdCMUX

8x1FdCMUX

8x1FdDMUX

8x1FdDMUX

16x1CCMUX

16x1CCMUX

8x1CCXMUX

8x1CCXMUX

8x1CCYMUX

8x1CCYMUX

8x1CCZMUX

8x1CCZMUX

Decoder1

Decoder1

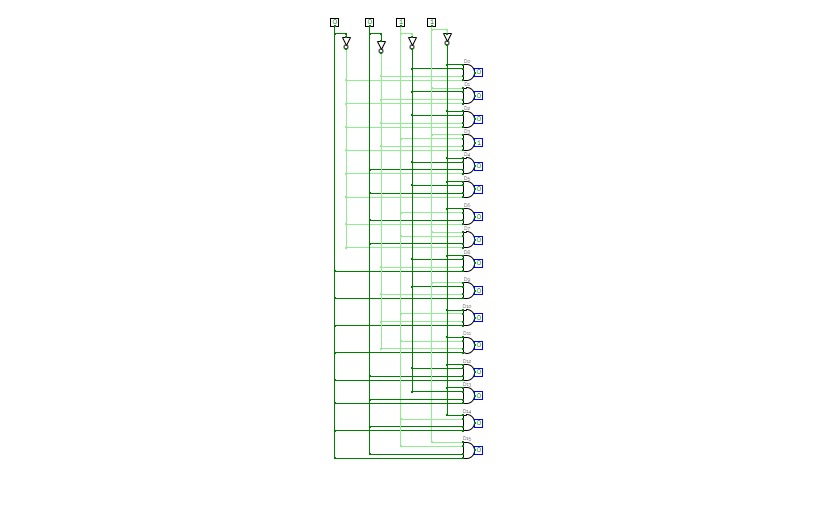

4X16DECODER

4X16DECODER

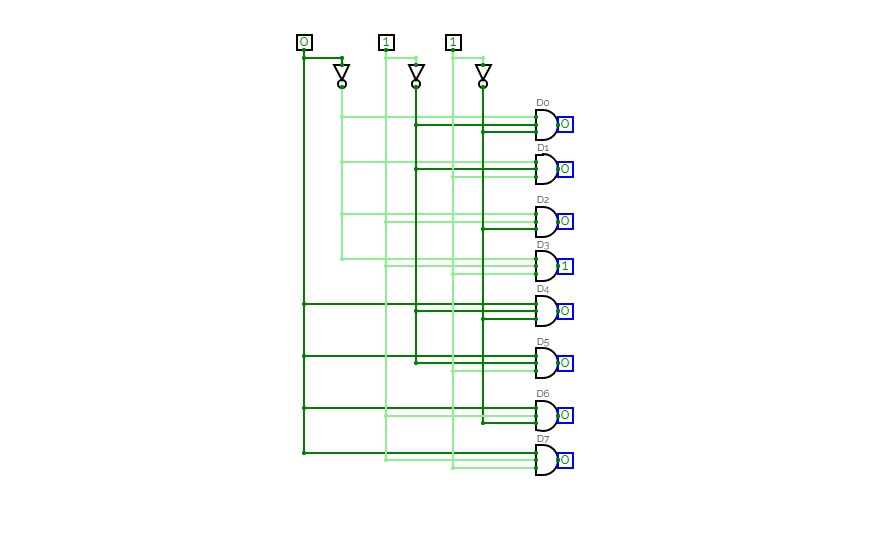

3X8DECODER

3X8DECODER

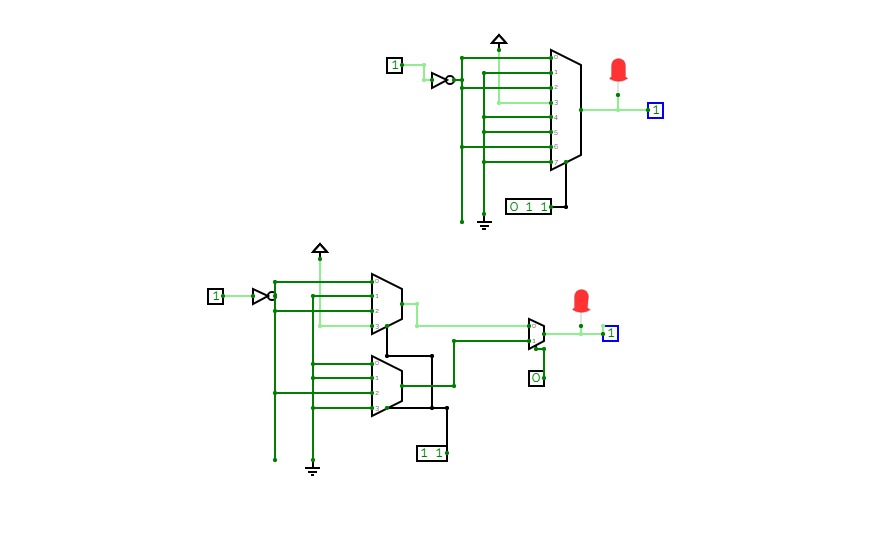

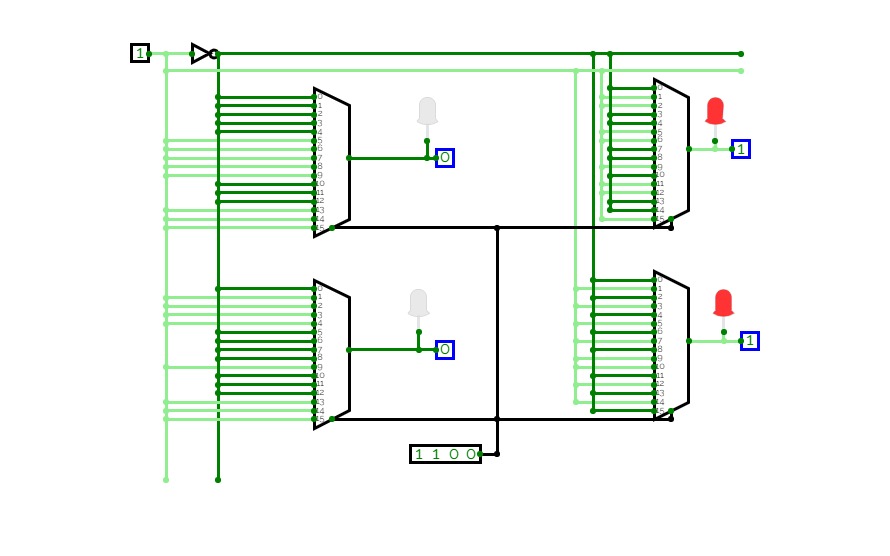

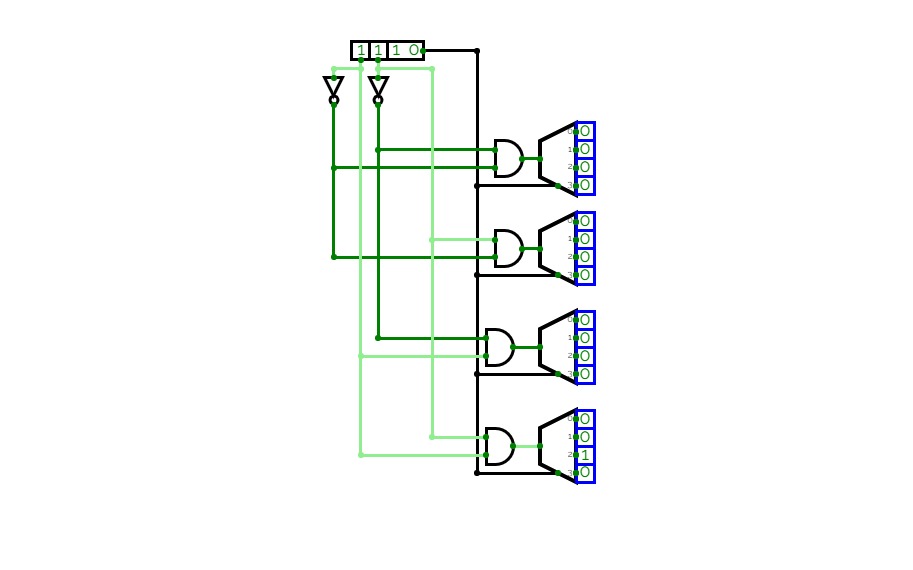

16:1 mux using 2:1 mux

16:1 mux using 2:1 mux

4x16us2x8Decoder

4x16us2x8Decoder

2:1 NAND

2:1 NAND

2x4DecoderNAND

2x4DecoderNAND

2:1 NOR

2:1 NOR

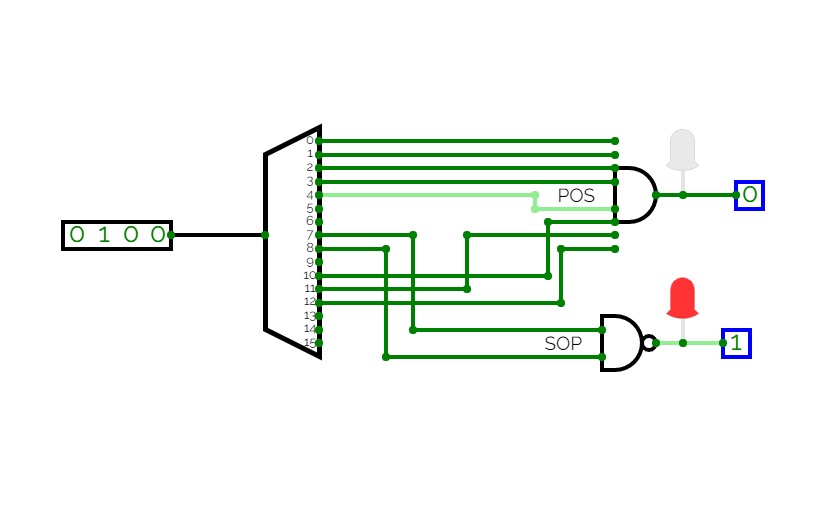

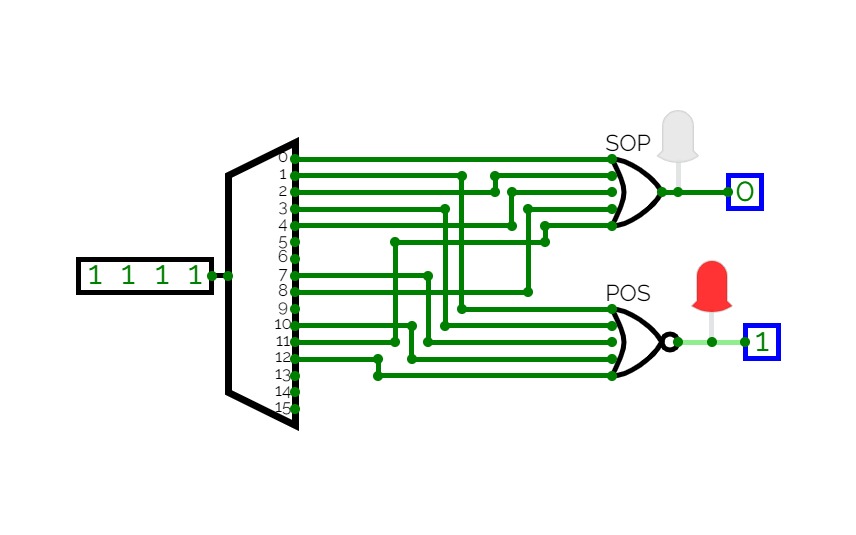

SOP

SOP

POS

POS

AHRN4x16Decoder

AHRN4x16Decoder

ALRN4x16Decoder

ALRN4x16Decoder

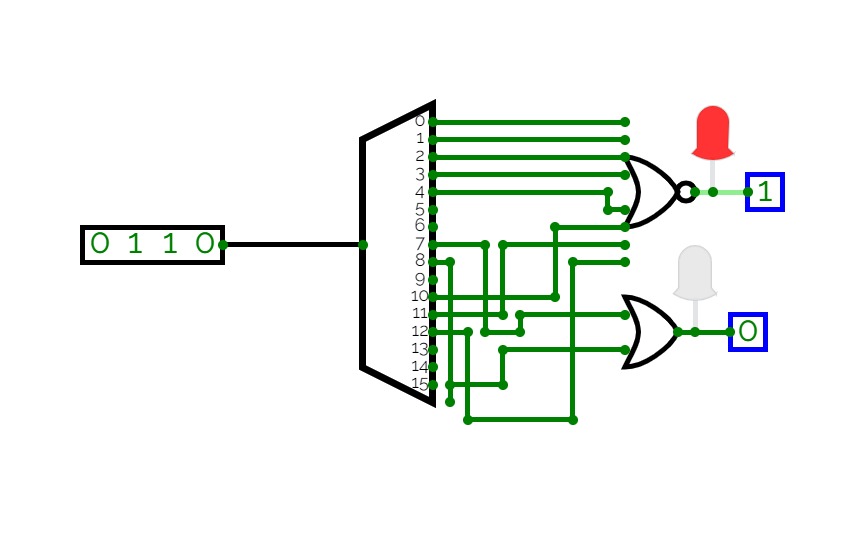

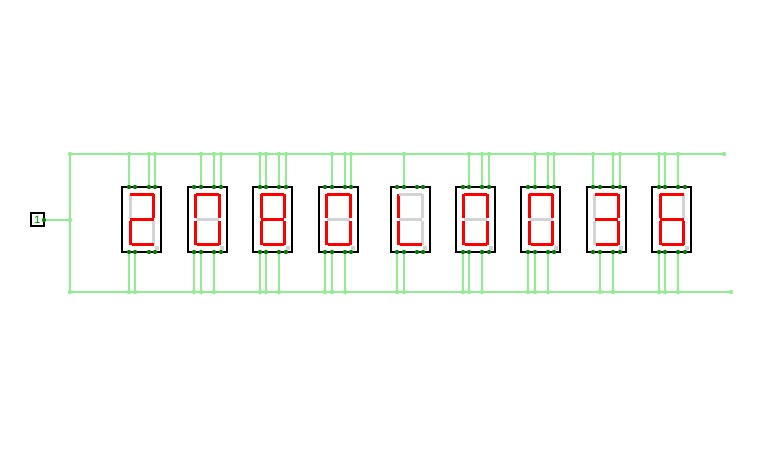

16:1

16:1

16:1 for F'

16:1 for F'

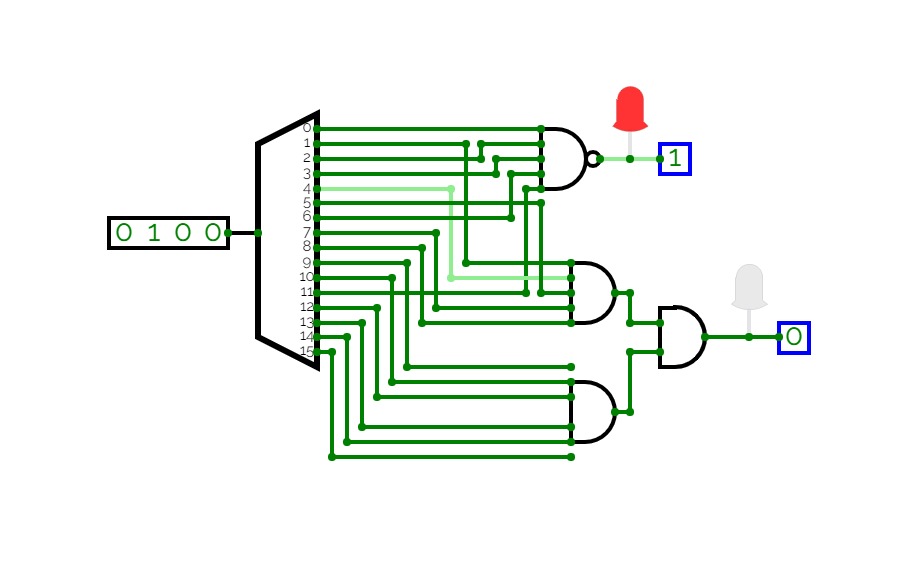

8:1 for F

8:1 for F

8:1 for F'

8:1 for F'

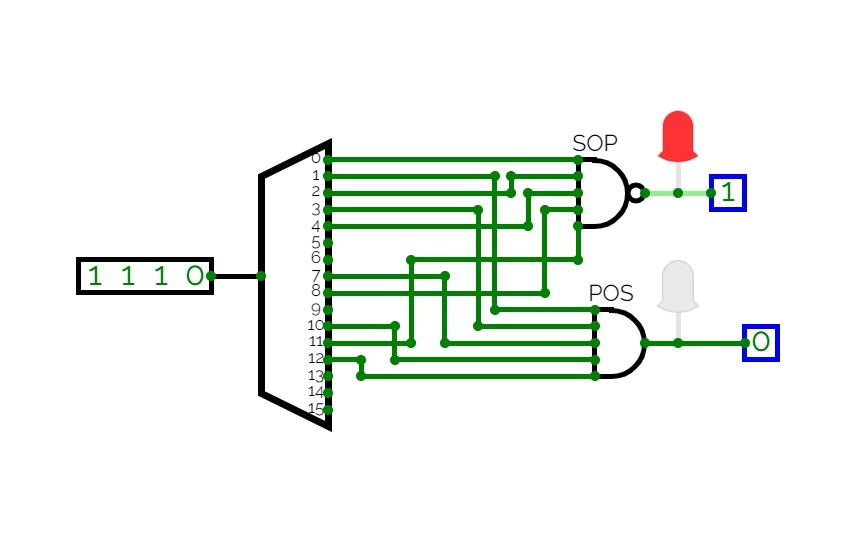

active high sop and pos using 4:16

active high sop and pos using 4:16

AHCC4X16DECODER

AHCC4X16DECODER

ALCCW4X16DECODER

ALCCW4X16DECODER

AHXCC4x16Decoder

AHXCC4x16Decoder

ALXCC4x16Decoder

ALXCC4x16Decoder

AHYCC4x16Decoder

AHYCC4x16Decoder

ALYCC4x16Decoder

ALYCC4x16Decoder

AHZCC4x16Decoder

AHZCC4x16Decoder

ALZCC4x16Decoder

ALZCC4x16Decoder

CCWXYZ4x16Decoder

CCWXYZ4x16Decoder

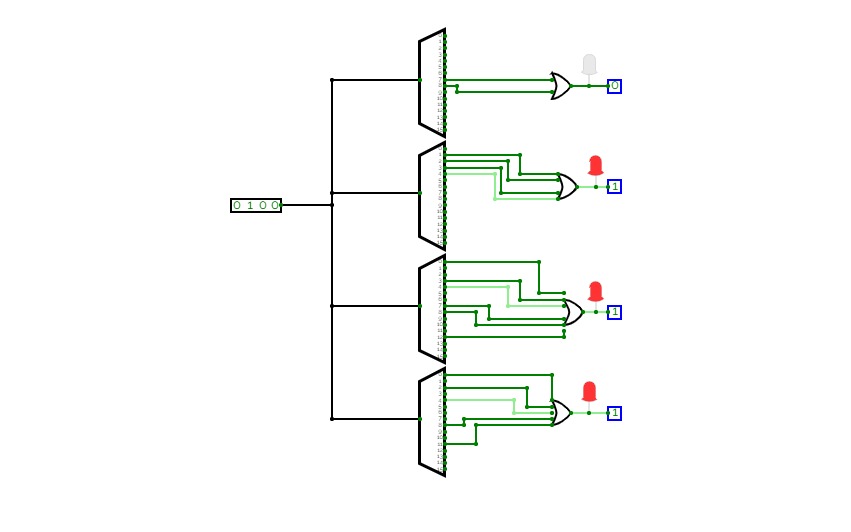

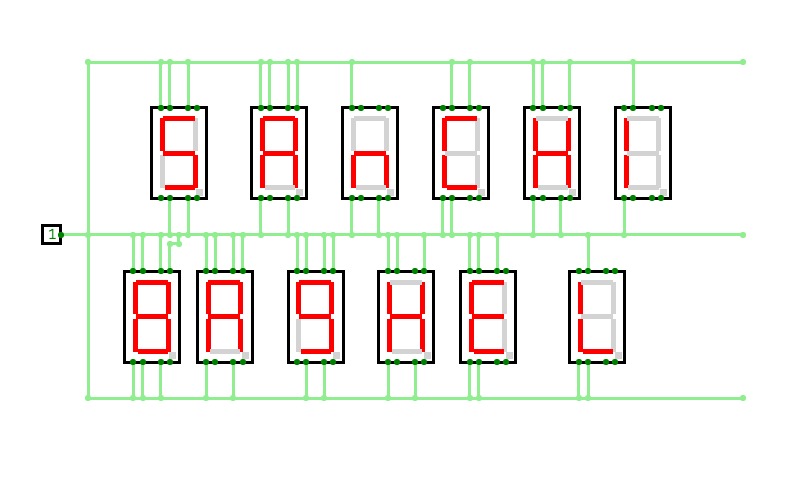

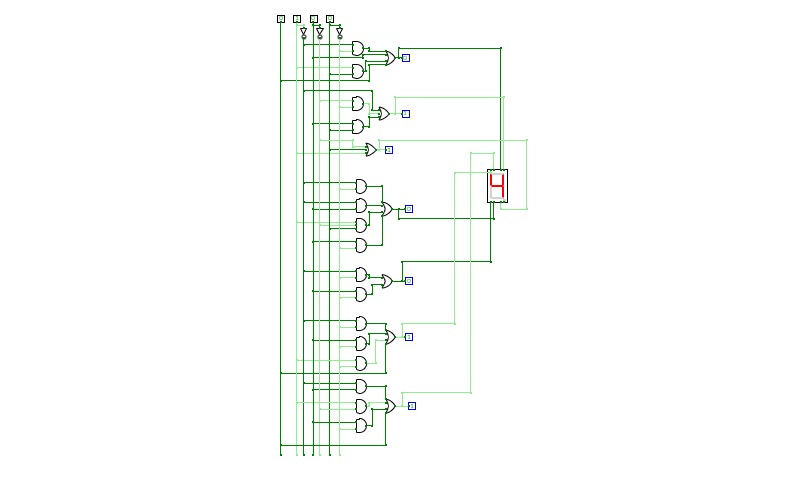

7-Segment Decoder REG

7-Segment Decoder REG

DCD7SEGNAME

DCD7SEGNAME

CathodeSegment7

CathodeSegment7

AnodeSegment7

AnodeSegment7